Fターム[5F004EA06]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380) | SiO2膜 (416)

Fターム[5F004EA06]に分類される特許

21 - 40 / 416

ドライエッチング方法及びドライエッチング装置

【課題】特殊な装置を用いることなく、好適なエッチングレートを維持しつつ、エッチング形状の異方性を向上することができるドライエッチング方法及びドライエッチング装置を提供する。

【解決手段】SF6からなるガスに、酸素を添加するとともに、SF6に対する流量比を0.22以上0.67以下に調整してSixFyで表されるフッ化ケイ素ガスを添加したエッチングガスをプラズマ化して、シリコン層をエッチングする。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

プラズマエッチング方法

【課題】マスクをプラズマから保護することができ、形成する穴部の側壁を基板の表面に対して垂直にできるプラズマエッチング方法を提供する。

【解決手段】上方にパターニングされたシリコン酸化膜が形成されてなる被処理基板におけるシリコン層を第1の処理ガスによりエッチングして穴部を形成するプラズマエッチング方法において、一酸化炭素ガスを含む第2の処理ガスによりシリコン酸化膜の表面に保護膜を堆積させる第1の堆積ステップS11と、第1の処理ガスによりシリコン層をエッチングする第1のエッチングステップS12と、穴部の側壁に第2の処理ガスにより保護膜を堆積させる第2の堆積ステップS13と、第1の処理ガスによりシリコン層を更にエッチングする第2のエッチングステップS14とを有し、第2の堆積ステップS13と第2のエッチングステップS14とを少なくとも2回ずつ交互に繰り返す。

(もっと読む)

プラズマ処理方法

【課題】本発明は、堆積性のガスを用いたプラズマ処理において、被処理体の処理枚数の増加による異物を抑制できるプラズマ処理方法を提供する。

【解決手段】本発明は、処理室内に導入された堆積性ガスからプラズマを生成し、当該処理室内に設けられた試料台上に載置される被処理体を、高周波電力を印加した状態で前記プラズマに曝すことにより前記被処理体のエッチングを行うプラズマ処理方法において、前記被処理体を前記プラズマに曝す第一の期間と、前記被処理体を前記プラズマに曝し当該第一の期間よりも前記被処理体に対するエッチングレートの低い第二の期間とを繰り返すことにより、前記処理室内壁面への堆積膜がアモルファスになるエッチング条件で前記被処理体をエッチングすることを特徴とする。

(もっと読む)

発光素子

【課題】光抽出構造が形成されることで、発光効率及び信頼性を向上できる発光素子を提供する。

【解決手段】本発明の発光素子は、金属又は半導体からなる支持層;支持層上に位置する第1の電極;第1の電極上に位置し、発光層を含む多層構造の半導体層;及び半導体層上に配置され、少なくとも一つのホール又は柱形状の単位構造で形成される光抽出構造;を含む。光抽出構造はランダムに配置され、光抽出構造の高さは、nを光抽出構造が形成された物質の屈折率とし、λを発光層の中心波長とした場合にλ/2n〜3000ナノメートルであり、光抽出構造の周期又は隣接する単位構造の各中心間の平均距離は400〜3000ナノメートルであり、光抽出構造の単位構造はホール又は柱形状であり、単位構造の内側表面の半径と外側表面の半径とが互いに異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、この配線20を窒素プラズマに曝露する。これにより、既存の側壁保護膜32にAlNが合わさって側壁保護膜32を分厚くすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、この配線20の表面を覆うように、SiN膜38を形成する。これにより、既存の側壁保護膜36にSiN膜38が合わさって側壁保護膜32が形成される。

(もっと読む)

プラズマエッチング方法

【課題】基板の表面をエッチングして穴部を形成する際に、穴部の側壁を基板の表面に対して垂直にできるとともに、高速にシリコン層をエッチングできるプラズマエッチング方法を提供する。

【解決手段】シリコン層の上方にレジスト層が形成されてなる被処理基板が設置されている処理容器内に、酸素ガスとフッ化硫黄ガスとを含んだエッチングガスを所定の流量で供給し、供給したエッチングガスをプラズマ化したプラズマにより、シリコン層をエッチングするプラズマエッチング方法において、フッ化硫黄ガスの流量に対する酸素ガスの流量の流量比を第1の流量比とした状態でエッチングする第1のステップS1と、流量比が第1の流量比から第1の流量比よりも小さい第2の流量比になるように、酸素ガスの流量を減少させながらエッチングする第2のステップS2と、流量比を第2の流量比とした状態でエッチングする第3のステップS3とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】SiCからなる第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、第2層間膜17をエッチングすることにより低段部28を形成する。このとき、第2層間膜17(SiC)からCを解離させ、その解離したCを含む反応生成物を側壁保護膜32に定着させることによって、側壁保護膜32を厚くする。

(もっと読む)

貼り合せ構造体及び貼り合せ構造体の製造方法、並びに被処理基板の構造体の製造方法

【課題】被処理基板における凹凸形状を備えた面と下地基板の表面とを仮接着した後に減圧下において処理する際の、加工精度、処理効率、及び/又は処理の安全性を高める。

【解決手段】本発明の1つの貼り合せ構造体40の製造方法は、凹部42A及び凸部42Bが形成された第1表面を備える被処理基板41の第1表面42上に、25℃における粘度が0.02Pa・s以上0.1Pa・s以下である溶液状仮接着材を供給する溶液状仮接着材供給工程と、その溶液状仮接着材を加熱することにより、第1表面42の凸部42Bを10μm超20μm以下の厚みの仮接着材46Bによって覆う仮接着材形成工程と、その仮接着材46Bを介して、第1表面42と平板状の下地基板48とを一時的に貼り合わせる貼り合せ工程とを含む。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】不純物領域の自己整合的な形成を精度よく行うことができる、炭化珪素半導体装置の製造方法を提供する。

【解決手段】マスク層31の開口部OPを介して炭化珪素基板90上に第1導電型不純物が注入される。第1および第2の材料のそれぞれから作られた第1および第2の膜32、33が成膜される。異方性エッチング中に第1の材料のエッチングが生じたことが検知され、異方性エッチングが停止される。第1および第2の膜32、33によって狭められた開口部OPを介して、炭化珪素基板90上に第2導電型不純物が注入される。

(もっと読む)

半導体レーザ素子の製造方法

【課題】リッジ部を形成するためのエッチングの際にGaAsキャップ層の側壁にサイドエッチングが進行することを防止できる半導体レーザ素子の製造方法を提供する。

【解決手段】本発明の半導体レーザ素子の製造方法は、半導体基板2上にnクラッド層3と、活性層4と、第1pクラッド層5と、エッチングストップ層6と、第2pクラッド層7と、キャップ層9とを順次積層して形成する工程と、キャップ層9の一部を除去した開口部10AにZnO層11を形成して窓領域を形成する工程と、開口部10Aからキャップ層9上にかけてストライプ状の絶縁膜マスクパターン16を形成し、絶縁膜マスクパターン16から露出したキャップ層9をエッチング除去する工程と、絶縁膜マスクパターン16から露出しているキャップ層9の側壁を酸化する工程と、エッチングストップ層6に達するまでエッチングを行ってリッジを形成する工程とを含むことを特徴とする。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

アモルファスカーボン膜の成膜方法、それを用いた半導体装置の製造方法、およびコンピュータ読取可能な記憶媒体

【課題】耐プラズマ性が高く、低温成膜が可能なアモルファスカーボン膜の成膜方法、およびそのようなアモルファスカーボン膜の成膜方法を適用した、半導体装置の製造方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器内に炭素と水素と酸素とを含む処理ガスを供給し、処理容器内の基板を加熱して処理ガスを分解して、基板上にアモルファスカーボン膜を堆積する。この方法を半導体製造装置のエッチングマスクの形成に適用して半導体装置を得る。

(もっと読む)

半導体装置の製造方法

【課題】水素を用いた熱分解において、水素濃度を規定してエッチング速度を制御することで、半導体装置の製造方法の加工精度を向上させる。

【解決手段】半導体装置1の製造方法は、基板10に窒化物半導体で形成された第1層(障壁層25)および第2層(キャップ層26)を順に堆積させる堆積工程と、窒素および水素の混合雰囲気中で加熱して第2層をエッチングする熱エッチング工程とを備える。熱エッチング工程では、水素濃度が1%以上20%以下であることが望ましい。

(もっと読む)

エッチングマスクスタックを用いたマルチマスクプロセス

【課題】基板の上のエッチング層内にエッチング特徴を形成するための方法が提供される。

【解決手段】エッチングマスクスタックが、エッチング層の上に形成される。第1のマスクが、エッチングマスクスタックの上に形成される。第1のマスクによって定められる間隔の幅を低減させる側壁層が、第1のマスクの上に形成される。側壁層を通して、第1組の特徴が、エッチングマスクスタック内へとエッチングされる。マスクおよび側壁層は、除去される。追加の特徴のステップが実施される。該ステップは、追加のマスクをエッチングマスクスタックの上に形成することと、側壁層を追加のマスクの上に形成することと、第2組の特徴を少なくとも部分的にエッチングマスクスタック内へとエッチングすることと、を含む。エッチングマスクスタック内の第1組の特徴および第2組の特徴を通して、複数の特徴がエッチング層内にエッチングされる。

(もっと読む)

半導体素子の作製方法

【課題】半導体からのV族原子の脱離を抑制しつつ同一面内でエッチング深さが異なる形状を簡易に加工することができる半導体素子の作製方法を提供する。

【解決手段】酸素プラズマの所定の濃度に対して、開口部幅の異なる領域毎に、半導体表面にて酸素プラズマによりポリマーの生成を抑制しつつ半導体表面のエッチングが進行する状態のみが発現するように前記開口部幅1905が設定された開口部1901を有するマスク1900を半導体表面に形成する第1の工程と、マスク1900が形成された前記半導体表面に前記炭化水素系プラズマおよび前記酸素プラズマを照射し、前記酸素プラズマを前記マスクの開口部幅方向にて前記開口部に拡散させることによりポリマーの生成を抑制するとともにエッチングに寄与する炭化水素系プラズマの濃度を制御する第2の工程を有するようにした。

(もっと読む)

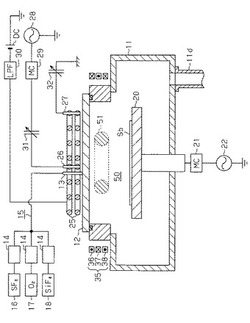

シリコン基板のエッチング方法、及びシリコン基板のエッチング装置

【課題】シリコン基板に形成される凹部の加工精度を高めることのできるシリコン基板のエッチング方法及び該方法を用いるシリコン基板のエッチング装置を提供する。

【解決手段】シリコン基板に対してその厚さ方向に延びる凹部を形成する際に、シリコン基板を含む基板Sを収容する真空槽11内に六フッ化硫黄(SF6)ガスのプラズマを生成して、該シリコン基板の厚さ方向に延びる凹部を形成する。加えて、真空槽11内に三フッ化ホウ素(BF3)ガスのプラズマを生成して、上記凹部の内壁面にホウ素とシリコンとを含む保護膜を形成する。

(もっと読む)

炭化珪素半導体装置

【課題】チャネル移動度の低下を抑制しつつ閾値電圧の設定の自由度を高めることが可能な半導体装置を提供する。

【解決手段】炭化珪素層は、基板1の主表面上にエピタキシャルに形成されている。炭化珪素層には主表面に対して傾斜した側壁6を有する溝が設けられている。側壁6は{0001}面に対して50°以上65°以下のオフ角を有する。ゲート絶縁膜8は炭化珪素層の側壁6上に設けられている。炭化珪素層は、ゲート絶縁膜8を介してゲート電極9と対向しかつ第1導電型を有するボディ領域3と、ボディ領域3によって互いに分離されかつ第2導電型を有する1対の領域2、4とを含む。ボディ領域3は5×1016cm-3以上の不純物密度を有する。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

21 - 40 / 416

[ Back to top ]