Fターム[5F033GG00]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930)

Fターム[5F033GG00]の下位に属するFターム

Fターム[5F033GG00]に分類される特許

61 - 80 / 240

ディッシング効果を低減する接合パッドの設計

【課題】 ディッシング効果を低減する接合パッドの設計を提供する。

【解決手段】 集積回路構造は半導体チップを含み、このチップはさらに第1面と、この第1面を介して露出されるパターン化接合パッドを備え、パターン化接合パッドは、互いに電気的接続された複数の部分を含み、且つその中に少なくとも1つの開口を含むもので、集積回路はさらに、この少なくとも1つの開口の少なくとも1つの部分の中に充填された誘電材料を含む。

(もっと読む)

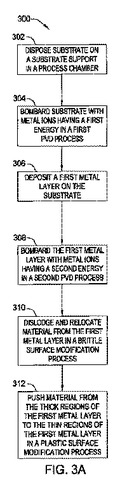

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に形成される貫通孔底部での絶縁層のノッチの発生、貫通孔下の配線層へのダメージを抑制し、電気的絶縁性の低下や配線層の接続不良を低減できる半導体装置及びその製造方法を提供する。

【解決手段】第一の絶縁層203と、第一の絶縁層上の第一の配線層204と、半導体基板201を貫通し、底部に第一の絶縁層を厚さ方向に除去した部分的なエッチ部を備えた貫通孔201aと、貫通孔の部分的なエッチ部の底部を除く内壁部から半導体基板の第二の面までを覆う第二の絶縁層206と、貫通孔の底部に、第一の配線層が露出するように第一の絶縁層に形成された開口部203aと、該開口部で第一の配線層と接すると共に貫通孔の第二の絶縁層上から半導体基板の第二の面の第二の絶縁層上に亘る第二の配線層202とを有し、開口部に接する第一の絶縁層が、半導体基板に接する第一の絶縁層より小さい厚さを有する。

(もっと読む)

ダイヤモンド半導体素子

【課題】100℃前後の温度でもパッド金属膜がダイヤモンド層から剥離しないダイヤモンド半導体素子を提供する。

【解決手段】ダイヤモンド層の上に、Al系またはAu系の配線膜、パッド金属膜、および金属ワイヤを備えたダイヤモンド半導体素子であって、パッド金属膜は、配線膜および金属ワイヤと電気的に接続されており、且つ、白金族金属またはその合金で構成されている。

(もっと読む)

電子基板、電子基板の製造方法、および表示装置

【課題】層間絶縁膜を介して配線された上下の導電パターンが、これらの導電パターン形成後に接続配線によって接続された構成において、接続抵抗の上昇を防止でき、さらにこの構成を製造する際のプロセスタクトタイムの削減が図られる電子基板を提供する。

【解決手段】基板1上に設けられた第1導電パターン3と、これを覆う状態で基板1上に設けられた層間絶縁膜5と、第1導電パターン3上に一部を重ねた状態で層間絶縁膜5上に設けられた第2導電パターン9とを備えている。第2導電パターン9と第1導電パターン3とが重なる位置には、第2導電パターン9および層間絶縁膜5に開口部31が設けられている。この開口部31は第1導電パターン3を底面としており、この開口部31の内壁を覆う接続配線33により、第2導電パターン9と第1導電パターン3とが結線されている。

(もっと読む)

電子又は電気機械部品及びナノ素子用の基板

本発明は、少なくとも一つの電子又は電気機械部品(708)及び一つ以上のナノ素子を支持するための基板であって、ベース支持部(301)と、触媒システム(302)と、障壁層(303)と、単結晶Si、Ge又はこれらの物質の混合物製の電子又は電気機械部品を収容するための層(304)とを備えた基板に関する。触媒システム(302)は、電子又は電気機械部品を収容することができる層(304)に接触することなく、ベース支持部(301)を覆い、障壁層(303)は触媒システム(302)と電子又は電気機械部品を収容することができる層(304)との間に挟まれている。障壁層(303)はベース支持部(301)と接触しない。  (もっと読む)

(もっと読む)

スルホールビアのための炭素ベース材質を備えた半導体デバイス

【解決手段】

半導体デバイスにおいて、デバイスの基板を通って延びるスルホールビアが炭素含有材質に基いて形成されてよく、それにより高温プロセスに対する優れた適合性がもたらされる一方で、ドープされた半導体材質等と比較して優れた電気的な性能ももたらされる。従って幾つかの例示的な実施形態では、スルホールビアは臨界的な回路要素を形成するために用いられる任意のプロセスステップに先立ち形成されてよく、それにより対応する半導体デバイスのデバイスレベルに対するスルホールビア構造の任意の干渉を実質的に回避することができる。その結果、高度に効果的な三次元集積化スキームを実現することができる。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法、および電子機器

【課題】有機材料からなる下地の絶縁性層に対してダメージを与えることなく、かつ上部に設けられる有機半導体層に対して良好なオーミックコンタクトが得られるソース電極およびドレイン電極を低コストで得ることを可能にする。

【解決手段】有機絶縁層からなる基板11と、基板11上にめっき成膜された層からなるソース電極13sおよびドレイン電極13dの第1層13-1と、第1層13-1よりも有機半導体材料に対して低オーミック接合を形成する金属材料からなり第1層13-1を覆う状態でめっき成膜されたソース電極13sおよびドレイン電極13dの第2層13-2と、第1層13-1および第2層13-2で構成されたソース電極13sおよびドレイン電極13d間にわたって設けられた有機半導体層15とを備えた有機薄膜トランジスタ1aである。

(もっと読む)

転写用紙、その製造方法、有機薄膜トランジスタおよびその製造方法

【課題】パターン毎に別途準備したマスクや専用のインク転写用の基材を用いることなく且つ導電性材料の利用効率が良好なパターン形成層を可能にし、この導電性パターン形成層を任意のフレキシブルフィルム基板に転写可能な転写用紙およびその製造方法、さらに、該転写用紙を利用した有機薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の転写用紙は、原紙面上に遅水性再湿糊層と速水溶性再湿糊層とを含む転写用紙基材と、導電性材料を含有するパターン形成層と、保護部材により形成されるオーバーコート層と、を有し、オーバーコート層形成後の王研式平滑度が1000秒以上である。この転写用紙に水を与え、前記糊層を溶解させ、フレキシブルフィルム等に接触させることで転写し、有機薄膜トランジスタを製造する。

(もっと読む)

積層構造体、多層配線基板、アクティブマトリックス基板、画像表示装置及び積層構造体の製造方法

【課題】インクジェット方式により緻密な配線の形成される積層構造体を提供する。

【解決手段】基板と、基板上において、エネルギーを付与することにより臨界表面張力が変化し、低表面エネルギー状態から高表面エネルギー状態へと変化する材料を含むものであって、エネルギーの付与により、高表面エネルギー領域と、低表面エネルギー領域とが形成されている濡れ性変化層と、濡れ性変化層の高表面エネルギー領域上に導電性材料により形成された導電層と、を有し、高表面エネルギー領域は、導電層による電気配線が形成される第1の領域と、第1の領域と接続されており、第1の領域よりも幅が狭く、第1の領域に導電材料を含む溶液を供給するための第2の領域とにより構成されていることを特徴とする積層構造体を提供することにより上記課題を解決する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】CMP(Chemical Mechanical Polishing)ストッパ膜を終点検出膜として利用しつつ、CMPによる平坦化精度を向上させる半導体装置及びその製造方法の提供。

【解決手段】ゲート電極3a上にはシリサイド層7aを形成するとともに、ゲート電極3b上にはシリサイド防止膜4bを形成し、半導体基板1上の第1の領域においては、シリサイド防止膜4bが露出するように、犠牲膜10、CMPストッパ膜9および層間絶縁膜8のCMPを行い、第2の領域においては、CMPストッパ膜9が露出するように、犠牲膜10のCMPを行うことで、第1の領域R1および第2の領域R2を平坦化する。

(もっと読む)

絶縁性被膜を有する構造体及びその製造方法、樹脂組成物並びに電子部品

【課題】電気絶縁性に優れる均一な絶縁性被膜を有する構造体及びその製造方法、絶縁性被膜を形成することができる樹脂組成物並びに電子部品を提供する。

【解決手段】本発明の絶縁性被膜を有する構造体の製造方法は、孔部を有する基板に、溶剤を塗布する工程と、樹脂組成物を、この樹脂組成物が孔部内の溶剤と接触するように、基板に塗布する工程と、塗膜を乾燥し、孔部の内壁面及び底面のうちの少なくとも内壁面に樹脂成分を含む被膜117、118、119を形成する工程と、孔部の内壁面及び底面を含む基板の全表面に形成されている被膜を加熱し、樹脂成分の硬化物を含む絶縁性被膜217、218、219とする加熱硬化工程と、基板の表面に形成されている絶縁性被膜219及び基板の孔部の底面に形成されている絶縁性被膜218を除去し、孔部の内壁面に形成されている絶縁性被膜217を残存させる表底面側絶縁性被膜除去工程と、を備える。

(もっと読む)

半導体チップ、半導体チップ群および半導体装置

【課題】 集積回路の周囲の回路及び配線の構造を簡素化可能で、チップ本体の小型化が可能なチップを提供する。

【解決手段】 半導体チップ1は平面形状が略四角形の板状のチップ本体3と、チップ本体3の表面に設けられた複数の集積回路5a、5bと、チップ本体3の裏面に設けられた他の回路としての配線13a〜13fと、集積回路5a、5bと配線13a〜13fを接続する接続手段としてのコンタクト11a、11bを有している。

コンタクト11a、11bはチップ本体3を貫通して設けられた導電性物質である。

このように、集積回路5a、5bを互いに接続するための配線を、チップ本体3の裏面2bに設けることにより、配線を表面2aに設けた場合と比べて、集積回路の周囲の他の回路(配線)の構造を簡素化することができる。

即ち、半導体チップ1を従来よりも小型化することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 厚いCESL膜を用いてもCESL膜やその上の層間絶縁膜に生じるボイドを回避し、高い駆動電流と高い信頼性を実現する。

【解決手段】 半導体基板10上にゲート絶縁膜12を介してゲート電極13を形成し、ゲート電極13を挟んで基板の表面部にソース/ドレイン領域18を形成してなるMOSFETを有する半導体装置であって、ゲート部のゲート長方向の側部に形成された側壁絶縁膜17と、ソース/ドレイン領域18上に形成された合金層19と、側壁絶縁膜17の側部に設けられ、ゲート長方向の断面で見た基板表面と成すテーパ角度が側壁絶縁膜17よりも小さいテーパ調整用絶縁膜21と、ゲート部、側壁絶縁膜17及びテーパ調整用絶縁膜21を覆うように形成された、チャネルに歪みを与えるための応力付与用絶縁膜22と、応力付与用絶縁膜22上に形成された層間絶縁膜25とを備えた。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

二座アミン安定化金属ナノ粒子

【課題】低コストで、低温でアニール可能であり、十分な貯蔵寿命を有する、安定な金属ナノ粒子組成物を提供する。

【解決手段】金属ナノ粒子の外面に会合した二座アミン安定剤を含む、二座アミン安定化金属ナノ粒子。また、分散された金属ナノ粒子の溶液を供給し、二座アミン安定化金属ナノ粒子分散液を基板上に堆積し、印刷された基板を加熱して基板の表面上に導電性構造部を形成して、基板上に導電性構造部を形成する方法。

(もっと読む)

マイクロパターンの製造方法

【課題】基板上にマイクロパターンを高精度にかつ容易に形成することを可能とするマイクロパターンの製造方法を得る。

【解決手段】 マイクロパターンが上面6aに形成される基板6と、前記マイクロパターンに対して反転されたパターン形状を有するフィルム状パターニング材1Aとを用意する工程と、前記フィルム状パターニング材1Aを前記基板6の上面に積層する工程と、前記フィルム状パターニング材1Aが積層された基板6の上面に被パターニング材料7を塗布する工程と、前記基板6の上面6aから前記フィルム状パターニング材1Aを除去して、前記フィルム状パターニング材1Aと反転されたマイクロパターンとなるように前記被パターニング材料7をパターニングし、それによって、被パターニング材料7からなるマイクロパターン7Aを形成する工程とを備える。

(もっと読む)

半導体チップ及び半導体装置

【課題】半導体基板の裏面側から効率よく放熱する半導体チップを実現できるようにする。

【解決手段】半導体チップ10は、基板11と、基板11の素子形成面側に形成され、複数の半導体素子を含む集積回路12と、基板11における複数の半導体素子のうちの所定の半導体素子30と対応する領域に形成さた放熱プラグ31とを備えている。放熱プラグ31は、素子形成面と反対側の面に開口する非貫通孔に埋め込まれた基板11と比べて熱伝導率が大きい材料からなる。

(もっと読む)

配線の製造方法

【課題】耐熱性が低い基材上に、ばらつきが少なく、電気抵抗がほぼ均一で、かつ、低抵抗化を実現した配線を製造する方法を提供することを目的とする。

【解決手段】基材上に配置された金属粒子を含む塗布膜に電流を流すことにより前記塗布膜を焼成し、前記金属粒子から形成された配線を得る配線の製造方法が提供される。この製造方法では、前記金属粒子が、金、銀、白金、銅、鉄、パラジウム、スズ、ニッケル、アルミニウム、ジルコニウム、チタンおよびタングステンの金属群から選択された1種の金属、または、前記金属群から選択された2種以上の合金であるのが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】薄膜トランジスタを印刷法を用いて作製する場合、第1の電極と第2の電極のあわせ精度が問題となる。ホトリソグラフィで作製すれば、各層のホトマスクが必要となりコストが増大する。

【解決手段】本願発明の骨子は、基板上に、ゲートパターン用ホトマスクでの露光により形成されたレジストパタンを用いてゲート形状の加工のみならず、ソース・ドレイン電極の加工を、リフトオフを用いて行う。こうして、ソース・ドレイン電極とゲート電極の位置合わせが施される。

(もっと読む)

61 - 80 / 240

[ Back to top ]