Fターム[5F033GG00]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930)

Fターム[5F033GG00]の下位に属するFターム

Fターム[5F033GG00]に分類される特許

81 - 100 / 240

導電膜の形成方法、トランジスタ、および有機エレクトロルミネッセンス素子

【課題】所定の形状に精度よくパターニングすることができる導電膜の形成方法を提供することである。

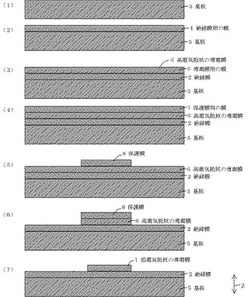

【解決手段】電気絶縁性を有する被成膜体の表面上に、金属微粒子を含む導電膜用の塗布液を塗布して導電膜用の膜を形成し、被成膜体に塗布された前記導電膜用の膜を第1の温度で加熱し、前記低電気抵抗の導電膜よりも電気抵抗が高い高電気抵抗の導電膜を形成し、前記高電気抵抗の導電膜の一部を除去し、高電気抵抗の導電膜を所定の形状にパターニングし、パターニングされた高電気抵抗の導電膜を第2の温度で加熱して電気抵抗を低下させ、低電気抵抗の導電膜を形成する。

(もっと読む)

被覆パターン形成方法およびパターン形成方法

【課題】CVDを使用することなく、被覆されたパターンを形成することが可能な被覆パターン形成方法およびこれを利用してより高密度なパターンを形成するパターン形成方法を提供する。

【解決手段】パターン2を有する熱伝導性基板1に熱重合性組成物を塗布して塗膜3を形成したのち、ベークおよび現像をして被覆パターン7を形成する。このようにして形成された被覆パターン上に無機性組成物膜を形成したのち、エッチングすることによって、より高密度なパターンを形成することができる。

(もっと読む)

有機デバイスおよびその製造方法

【課題】可撓性のある樹脂基板上に領域選択的に形成された、密着性およびデバイス特性に優れる有機デバイスおよび、その作製方法を提供する。

【解決手段】デバイスが形成される可撓性基板表面領域と該基板表面に設けられた前記基板以外の材料からなる所定の領域との両領域か、またはいずれかの領域の表面に、有機分子を化学結合させて形成した機能性有機分子層と、前記機能性有機分子層上の一部に、前記有機分子と同種または異種の有機分子とを化学結合させて、更に積層した少なくとも一つ以上の機能性有機分子層とを備えた有機デバイスであって、前記領域において、有機分子層の積層回数を異ならせた領域が含まれていることを特徴とする有機デバイスを提供する。

(もっと読む)

半導体装置および電子機器

【課題】積層された各半導体チップが備える導体ポスト同士の接合が、低温下の処理でも、導電性に優れ、かつ、高い寸法精度で強固に行われている信頼性の高い半導体装置、かかる半導体装置を備える電子機器を提供すること。

【解決手段】半導体装置1は、インターポーザー2と、第1の電気配線34および厚さ方向に貫通して設けられた第1の導体ポスト33とを有する第1の半導体チップ3と、第2の電気配線44および厚さ方向に貫通して設けられた第2の導体ポスト43とを有する第2の半導体チップ4とを備える。第1の導体ポスト33と第2の導体ポスト43とは、接合膜433を介して接合されている。この接合膜433は、導電性を有し、かつ、所定の処理を施すことにより接着性を発現する特定の材料で構成されており、その表面に発現した接着性によって、これら導体ポスト33、43同士を接合している。

(もっと読む)

半導体装置

【課題】良好な特性を得ながら、小型化、高耐圧化および低消費電力化が可能な半導体装置を提供する。

【解決手段】この半導体装置1は、シリコンよりも大きいバンドギャップを有し、パワートランジスタ2が形成されたSiC層11と、SiC層11の主表面11aよりも上側の所定領域に形成されるとともに、制御回路用のNMOSトランジスタ3およびPMOSトランジスタ4が形成され、SiC層11とは別の層からなるシリコン層21と、SiC層11のパワートランジスタ2とシリコン層21のNMOSトランジスタ3およびPMOSトランジスタ4とを接続するAl配線5とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】金属ナノ微粒子を用いた、電極、配線形成方法では、金属ナノ微粒子溶液を塗布、印刷後抵抗値を落とすために200℃程度の熱処理が必要である。プラスチックなどのフレキシブル基板では、耐熱性が150℃程度であるため、この熱処理により基板の変形が出てしまう。

【解決手段】本発明は、ハロゲンを有するガスに金属ナノ微粒子を所望の形状に印刷した後に暴露する事によって、なんら過熱焼成することなく、金属電極、配線を形成できる。

(もっと読む)

スパッタターゲットの製造方法

【課題】ヒロック、エッチング残渣、ITO等との電気化学反応の発生を防止した低抵抗な配線膜を再現性よく成膜することができ、かつスパッタ時におけるダスト発生を抑制したスパッタターゲットの製造方法を提供する。

【解決手段】Y、Sc、La、Ce、Nd、Sm、Gd、Tb、Dy、Er、Th、Sr、Ti、Zr、V、Nb、Ta、Cr、Mo、W、Mn、Tc、Re、Fe、Co、Ni、Pd、Ir、Pt、Cu、Ag、Au、Cd、Si、PbおよびBから選ばれる少なくとも1種の第1の元素を0.001〜30原子%の範囲で含み、残部がAlからなるインゴットまたは焼結体を、大気溶解法、真空溶解法、急冷凝固法、粉末冶金法で作製するにあたって、インゴットまたは焼結体にCを第1の元素量に対して20原子ppm〜37.8原子%の範囲で含有させ、得られたインゴットや焼結体を加工してスパッタターゲットを作製する。

(もっと読む)

導電性銀外形を印刷する方法

【課題】本発明の目的は、2つ以上の成分を基板に印刷して導電性銀外形を形成する方法を提供することである。

【解決手段】本発明は、導電性銀外形を基板上に形成する方法であって、前記方法は、2つ以上の溶液(第1の溶液は、銀化合物溶液であり、第2の溶液は、前記銀化合物のためのヒドラジン化合物を含んでなる還元剤溶液であり、前記ヒドラジン化合物還元剤溶液は、前記銀化合物溶液から離れている)を準備するステップと、前記銀化合物溶液および前記ヒドラジン化合物還元剤溶液を前記基板上にプリントヘッドにより印刷するステップ(前記銀化合物溶液および前記ヒドラジン化合物還元剤溶液は、前記銀化合物溶液および前記ヒドラジン化合物還元剤溶液の両方の前記基板上への印刷直前、印刷中、または印刷後に混合される)と、前記銀化合物を還元して該印刷された銀外形を前記基板上に形成するステップとを含む。

(もっと読む)

半導体装置

【課題】 本発明は半導体装置における信頼性向上を図るものである。

【解決手段】 本発明の半導体装置は、半導体チップの第1の主面上に形成されたパッド電極53と、前記半導体チップの第1の主面に接着されたガラス基板56と、前記半導体チップの第2の主面から前記パッド電極53の表面に貫通するビアホール81と、前記ビアホール81の側壁及び前記半導体チップの側端部に形成されたCVD膜から成る側壁絶縁膜59Aと、前記ビアホール81を通して、前記パッド電極53と電気的に接続された配線層63とを具備することを特徴とする。

(もっと読む)

導電性パターンの形成方法、積層基板の製造方法及び微細流路構造体の製造方法

【課題】ガラス基板の表面に薄膜の導電性パターンを形成することができる導電性パターンの形成方法の提供。

【解決手段】基板100上に導電性パターン110を形成する工程と、導電性パターン110が形成された基板100を、基板100の表面が軟化を生じる温度まで加熱し、上方から押圧部材120を導電性パターン110に押し付けて、導電性パターン110を基板100の表面に押し込む工程と、を備える。

(もっと読む)

ポリマー膜のパターニング方法

【課題】ポリマー膜の優れた特性を損なうことなく基板上にポリマー膜をパターン形成する。

【解決手段】ポリマー膜のパターニング方法において、基板上にパターニングされたレジスト層を形成後に、前記基板上にポリマーインクを塗布し、その後、前記レジスト層を剥離することで前記塗布されたポリマーインクを併せて除去することを特徴とするポリマー膜のパターニング方法。

(もっと読む)

ペースト組成物、絶縁膜、多層配線構造、プリント基板、画像表示装置、及びペースト組成物の製造方法

【課題】 スクリーン印刷法により微細パターン印刷を可能にする絶縁性ペースト組成物の提供。

【解決手段】 シリカ及び/又はチタニアの微粒子を含む絶縁性充填材と、少なくとも表面はシリカ及びチタニアとは異なる絶縁性粒子と、からなるフィラー並びに樹脂を含有し、前記絶縁性充填材の体積が、前記フィラー全体の体積の20%以上、80%以下であることを特徴とするペースト組成物。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に複数の電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。複数の電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。複数の電界効果トランジスタはそれぞれ前記半導体層に歪みを与える絶縁膜で覆われている。

(もっと読む)

接点抵抗が改善された半導体構造およびその製造方法(接点抵抗が改善された半導体構造)

【課題】 構造の接点抵抗を改善した、すなわち低下させた半導体構造を提供する。

【解決手段】 自己組織化・ポリマー技術を用いて、半導体構造の導電性コンタクト領域に存在する材料内に少なくとも1つの配列されたナノサイズ・パターンを形成する。配列されたナノサイズ・パターンを有する材料は、相互接続構造または電界効果トランジスタの半導体ソースおよびドレイン領域の導電材料である。接点領域内に整列ナノサイズ・パターニング材料が存在することによって、以降の接点形成のための全領域(すなわち界面領域)が拡大し、これによって構造の接点抵抗が低下する。接点抵抗の低下により、構造を通る電流が改善する。上述のことに加えて、本発明の方法および構造では、接合領域が不変のままであるので、構造の接合容量は影響を受けない。

(もっと読む)

半導体装置及びその作製方法

【課題】配線に低抵抗な材料を用いることにより、画素部の大面積化に対応し得る半導体装置及びその作製方法を提供する。

【解決手段】

ゲート電極及び第1の配線上に形成された絶縁膜と、絶縁膜上にゲート電極と重なって形成された半導体層と、絶縁膜上に形成され、かつ、半導体層に電気的に接続された接続電極と、を有し、接続電極は、絶縁膜に設けられたコンタクトホールを介して第1の配線に電気的に接続され、ゲート電極及び第1の配線は、第1の導電層と、第1の導電層上の第2の導電層と、第2の導電層上の第3の導電層とでなる積層構造を有し、第2の導電層は、第1の導電層及び第3の導電層より低抵抗であり、第1の導電層及び第3の導電層は、第2の導電層より高融点の導電材料からなり、第2の導電層の端部における断面形状はテーパー形状であることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ICチップなどの半導体チップをより薄型化することが可能な技術を提供する。

【解決手段】集積回路が形成された半導体基板をCMP等により研磨し、半導体基板中に脆化層を形成して半導体基板の一部を分離することにより半導体基板を薄膜化して、従来にない薄さのICチップなどの半導体チップを得る。また、このような薄膜化したICチップに設けられた配線と、インターポーザに設けられた配線とを、導電性材料又はめっき処理により形成される導電膜を介して電気的に接続する。

(もっと読む)

半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法

本明細書には概して半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法が記載されている。  (もっと読む)

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法であって、基板が少なくとも銅含有表面層を含む方法を提供する。

【解決手段】この方法は、第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

半導体装置及びその作製方法

【課題】接続孔内から無電解めっき層が剥がれて抜け落ちるのを防止できる半導体装置及びその作製方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体層32上に形成された第1の絶縁層33,203と、前記第1の絶縁層に形成され、前記第1の絶縁層の上面から途中まで異方性エッチングにより形成された第1の接続孔203cと、前記第1の絶縁層に形成され、前記第1の接続孔に繋げられ、前記第1の接続孔下の前記第1の絶縁層が等方性エッチングにより形成され、前記半導体層上に位置する第2の接続孔203gと、前記第1の接続孔内の側面及び前記第1の絶縁層上に形成された第2の絶縁層203dと、前記第2の接続孔の底面の前記半導体層から成長され、前記第2の接続孔内及び前記第1の接続孔内に埋め込まれた無電解めっき層204aと、を具備することを特徴とする。

(もっと読む)

半導体装置のテスト構造物及び半導体装置

【課題】半導体装置のテスト構造物及び半導体装置を提供する。

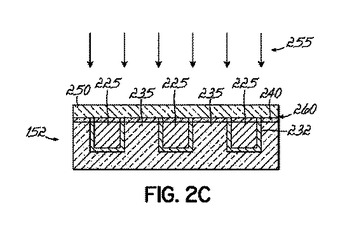

【解決手段】半導体装置のテスト構造物は、トランジスタ150、ダミートランジスタ160、及びパッドユニットを具備する。トランジスタ150は、基板の第1アクティブ領域120上に形成される。ダミートランジスタ160は、基板の第2アクティブ領域130上に形成され、トランジスタ150に接続される。パッドユニットは、トランジスタ150に接続される。ダミートランジスタ160により、トランジスタ150が受けるプラズマダメージが減少する。

(もっと読む)

81 - 100 / 240

[ Back to top ]