Fターム[5F033GG00]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930)

Fターム[5F033GG00]の下位に属するFターム

Fターム[5F033GG00]に分類される特許

21 - 40 / 240

パターン形成方法及び回路基板の製造方法

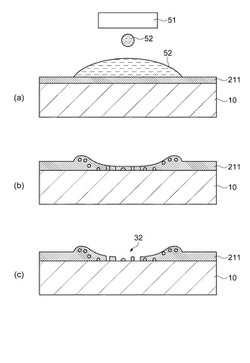

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル間の短絡を防止した上で、活性領域上にシリコン膜が十分に形成された半導体装置を提供する。

【解決手段】半導体基板2の表層に埋め込み形成された素子分離膜8によって、活性領域7が区画された半導体装置1であって、前記活性領域7の側面17が露出するように、前記素子分離膜8の上面の一部が除去されて設けられた凹部と、前記凹部を埋め込みつつ、前記活性領域7の上面7d及び前記側面17と接するように設けられたシリコン膜10と、を有することを特徴とする。

(もっと読む)

半導体デバイス

【課題】軽量であり、かつ強固な信頼性を備えた半導体デバイスを提供する。

【解決手段】集積回路チップは、プラスチックの基板101と、基板101上に配されたポリマー誘電体103と、電極同士の間に形成された有機半導体材料112および受動層114の少なくとも1つのを含むアクティブデバイス104と、少なくとも1つのアクティブデバイス104に隣接する導電性ポリマー106および/または108とを備えている。

(もっと読む)

SiCの除去法

【課題】基板に形成されたカーバイドシリコン層の少なくとも露出された部分を除去するための方法を提供する。

【解決手段】カーバイドシリコン層45を酸素含有プラズマに曝すことにより、前記カーバイドシリコン層45の少なくとも露出された部分を酸化シリコン層に変換し、そして基板から前記酸化シリコン層を除去するステップからなる。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

半導体チップの多チップ・アセンブリを形成する方法

3次元集積のための裏側ダミー・プラグを含む半導体構造およびこれを製造する方法

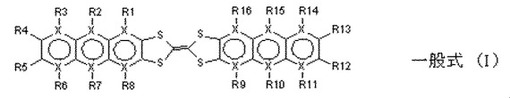

有機積層膜

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

基板製造方法及び基板

【課題】CMPの処理時間を短縮する。

【解決手段】基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

(もっと読む)

銅プラグを有する半導体デバイスおよびデバイスを形成するための方法

【課題】絶縁層がデバイスの最終配線層と接触する銅プラグを有する、半導体デバイスを提供する。

【解決手段】銅プラグと絶縁層とを分離する障壁層も存在可能である。他の実施形態では、絶縁層と銅プラグとの間にアルミニウム層も存在可能である。半導体デバイスを生成するためのプロセスも開示される。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

微小コイル装置およびその製作方法

導電性コイルの製作方法。この方法は、コイル、通常、平面らせん状の導電性コイルを製作するために半導体製造プロセス(例えばTSV)を使用することを含む。 (もっと読む)

21 - 40 / 240

[ Back to top ]