Fターム[5F033GG00]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930)

Fターム[5F033GG00]の下位に属するFターム

Fターム[5F033GG00]に分類される特許

41 - 60 / 240

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

アクティブマトリックスアレイ及びその製造方法

【課題】印刷塗布して形成された絶縁膜の絶縁特性を良好に保持した状態で、生産性を向上することが可能なアクティブマトリックスアレイ及びその製造方法を提供する。

【解決手段】下地層34上に絶縁膜インクを印刷塗布する。印刷塗布された絶縁膜インクに含まれる溶媒が所定の絶縁特性が得られるまで十分に揮発させる前に終了するように絶縁膜インクを焼成して絶縁膜32を形成する。下地層34上に形成された絶縁膜32上に1つ以上の開口部33を有する導電層31を形成する。それにより、導電層31に設けられた開口部33から絶縁膜32内に残っている溶媒を揮発させることができるので、導電層31におおわれた絶縁膜32の絶縁特性を良好にすることができる。また、絶縁膜32が十分に揮発する前に、絶縁膜32上に導電層31を形成することができるので、生産性を良くすることができる。

(もっと読む)

金属結晶領域、特に集積回路における金属結晶領域を生成する方法

本方法は、例えば相互接続ラインを形成するために、薄い結晶(8)のシートを、基板(1)のトレンチに堆積される、このシートと同一のタイプであるが、アモルファスであるか小さな粒径である金属(6)に固定することを含む。焼鈍しは、このラインにシートの結晶構造を徐々に与える。結晶(8)が除去されると、高度の導電結晶ラインが得られる。それは、その粒径が非常に拡大されているからである。金属は、銅、銀及びアルミニウムから選択される。  (もっと読む)

(もっと読む)

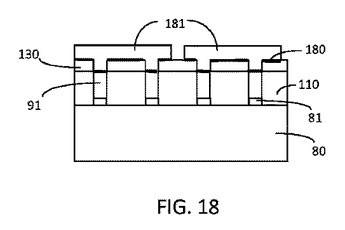

金属/有機誘電体界面でのクラックの低減

有機誘電体材料(110)中に埋め込まれた第2構造(91)への金属相互接続(181)を提供する方法であって、有機誘電体材料(110)中に埋め込まれた、例えば金属ピラー(91)のような第2構造を有する第1構造を得る工程と、少なくとも第1構造のいくつかの位置で、有機誘電体材料(110)の上に硬い層(130)を提供する工程であって、硬い層(130)は有機誘電体材料(110)の剛性より高い剛性を有する工程とを含む方法。この方法は、第1構造(91)と有機誘電体材料(110)との間の界面でクラックの無い相互接続構造を提供する。  (もっと読む)

(もっと読む)

ブロック共重合体を用いてホール又はビアを有するデバイスを形成する方法

【課題】 ブロック共重合体を用いて所定の位置にホール又はビアを有するデバイスを形成する方法を提供する。

【解決手段】 例えば、光リソグラフィを用いて、輪郭を付けられた凸状のセグメントによって与えられる断面を有する開口部を基板内に形成する。開口部の断面は、例えば、重なった円形領域によって与えることができる。側壁は、種々の点で隣接し、そこで突起を画定する。ブロック共重合体を含むポリマーの層を開口部及び基板の上に塗布し、自己集合させる。開口部内に個別分離ドメインが形成され、これらを除去してホールを形成し、これを下層の基板に転写することができる。これらのドメイン及びこれらの対応するホールの位置は、側壁及びそれらに付随する突起によって所定の位置に誘導される。これらのホールを隔てる距離は、何も側壁がない場合にブロック共重合体(及び何れかの添加剤)が自己集合したとする場合よりも大きく又は小さくすることができる。

(もっと読む)

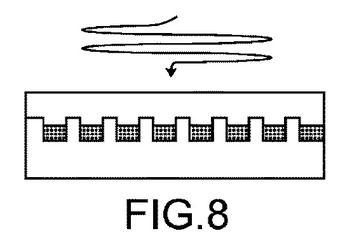

薄膜電子素子の製造方法

【課題】

転写型に形成された薄膜電子材料層を、転写型から良好に離型して転写することのできる薄膜電子素子の製造方法を提供する。

【解決手段】

凹凸パターンが形成された転写型4に親液処理をする親液処理工程と、親液処理がされた転写型4に剥離層を形成する剥離層形成工程と、剥離層が形成された転写型4に薄膜電子材料層を形成する薄膜電子材料層形成工程と、前記転写型4に形成された薄膜電子材料層を基板上に転写する転写工程と、を備えている。剥離層を形成する前に親液処理を行うことで、剥離層をムラなく均一に広がるように形成することができる。それにより、転写型4に形成された薄膜電子材料層を転写型4から良好に離型して転写することができる。

(もっと読む)

複合体、複合体の製造方法及び半導体装置

【課題】複合体の樹脂層に形成された高密着、高信頼性、高周波対応の微細配線やビアを有する複合体、複合体の製造方法及び半導体装置を提供する。

【解決手段】樹脂層1と導体層2とを含む第1の複合体100であって、前記樹脂層1の表面に最大幅が1μm以上、10μm以下の溝3と当該溝3内部に導体層2を有し、当該導体層2と接する前記樹脂層1の表面の算術平均粗さ(Ra)が0.05μm以上、0.45μm以下である、及び/又は、前記樹脂層1に直径が1μm以上、25μm以下のビア孔と当該ビア孔内部に導体層2を有し、前記ビア孔内部の樹脂層1の表面の算術平均粗さ(Ra)が0.05μm以上、0.45μm以下であることを特徴とする。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

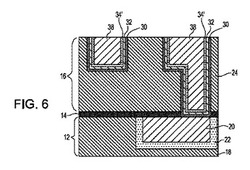

集積回路を製造する装置及び方法

本発明は、厚膜金属層14を有する集積回路10を製造する装置に関する。金属ペースト14の層は、熱伝導基板12上に適用手段24によって適用される。金属ペースト14は、予め決められたサイズの金属粒子を含む。RF生成器16は、金属ペースト14にRFエネルギー18を選択的に誘導結合させる。金属粒子を加熱するために、金属ペースト14の金属粒子の予め決められたサイズは、RFエネルギー18の結合周波数に対応する。このようにして、金属ペースト14の金属粒子は、従来のプロセスのパワーの何分の一かのパワーで、金属ペースト14を予備焼結する必要なく、加熱される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッドよりも径の小さな貫通孔を半導体基板自体に設けることなく、上下に積層された半導体チップ間の電気的な接続を行う。

【解決手段】半導体基板S1の横にはみ出すように電極パッドP1を配置し、半導体基板S1の周囲を取り囲むように配置された樹脂層J1上にて支持し、電極パッドP1が上下に重なるように半導体チップC1を積層し、貫通孔T1内に導電体D1を埋め込むことで、上下の電極パッドP1を電気的に接続し、上下に積層された半導体チップC1間の電気的な接続を行う。

(もっと読む)

積層構造体及び積層構造体の製造方法

【課題】耐マイグレーションに強い積層構造体を提供する。

【解決手段】基板と、基板上において、エネルギーを付与することにより臨界表面張力が変化し、低表面エネルギー状態から高表面エネルギー状態へと変化する材料を含むものであって、エネルギーの付与により、第1の高表面エネルギー領域及び第2の高表面エネルギー領域と、低表面エネルギー領域とが形成されている濡れ性変化層と、第1の高表面エネルギー領域上に導電性材料により形成された第1の導電層と、第2の高表面エネルギー領域上及び第1の導電層上に形成された第2の導電層を有し、第1の導電層を第2の導電層により覆われた積層構造の導電層が形成されているものであることを特徴とする積層構造体を提供することにより上記課題を解決する。

(もっと読む)

コバルト膜の形成方法

【課題】コバルト前駆体の使用効率の高い、化学気相成長方法によるコバルト膜の形成方法を提供すること。

【解決手段】上記コバルト膜の形成方法は、基体上にコバルト膜を形成する方法であって、少なくとも(A)一酸化炭素を含む気体の存在下でコバルトカルボニル錯体を昇華する工程と(B)基体上にコバルトカルボニル錯体の昇華物を供給してコバルトに変換する工程とを含むことを特徴とする方法である。

(もっと読む)

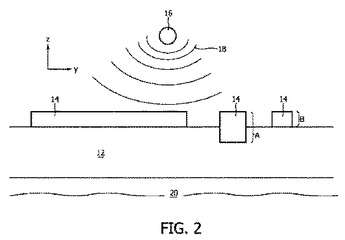

半導体構造、半導体構造を形成する方法、および半導体デバイスを操作する方法(信号忠実度および電気的分離が強化されたSOI無線周波スイッチ)

【課題】SOI(セミコンダクタ・オン・インシュレータ)基板内の底部半導体層からの半導体デバイスについて強化された信号分離を可能とする半導体構造、これを製造する方法、およびこれを操作する方法を提供する。

【解決手段】底部半導体層10と反対の導電性タイプを有するドープ接点領域18は底部半導体層10内の埋め込み絶縁体層20の下に設ける。少なくとも1つの導電ビア構造47,77は、相互接続レベル金属ライン94から、中間工程(MOL)誘電体層80、最上部半導体層30内の浅いトレンチ分離構造33、および埋め込み絶縁体層20を通り、ドープ接点領域18まで延びる構造とする。

(もっと読む)

有機トランジスタアレイ、表示パネル及び表示装置

【課題】オフ電流を低減することが可能な有機トランジスタアレイ、表示パネル及び表示装置を提供する。

【解決手段】マトリクス状に設けられている走査線11及び信号線12と、走査線11と接続するゲート電極21と、ゲート電極21及び走査線11を覆うように形成されている第1のゲート絶縁膜と、信号線12と接続するソース電極23と、チャネル領域Cを挟んでソース電極23と対向して形成されているドレイン電極24と、チャネル領域Cに形成されている有機半導体層25とを備え、走査線11及び信号線12が交差して形成されている画素領域A1、A2に設けられる有機トランジスタ20とを有する有機トランジスタアレイ10において、ゲート電極21は、更に平面視でドレイン電極24と信号線12とに挟まれる領域Sに形成され、有機半導体層25は、更に平面視でドレイン電極24と信号線12に挟まれる領域S1に形成されている。

(もっと読む)

機能性有機物素子及び機能性有機物装置

【課題】 薄くて軽く、しかも、酸素や水などの外部物質の侵入を阻止する封止性能に優れた封止部材を備えた、カラ−ディスプレイなどに好適な機能性有機物素子及び機能性有機物装置を提供すること。

【解決手段】 まず、絶縁性基板1の上に、有機半導体層4を有する有機薄膜トランジスタを形成する。次に、有機半導体層4への外部物質の侵入を阻止する第1の封止層31を、形成時に有機半導体層4にダメージを与えることが少ない蒸着法や塗布法などで、有機薄膜トランジスタを被覆するように形成する。これとは別に、プラズマCVD法などによって、封止性能の高い第2の封止層33を有機高分子樹脂材32に形成する。次に、第1の封止層31が設けられた基板1に、第2の封止層33が設けられた有機高分子樹脂材32を、防湿性樹脂34によって貼り付ける。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】薄膜トランジスタを有する半導体装置において、薄膜トランジスタの半導体層を、金属元素が添加された酸化物半導体層とする。金属元素として鉄、ニッケル、コバルト、銅、金、モリブデン、タングステン、ニオブ、及びタンタルの少なくとも一種類以上の金属元素を用いる。また、酸化物半導体層はインジウム、ガリウム、及び亜鉛を含む。

(もっと読む)

GaN系LED素子およびその製造方法

【課題】p電極にTCO膜を用いたGaN系LED素子に関して、その高出力化および信頼性向上の少なくともいずれかを実現すること。

【解決手段】n型GaN系半導体層の上にGaN系半導体からなる活性層とp型GaN系半導体層とを順次積層してなり、前記p型GaN系半導体層の前記活性層側の主面とは反対側の主面上に形成されたTCO膜と該TCO膜に接続されたp側ボンディングパッドとを含むp電極と、前記TCO膜の前記p型GaN系半導体層側とは反対側の主面上の一部に形成された抵抗制御膜と、前記p型GaN系半導体層と前記TCO膜との界面に形成されて前記抵抗制御膜の下方の領域において前記活性層を流れる電流を減少させる抵抗増加領域と、前記n型層に接続されたn側ボンディングパッドと、を有するGaN系LED素子。

(もっと読む)

電子デバイス及びその製造方法

【課題】塗布プロセス(印刷やIJ)により製造が可能であって、電磁波照射による異常放電がなく、生産効率及び生産安定性が高く、かつキャリア移動度及びon/off比が向上した電子デバイス及びその製造方法を提供することにある。

【解決手段】基板上に、電極を有し、少なくとも1部に熱変換材料または熱変換材料を含むエリアと、前記熱変換材料または熱変換材料を含むエリアに隣接もしくは近接して電磁波吸収能を持つ物質または電磁波吸収能を持つ物質を含むエリアを配置し、電磁波を照射して、該電磁波吸収能を持つ物質が発生する熱により、熱変換材料を機能材料に変換する電子デバイスの製造方法において、前記電極の辺が形成する角が全て90°より大きく180°より小さい、または、曲面であることを特徴とする電子デバイスの製造方法。

(もっと読む)

ジピリジル系レベリング剤によるマイクロエレクトロニクスにおける銅の電子沈積

【課題】半導体集積回路デバイス基板におけるビア構造をメタライズするための方法を提供する。

【解決手段】半導体集積回路デバイス基板は、前面、背面、ビア構造を備え、ビア構造は、基板の前面に開口部、基板の前面を内向きに伸びる側壁部、および底部を備え、前記方法は以下からなる:

半導体集積回路デバイス基板に、(a)銅イオン源、および(b)レベラー化合物からなる電解銅沈積組成物を接触させて、前記レベラー化合物はジピリジル化合物およびアルキル化剤の反応生成物からなり;

電流を電解銅沈積組成物に供給し銅金属をビア構造の底部および側壁部に沈積し、これによって銅充填ビア構造を得る。

(もっと読む)

半導体装置及びその製造方法

【課題】 高アスペクト比の貫通電極を有する半導体装置を低温プロセスによって製造する。

【解決手段】 半導体基板1の表面側に配置された第1の電極3と裏面側の第2の電極6は、接続孔4に充填された導電物7と、接続孔4内に延在する第2の電極6の延在部6aとによって電気的に接続される。接続孔4が高アスペクト比であっても、第2の電極6を接続孔4の底部まで形成する代わりに導電物7を用いることで、低温プロセスによる成膜が可能となる。

(もっと読む)

41 - 60 / 240

[ Back to top ]