Fターム[5F033GG00]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930)

Fターム[5F033GG00]の下位に属するFターム

Fターム[5F033GG00]に分類される特許

221 - 240 / 240

表面改質によるパターン化方法

(a)再配置可能なアパーチャマスクを基板の近くに配置する工程と、(b)基板の部分を表面改質処理に選択的に曝す工程であって、曝された部分が、アパーチャマスクの1つ以上のアパーチャによって画定される工程とによって表面改質をパターン化する方法。 (もっと読む)

導電性パターンの形成方法

【課題】 より簡便に比較的厚さが大きく、インクの着弾径より小さな線幅でも着弾痕のない導電性パターンを得る形成方法を提供することにある。

【解決手段】 撥液剤80は、前述したようにバンク上面12eにおいて、水に対して110°以上の高い接触角を備えているため、導電性液状材料11に対しても接触角θは大きい。一方、バンク溝部20は前述したように親水性となっているために、基板10に到達した導電性液状材料11は、バンク上面12eに配設されている撥液剤80から圧縮力を受け、逆にバンク溝部20からは張力を受ける。このために、導電性液状材料11はバンク溝部20の溝に沿って、同図紙面の垂直方向の前後に広がっていくことができる。また、バンク溝幅Bが液滴の大きさDより大きい場合は、より安定して導電性液状材料11をバンク溝部20の中へ収容することができる。

(もっと読む)

配線基板及び半導体装置の作製方法

【課題】少ない工程数で大面積基板に微細な形状を有する配線を形成する方法を提供する。また、少ない工程数及び原料の削減により、コスト削減及びスループットの向上が可能であり、かつ微細構造の半導体素子を有する半導体装置の作製方法を提供する。

【解決手段】金属粒子と有機樹脂とで形成される液状物質にレーザ光を照射し、金属粒子の一部を溶融した後、レーザ光が照射されない液状物質を除去して、配線、電極等に代表される導電層を基板上に形成することを特徴とする。また、本発明は、上記焼結された導電層を配線又は電極として有する半導体装置を形成することを特徴とする。

(もっと読む)

薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 薄膜形成領域の断面全域に機能液を充填することにより、形成される薄膜の機能を実現するために充分な断面積と必要な断面形状を有する薄膜を形成することができる、薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器を実現する。

【解決手段】 薄膜パターン形成方法は、第1の薄膜を構成する材料を含む機能液に対して親液性を有する第2の薄膜を形成するステップと、第2の薄膜の表面に、機能液に対する撥液性を付与する処理を行うステップと、第2の薄膜の一部を取り除いて、第1の薄膜のパターン形状を規定する凹部を形成するステップと、凹部に向けて機能液を吐出するステップと、凹部に吐出された機能液を乾燥させて第1の薄膜を形成するステップとを有する。半導体装置の回路配線は、上記薄膜パターン形成方法を用いて形成されており、電気光学装置は当該半導体装置を備え、電子機器は上記電気光学装置を備える。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

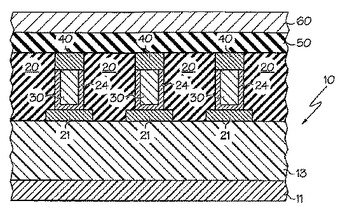

カルコゲニド型メモリ・デバイスのための金属キャップの無電解メッキ

カルコゲニド型メモリ・デバイスにおいて導電性相互接続部の上側に金属キャップを形成する方法が提供され、該方法は、基板10の上側に第1導電性材料の層21を形成する工程と、基板及び第1導電性材料の上側に絶縁層20を堆積させる工程と、絶縁層に開口22を形成して、第1導電性材料の少なくとも一部分を露出させる工程と、絶縁層の上側に且つ開口内に第2導電性材料30を堆積させる工程と、第2導電性材料を部分的に除去して開口内に導電性区域を形成する工程と、開口内の導電性区域を絶縁層の上面よりも低い高さまで凹ます工程と、開口内の凹まされた導電性区域の上側に第3導電性材料のキャップ40を形成する工程と、キャップの上側にカルコゲニド型メモリ・セル材料のスタックを堆積させる工程と、カルコゲニド型メモリ・セル材料のスタックの上側に導電性材料を堆積させる工程とを備え、第3導電性材料は、コバルト、銀、金、銅、ニッケル、パラジウム、白金、及びそれらの合金の群の中から選択される。  (もっと読む)

(もっと読む)

基板にダマシン構造を製造する方法、集積回路の製造方法およびこれらの方法によって製造される半導体装置

ダマシン構造の製造は、ダマシン構造用の凹部(30)の周りの領域を保護するため、犠牲層(20)を基板(10)上に形成する工程と、前記凹部内に、前記犠牲層と電気接触状態でバリヤ層(40)を形成する工程と、前記凹部内にダマシン構造(50)を形成する工程と、平坦化する工程とを含む。平坦化の間、犠牲層は、バリヤ層またはダマシン構造と電気化学的に反応する。これは、ダマシン構造のくぼみまたは突起を減少させ、銅の残渣を減少させ、そして、バリヤ腐食を減少させるように、ダマシン構造および犠牲層の除去の相対速度を変えることができる。バリヤ層は、ALCVDによって形成することができる。バリヤ層の材料は、WCNおよびTaNの1以上である。犠牲層は、TaN、TiNまたはWとすることができる。  (もっと読む)

(もっと読む)

パターン形成構造、パターン形成方法、デバイス及び電気光学装置、電子機器

【課題】パターン形成時に、微細パターンと他のパターンとの各々の高さを同じくすることにより、パターンを含む領域の上面に平坦領域を形成するバンク構造体、パターン形成方法、及び電気光学装置、電子機器を提供する。

【解決手段】機能液により形成するパターンに対応した凸部35が設けられた隔壁構造体であって、第1パターンに対応して設けられた第1凹部55と、第1パターンに接続され、かつ、第1パターンよりも幅が狭い第2パターンに対応して設けられた第2凹部56と、第1凹部55に少なくとも1以上設けられた凸部35と、を備えることを特徴とする。

(もっと読む)

電子回路を自己組織化させる方法及びその方法によって形成された回路

回路を組み立てる方法が、テンプレートを準備するステップと、半導体材料が該テンプレート上に自己組織化することを可能にするステップと、回路を形成するために、該半導体材料と該テンプレートとの間における接続の自己組織化を可能にするステップとを含む。  (もっと読む)

(もっと読む)

アルミニウム、銅、およびタングステンの構造の選択的ニッケルめっき

中間の半導体デバイス構造の上にニッケルを選択的にめっきする方法。この方法は、少なくとも一つのアルミニウムまたは銅の構造と少なくとも一つのタングステンの構造を有する中間の半導体デバイス構造を用意することを含む。アルミニウムまたは銅の構造とタングステンの構造のうちの一方はニッケルめっきされ、他方はめっきされないまま残る。アルミニウムまたは銅の構造またはタングステンの構造は、最初にニッケルめっきに対して活性化されてもよい。次いで、この活性化したアルミニウムまたは銅の構造または活性化したタングステンの構造は、無電解ニッケルめっき溶液の中に中間の半導体デバイス構造を浸漬することによってニッケルめっきされてもよい。めっきされていないアルミニウムまたは銅の構造またはめっきされていないタングステンの構造は、このめっきされていない構造を活性化し、そしてこの活性化した構造をニッケルめっきすることによって、後にニッケルめっきされてもよい。中間の半導体デバイス構造と同じく、アルミニウムまたは銅の構造とタングステンの構造をニッケルで同時にめっきする方法も開示される。 (もっと読む)

アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置並びに電子機器

【課題】 ドライプロセスとフォトリソエッチングを組み合わせた工程の回数を低減することができるアクティブマトリクス基板の製造方法等を提供することを目的とする。

【解決手段】 アクティブマトリクス基板20の製造方法において、第1方向又は第2方向のいずれか一方の配線42が交差部56において分断された格子パターンの配線40,42,46を基板P上に形成する第1工程と、交差部56及び配線40,42,46の一部上に絶縁膜と半導体膜30とからなる積層部を形成する第2工程と、積層部上に分断された配線42を電気的に連結させる導電層49、及び半導体膜30を介して配線42と電気的に接続される画素電極45を形成する第3工程と、を有する。

(もっと読む)

回路基板、電気光学装置、及び電子機器

【課題】 トランジスタ等の能動素子が安定に動作し、大画面化と長期にわたって安定した表示動作とを可能にする。

【解決手段】 陰極(222)と陽極(23)とに狭持され、基板(2)の上方に配置された電気光学素子と、電気光学素子を駆動する能動素子(24)と、陰極(222)及び陽極(23)のうち少なくとも一方と基板(2)との間に配置された誘電率が所定の値以下の絶縁材料からなる絶縁膜(283、284)とから電気光学装置(1)を構成する。

(もっと読む)

スタックされた有機メモリデバイス及びその製造及びオペレーション方法

本発明は、多層の有機メモリデバイス(10,24,28,34,54,58,74,78,100,700,704)を与え、非揮発性メモリデバイスとしてオペレートし得るし、その中に構築された複数のスタックされた及び/又はパラレルメモリを有する。複数セルと多層有機メモリコンポーネント(30,34,50,54,70,74)は、2あるいはそれ以上の電極(110,122,132,140,220,244,332,348,432,448,514,560,616,704,710)で形成され得るし、電極間(110,122,132,140,220,244,332,348,432,448,514,560,616,704,710)に選択的導電媒体(706,708)を有し、個々のセルを形成する。一方でパーティションコンポーネント(40,44,48,60,64,68,80,84,88)を、先に形成されたセルの上部に又は関連して追加のメモリセルをスタックすることを可能にするために利用する。メモリスタック(30,34,50,54,70,74)は、追加の層−追加のパーティションコンポーネントによって分離された各層を加えることによって形成され得るし、複数スタックが高密度メモリデバイスを与えるために併存して形成され得る。  (もっと読む)

(もっと読む)

電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置

【課題】 電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置を提供する。

【解決手段】 層を別にして交互される二層以上の導電層を含む電子装置において、導電層のうち、少なくとも何れか一層は、長手方向に沿って幅を別にする幅変動部を備えるが、幅変動部は、隣りの導電層との非交差部に形成されることを特徴とする薄膜トランジスタ構造体。また、基板の一面上に形成される薄膜トランジスタ層と、薄膜トランジスタ層と電気的疎通をなす一つ以上の画素を備える画素層と、を含み、薄膜トランジスタは、層を別にして交互される二層以上の導電層を含み、導電層のうち少なくとも何れか一層は、長手方向に沿って幅を別にする幅変動部を備えるが、幅変動部は、隣りの導電層との非交差部に形成されることを特徴とする平板ディスプレイ装置。

(もっと読む)

薄膜トランジスタの作製方法

【課題】 しかし、薄膜トランジスタを有する表示装置では、同一対象物、例えば同一絶縁膜のエッチング条件を最適化することが難しかった。これは、同一絶縁膜において、エッチングする絶縁膜の膜厚や面積が異なるためである。特に面積の小さなコンタクトホールは、エッチングする量がその他の開口部と異なる。

【解決手段】 上記課題を鑑み本発明は、第1のマスクを用いて、第1の領域の対象物をエッチングして広面積な開口部を形成し、第2のマスクを用いて、第2の領域の前記対象物をエッチングして微細な開口部、つまりコンタクトホールを形成することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 半導体素子の搭載されたで導電性基板に、導電性基板の表裏面の導通をとる高アスペクト比、小径の貫通孔を、高温プロセスを使用する事なく形成する。

【解決手段】 あらかじめその表面に半導体素子及び該半導体素子と繋がる電気接続部が作りこまれている、半導体基板またはガラス基板からなる導電性基板の所定位置に、少なくとも1つの貫通孔をレーザ等で形成し、該貫通孔の内側表面に蒸着重合法により絶縁層を形成し、該絶縁層の内側表面およびそれと連なる該貫通孔の開孔部周辺部に、無電解メッキ等により導電層を該電気接続部と繋がるように形成する事で、該電気接続部と基板の裏面あるいは側面との導通をとる。

(もっと読む)

ビア・ファースト・デュアルダマシン相互接続配線形成のための構造体充填方法

厚さが溶剤により容易に制御できる間隙充填底部反射防止膜を用いたビア・ファースト・デュアルダマシン相互接続構造体を形成する方法である。基板に塗布後、底部反射防止膜は低温焼成により部分硬化される。次に皮膜したウェハ上に溶剤を施し、膜と一定時間接触させて置く。底部反射防止膜の焼成温度と溶剤との接触時間により制御できる速さで溶剤が底部反射防止膜を除去しつつも、薄い底部反射防止膜を作り誘電体積層上に最適の光吸収特性は維持される。本方法の別の実施例では底部反射防止膜を充分除去し、ビアを単に部分充填し、続く処理工程でビア底部が保護されるようにしてもよい。溶剤はウェハから除去され、底部反射防止膜は高温焼成処理により完全に硬化される。次にウェハはフォトレジストにより被覆されトレンチパターンが露出する。使用される底部反射防止膜材によりトレンチパターン形成上、より平坦な表面形状が維持され、誘電体積層上に無機光吸収材層を設ける必要がなくなり、トレンチのエッチング工程時ビアの底部を保護し、溶剤を用いてビアの厚さを制御することにより境界問題の発生を防止する。 (もっと読む)

薄膜電子部品の製造方法および製造装置ならびに薄膜電子部品

本発明は、薄膜電子部品の製造方法およびこの方法を実施する装置に関する。また、本発明は、この方法に従って製造された薄膜電子部品に関する。まず、実質的に誘電性を有する基板上に、導電性材料から成るガルヴァニックに均一な最下段の導電層が形成され、この最下段の導電層から導電領域がガルヴァニックに相互に分離して、電極パターンが形成される。この電極パターン上には、薄膜部品に必要とされる上部の不活性層または活性層を1層または数層形成することが可能である。本発明によれば、この最下段の導電層が分離することによる電極パターンの形成は、ダイカットエンボス加工に基づく切断作業を最下段の導電層に行うことによる。すなわち、切断作業に使用する切断部材の浮彫りが、基板上に永久変形が生じさせ、同時に、導電層から、ガルヴァニックに相互に分離した導電領域に至る領域をエンボス加工する。本発明は、ロールツーロール方式における薄膜部品の製造に適している。

(もっと読む)

(もっと読む)

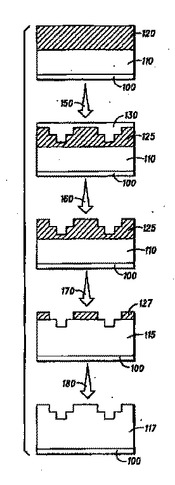

インプリント・リソグラフィによる単一デュアルダマシン製法

インプリント・リソグラフィと共に多段構造を有するテンプレートを用いるデュアルダマシン構造の製造方法の一例は、多段構造を有するリソグラフィ用テンプレート(130)をレジスト層(120)と接触するように配置するステップ(ステップ150)と、テンプレート(130)に圧力を加えることによりレジスト材料(120)がテンプレート(130)のレリーフパターン内に流れ込み、パターン化されたレジスト層(125)が形成されるステップと、そのパターン化されたレジスト層(125)を必要に応じて硬化するステップと、テンプレート(130)をパターン化されたレジスト層(125)から取り外すステップ(ステップ160)と、及びパターニング層(117)にビアやトレンチを作製するためパターン化されたレジスト層(125)をエッチングするステップ(ステップ170,180)とからなる。開示された特徴や仕様は、デュアルダマシン構造や他の多段構造の作製を改良したり、他の方法で最適化したりするため、様々に制御したり、設定したり、適合させたり、他の方法で部分的に変更したりしてもよい。  (もっと読む)

(もっと読む)

フリップチップ用高性能シリコンコンタクト

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

221 - 240 / 240

[ Back to top ]