Fターム[5F033HH13]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Au、Au合金 (1,453)

Fターム[5F033HH13]に分類される特許

141 - 160 / 1,453

半導体デバイス

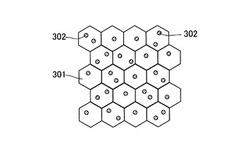

【課題】応力による半導体回路の特性劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体は、半導体基板の厚み方向に設けられた微細孔を満たし、第1結晶組織301と第2結晶組織302とを含むナノコンポジット結晶構造を有する。ナノコンポジット結晶構造において、第1結晶組織301及び第2結晶組織302の少なくとも一方は、ナノサイズである。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の接続孔側壁の寸法制御を高精度に且つ低コストで行うことができる半導体装置を提供する。

【解決手段】半導体装置1は、基材10の主面を被覆し、下部電極11の上面に達する接続孔12hを有する絶縁膜12を備える。絶縁膜12の膜密度は、基材10の主面から絶縁膜12の厚み方向に離れるに従って低減する。接続孔12hの内径は、絶縁膜12の膜密度の低減に伴って拡大する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置の製造方法

【課題】金属マスクを形成する工程を含む半導体装置の製造方法において、金属片が支持基板に付着することを防止する。

【解決手段】この製造方法は、支持基板10の表面10aに貼付された半導体ウェハ12上にネガレジストを塗布し、該ネガレジストを露光することにより所定のパターンを有するレジスト18を形成するレジスト形成工程と、半導体ウェハ12上にメッキ処理を施すことにより金属マスク20を形成したのちレジスト18を除去する金属マスク形成工程と、金属マスク20を介して半導体ウェハ12にエッチングを施すことにより、貫通孔12dを形成するエッチング工程と、金属マスク20を除去したのち、貫通孔12dの内面及び半導体ウェハ12の裏面12bに金属膜26を形成する金属膜形成工程と、半導体ウェハ12を支持基板10から取り外す取外し工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】基板に形成されたビアホール内のメタライズを改善すること。

【解決手段】本半導体装置の製造方法は、SiCを材料とする基板10を備える半導体装置100の製造方法であって、フッ化炭素を含むエッチングガス及びマスク14を用いて基板10の裏面をエッチングし、基板10の裏面から表面に向かって開口面積が次第に小さくなるテーパ形状を有する第1領域22を形成する第1工程と、次いで、フッ化硫黄を含むエッチングガス及びマスク14を用いて第1領域22の内側をエッチングし、第2領域24を形成する第2工程とを有し、基板10の表面に対する第2領域24の内壁面の傾斜角は、基板10の表面に対する第1領域22の内壁面の傾斜角より大きいことを特徴とする。

(もっと読む)

半導体装置

【課題】ディッシング及び埋め込み不良のないパッド構造を短時間で安定して形成する。

【解決手段】基板100上に形成された第1の絶縁膜108Bに、複数のパッド配線109pを含むパッドが形成されている。第1の絶縁膜108B上に、前記パッドの少なくとも一部分の上に位置する開口部を有する第2の絶縁膜110が形成されている。複数のパッド配線109pのうち互いに隣り合う配線同士を電気的に接続するように配線接続部109qが設けられている。各パッド配線109pの幅W1は、各パッド配線109pの高さよりも小さく且つ配線接続部109qの幅W3よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】基板に形成されたビアホール内のメタライズを改善すること。

【解決手段】本半導体装置の製造方法は、SiCを材料10とする基板を備える半導体装置の製造方法であって、フッ化炭素を含むエッチングガス及びマスク14を用いて基板10の裏面をエッチングし、基板10の表面から裏面に貫通するビアホール20を形成する工程を有し、ビアホール20成する工程は、基板10の裏面から表面に向かって開口断面積が次第に小さくなるテーパ形状を形成する工程であり、かつエッチング条件は、誘導結合プラズマ方式のドライエッチングを含み、ガス流量が、フッ化炭素=10〜200sccm、ガス圧力が、Press=0.1〜10.0Pa、誘導結合プラズマパワーが、ICP=100〜5000W、バイアスパワーが、Bias=10〜1000W、であることを特徴とする。

(もっと読む)

マスクおよびその製造方法、半導体ウエハ

【課題】半導体ウエハ面内における金属配線の抵抗分布のばらつきを抑え、得られるデバイスの特性や精度を面内で均一化させることが可能なマスクを提供する。

【解決手段】本発明のマスクは、金属配線を有するデバイス10を基板2の一面上に多数形成する際に、該基板の一面に対向配置されて用いられるマスクであって、個々の前記デバイスが配される前記基板上の位置に応じて、それぞれのデバイスが有する前記金属配線に対応する部位の形状を変えたこと、を特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】パッシベーション膜にクラックを生じさせるか否かを容易に判定できる構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、下部電極23の上面に達する接続孔30hを持つパッシベーション膜30を備える。パッシベーション膜30は、接続孔30hを除いて下部電極23の周縁部を含む領域を被覆する。下部バリアメタル膜31は、下部電極23とパッシベーション膜30の凸状部分30bとを被覆するように形成されている。バンプ電極35から離れた領域でパッシベーション膜30に形成されている段差部分を被覆するように金属膜パターン31Tが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

配線基板の製造方法

【課題】コンタクトホールを、生産性良く、低コストで、且つ信頼性良く製造する配線基板の製造方法を提供する。

【解決手段】基板1に第1電極3及び第2電極7が形成される。第1電極3及び第2電極7を連通するように形成された微細穴の側壁部及び底部に、導電膜9を形成してコンタクトホール2を形成する。この配線基板100の製造する際に、微細穴を形成する微細穴形成工程において、微細穴の側壁部の開口端側に相対的に浅い溝からなる第1溝領域4が形成され、微細穴の側壁部の底部側に相対的に深い溝からなる第2溝領域5が形成される。このように区分けした溝領域4,5のうち、第2溝領域5に導電性材料を含有する液体を付与して、導電膜9を形成する。

(もっと読む)

金属膜形成装置

【課題】処理雰囲気を適切に制御しつつ、金属混合液を用いて基板上に金属膜を適切に形成する。

【解決手段】金属膜形成装置1の処理容器10の内部は、不活性ガスの大気圧雰囲気又は減圧雰囲気に切り換え可能になっている。処理容器10の内部には、ウェハWを保持するスピンチャック20と、ウェハWの側方を囲むように設けられたカップ体31と、ウェハW上に金属混合液を吐出する塗布ノズル60と、ノズル駆動部65の動力を塗布ノズル60に伝達するノズル伝達部64と、塗布ノズル60を待機させるノズルバス66とが設けられている。処理容器10の外部には、水平方向より所定の角度で傾斜した方向に沿って、スピンチャック20とノズルバス66との間で塗布ノズル60を移動させるためのノズル駆動部65が設けられている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】研磨工程を含む新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、絶縁膜を形成する工程と、絶縁膜に、第1の深さを有するダミー溝と、第1の深さよりも深い第2の深さを有する配線溝と、配線溝の底面に配置されるビアホールとを形成する凹部形成工程と、ダミー溝内、配線溝内、ビアホール内、及び絶縁膜上方に、導電材を堆積させる工程と、絶縁膜上方の導電材を研磨除去する工程とを有する。

(もっと読む)

パターン形成方法及びパターン形成装置

【課題】、基材の表面を冷却したまま溶媒を除去しない場合に比べ、パターンが精度良く形成されるパターン形成装置を提供する。

【解決手段】基材20を冷却する基材冷却手段22と、前記基材冷却手段によって冷却された前記基材の表面に、パターン形成材料、及び溶媒を含む組成物18を付与して該組成物のパターンを描画するパターン描画手段24と、前記基材の表面に描画された前記組成物のパターンから該基材を冷却したまま前記溶媒を除去する溶媒除去手段26と、を有するパターン形成装置10。溶媒除去後、加熱を行って分散剤を除去する加熱手段28を備えてもよい。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

パターン形成方法及びパターン形成装置並びにパターン構造

【課題】基材の表面にバルジを誘導するためのパターンを形成せずに組成物の液滴を付与して線状パターンを形成する場合に比べ、線状パターンに生じるバルジの方向が制御されるパターン形成方法を提供する。

【解決手段】基材の表面に組成物の液滴を線状に付与して線状パターン12A,12Bを形成する線状パターン形成工程と、線状パターンを形成すると共に又は線状パターンを形成する前に、液滴を付与して、前記線状のパターンの幅方向における片側の縁で接触するバルジ誘導用パターン10A,10B,10Cを形成するバルジ誘導用パターン形成工程と、を含む。バルジ誘導用パターンを形成した後、線状パターンを形成することが望ましく、予めパターン形成領域外に組成物の液滴を付与してバルジ発生位置を確認するためのバルジ確認用パターンを形成する工程をさらに含んでもよい。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】Cuを主要な成分とする再配線に設けられた外部接続用Auパッドの剥離を抑制する。

【解決手段】Cu膜15aの上部にNi膜15bを積層した2層膜からなる再配線15の表面には、ワイヤが接続されるパッド18が形成されている。パッド18は、Ni膜19aの上部にAu膜19bを積層した2層膜からなり、再配線15の上面および側面を覆うように一体形成されている。これにより、再配線15とパッド18の接触面積が大きくなるので、パッド18が再配線15から剥がれ難くなる。

(もっと読む)

配線構造の形成方法および配線構造

【課題】太い幅の配線溝と細い幅の配線溝をCuの電解メッキで充填する際に、アンダープレートの発生を抑制し、化学機械研磨後におけるディッシングの発生を抑制する。

【解決手段】表面の第1の領域に縦/横比小さい第1の配線溝22Aが形成され、表面の第2の領域に縦/横比が大きい第2の配線溝22Bを形成された絶縁膜の表面上にレジスト膜R1を形成し、第1の領域を露出する第1のレジスト開口部R1Aを形成する工程と、レジスト膜をマスクに電解メッキを行い、第1の配線溝を第1の配線パタ―ン25Aで充填する工程と、第2の領域を露出する第2のレジスト開口部を形成する工程と、レジスト膜をマスクに電解メッキを行い、第2の配線溝を第2の配線パタ―ンで充填する工程と、レジスト膜を除去し、第1の配線パタ―ンおよび第2の配線パタ―ンを、それぞれの表面が絶縁膜の表面に一致するように、化学機械研磨により平坦化する工程と、を含む。

(もっと読む)

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体

装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製

する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上

に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄

膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

141 - 160 / 1,453

[ Back to top ]