Fターム[5F033HH13]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Au、Au合金 (1,453)

Fターム[5F033HH13]に分類される特許

161 - 180 / 1,453

半導体装置

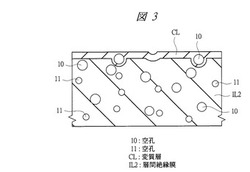

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】ポーラスLow−k膜からなる第2ファイン層の層間絶縁膜IL2内の空孔10および空孔11の平均径を1.0nm以上1.45nm未満とすることで、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、製造コストの増加を抑制可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板部10、誘電体膜22、再配線24、上部電極25、絶縁膜26、及び外部接続端子28を有する。半導体基板部10は、回路が形成され、回路にそれぞれ接続される下部電極15、上部電極パッド16、接続パッド17、18を上面に有する。誘電体膜22は、下部電極15を被い、上部電極パッド16、接続パッド17、18の上面に達する開口部を有する。再配線24は、一部の接続パッド17、18に電気的に接続される。上部電極25は、誘電体膜22を介して下部電極15の上面に対向して配置され、上部電極パッド16に接続され、再配線24を含む。絶縁膜26は、誘電体膜22、再配線24、及び上部電極25を被う。外部接続端子28は、絶縁膜26を貫通し再配線24に接続され、絶縁膜26の上面から露出する。

(もっと読む)

導電性素子およびその製造方法、配線素子、情報入力装置、表示装置、ならびに電子機器

【課題】優れたスループットを実現できる導電性素子を提供する。

【解決手段】導電性素子は、第1の波面および第2の波面を有する基体と、第1の波面上に形成された導電層とを備える。導電層は、導電パターン部を形成し、第1の波面および第2の波面が、0≦(Am1/λm1)<(Am2/λm2)≦1.8(但し、Am1:第1の波面の振動の平均幅、Am2:第2の波面の振動の平均幅、λm1:第1の波面の平均波長、λm2:第2の波面の平均波長)の関係を満たす。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

配線回路基板及びその製造方法

【課題】配線回路基板において、コンタクト抵抗の上昇を抑制し、熱応力による断線を防止することのできるコンタクト構造を提供する。

【解決手段】 配線回路基板は、第1配線層(5)、第2配線層(7)、及び前記第1配線層と前記第2配線層を電気的に接続するコンタクト配線(6)を有する。前記コンタクト配線は、前記第1配線層のコンタクト面を被覆する第1被覆部(6a)と、前記第2配線層のコンタクト面を被覆する第2被覆部(6c)と、前記第1被覆部と前記第2被覆部の間に延びるプラグ部(6b)を有する。前記第1被覆部、前記プラグ部、及び前記第2被覆部は、同一の導電性材料で一体的に形成された内部に界面のないコンタクト配線である。

(もっと読む)

電子回路付き基板及びその製造方法、並びに混合型電子回路形成キット

【課題】DNA又はDNA−脂質複合体を用いた簡易な方法により、基板上に導電性パターンを、画像流れを抑制しながら安定して形成できる電子回路付き基板の製造方法を提供する。

【解決手段】基板上に、DNA又はDNA−脂質複合体を含む溶液を描画することによって電子回路パターンを形成する工程と、前記電子回路パターンが形成された基板を多価金属イオン溶液に浸漬することによって、前記電子回路パターンにおいて、前記DNA又は前記DNA−脂質複合体と前記多価金属イオンとの錯体を形成する工程と、形成された錯体中の金属イオンを還元することによって、前記電子回路パターンを導電性パターンとする工程と、を有する電子回路付き基板の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】積層する基板の電極端子同士の間での接合不良を防止できる3次元集積化技術を提供する。

【解決手段】基板1上にトランジスタ6と多層配線2、絶縁膜3を形成する。絶縁膜3に配線が露出するように開口部4を形成する。開口部内を含む絶縁膜上に、銅などからなる複数の導電体微粒子5を含む有機溶剤を回転塗布する。第1の熱処理により溶剤と有機成分を除去した後、CMP法で外側部分の導電体微粒子を除去する。開口部内に導電体微粒子から構成された電極端子9が形成される。第2の基板51の貫通電極52を開口部に合わせ、加圧して押し合わせる。第1の熱処理より高温の第2の熱処理を行い、導電体微粒子を部分的に溶融させ、貫通電極と接合する。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

半導体装置およびその製造方法

【課題】パッド電極に荷重または衝撃力が加わっても、周囲の絶縁膜にクラックが発生しにくい構造の半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、平面形状が、略円形、略楕円形、少なくとも1つの内角が90°より大きい略多角形、および、少なくとも1つの角部に面取りや丸みをつけた略多角形、ならびに、これらの少なくとも一部分を含む形状の組合せからなる群から選ばれた平面形状となるような凹部を形成する凹部形成工程と、前記凹部の内面に少なくとも一部を被覆する下敷膜を形成する下敷膜形成工程と、絶縁膜で覆われた前記凹部に導電性の電極材質を埋め込むパッド部形成工程とを含み、前記凹部形成工程は、第1の凹部を形成する工程と、前記第1の凹部の一部分においてさらに深く凹む第2の凹部を形成する工程とを含む。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

積層構造体及びその製造方法、並びに多層配線基板、アクティブマトリクス基板及び画像表示装置

【課題】インクジェット法を用いた場合でも高いスループットで微細な導電層を有する積層構造体を製造可能な積層構造体の製造方法、並びに積層構造体、多層配線基板、アクティブマトリクス基板及び画像表示装置を提供する。

【解決手段】基板上に、同一パターンの高表面エネルギー部40を一定の間隔で周期的に配列しておき、インクジェット装置の主走査方向(X軸方向)における吐出ノズル1,2の間隔を、高表面エネルギー部40のパターン間隔と一致させて選択的に機能液の液滴dを滴下してソース電極230、ソース電極線290、ドレイン電極240となる導電層を形成する。

(もっと読む)

充填用基材及びそれを用いた充填方法

【課題】充填時の溶融温度が低く、凝固後は高い融点を確保することができ、しかも、作業操作性に優れた充填用基材及びそれを用いた充填方法を提供すること。

【解決手段】充填用基材5は、第1金属層21と第2金属層22とを含む金属層2を支持基体1の一面上に設けた構造になっている。第1金属層21は、その融点よりも低い温度で溶融可能なナノ金属粒子の集合したものでなり、第2金属層22は、その融点が第1金属層21の融点よりも低い金属粒子の集合したものでなる。充填用基材5の一面側を、微細空間30の開口する基板3の一面上に重ねる。そして、充填用基材5を加熱し、かつ、加圧F1して、金属層2の溶融物を微細空間30内に充填する。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置において、貫通電極によって被覆された貫通孔の内部を充填する保護層にクラック等が発生する不具合を防止する。

【解決手段】

貫通電極9を被覆するとともに、貫通孔6内を充填する保護層10を備える半導体装置1において、保護層10が複数層11、12からなり、複数層の保護層のうち最も半導体基板2の一面2aに近い層が、少なくとも貫通電極の底面9aと側面9bの交差部を被覆し、かつ、ポジ型感光性樹脂を用いて形成されることを特徴とする半導体装置を提供する。

(もっと読む)

パターン形成体の製造方法、機能性素子の製造方法および半導体素子の製造方法

【課題】本発明は、高精細なパターニングが可能なパターン形成体の効率的な製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に形成され、表面が疎水性を示す疎水性層上にフォトレジストパターンを形成するフォトレジストパターン形成工程と、上記フォトレジストパターンが形成された上記疎水性層の表面にエネルギーを照射して親水化し、親水性領域を形成する親水化工程と、上記フォトレジストパターンを剥離し、上記疎水性層表面に、上記親水性領域と上記親水化工程にて上記フォトレジストパターンで覆われていた疎水性領域とがパターン状に形成された親疎水パターンを形成するフォトレジストパターン剥離工程とを有することを特徴とするパターン形成体の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の半導体素子を積層させる半導体装置を低コストで製造する手段を提供する。

【解決手段】半導体装置31は、回路基板1上に第1の半導体素子10が実装されており、第1の半導体素子10の第1の電極パッド14上のハンダバンプ17に第2の半導体素子20の接続端子26が接合されている。第1の半導体素子10の第2、第3の電極パッド15,16はワイヤ18で回路基板1に電気的に接続されている。第1の半導体素子10と第2の半導体素子20の間の距離H0は、背高の接続端子26によって、ワイヤ18のループ高さH1以上になっている。

(もっと読む)

貫通孔配線基板の製造方法

【課題】めっき反応速度を調整することでめっき未着を防ぐことが可能な貫通孔配線基板の製造方法を提供することである。

【解決手段】微小デバイスを構成する貫通孔配線基板の製造方法であって、基板40の両表面を貫通する貫通孔41を形成する工程と、貫通孔41の少なくとも内表面にNiめっきを成長させる工程と、を備え、貫通孔41の少なくとも内表面にNiめっきを成長させる工程では、Niめっきの析出レートを50nm/min未満にしてめっきを成長させる。

(もっと読む)

半導体チップおよびこれを用いた半導体装置

【課題】接続導体との間のはんだ接合部の信頼性を確保する。

【解決手段】ジンケート法による無電解めっき法を用いて、半導体チップ1の表面側のAl電極3の上にNiめっき層5が形成される。Al電極3の上には、選択的にNiめっき層5が析出されるため、周辺耐圧構造4部分には、Niめっき層5は形成されない。また、形成されるNiめっき層5は、所定の厚さに均一に形成することができる。続いて、Niめっき層5の上にAuめっき層6が形成される。無電解めっき法を用いることによって、Auめっき層6もNiめっき層5と同様に、Niめっき層5の上に選択的、かつ均一に形成される。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】基板を薄板化しても基板の反りを抑制でき、耐熱性、機械特性に優れた絶縁膜で保護された半導体素子及びその製造方法を提供する。

【解決手段】基板1の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板の表面に、芳香族テトラカルボン酸及び芳香族テトラカルボン酸二無水物から選ばれる1種以上のアシル化合物を、前記芳香族ジアミンよりも1モル%以上多く反応して得られるポリアミド酸を含むポリイミド前駆体組成物を塗布し、イミド化して絶縁膜3を形成し、第1表面電極2及び絶縁膜3が少なくとも形成された基板1を、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

161 - 180 / 1,453

[ Back to top ]