Fターム[5F033HH13]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Au、Au合金 (1,453)

Fターム[5F033HH13]に分類される特許

101 - 120 / 1,453

半導体装置

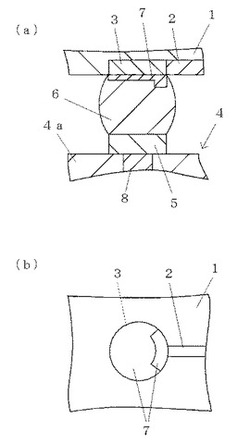

【課題】 半導体素子の電極がはんだバンプを介して接続パッドに電気的に接続されているとともに、エレクトロマイグレーションが効果的に抑制された半導体装置を提供する。

【解決手段】 半導体基板1の電極3の外周の一部に電子回路2が直接に接続されてなる半導体素子と、半導体素子の電極3と対向して配置された接続パッド5を備える配線基板4と、電極3と接続パッド5との間に介在して、電極3および接続パッド5に接合されたはんだバンプ6とを備え、電極3とはんだバンプ6との界面に沿って、電極3の外周の電子回路2が接続されている一部に接した部分において他の部分よりも厚いニッケル層7が介在している半導体装置である。ニッケル層7の厚みの差に応じた電気抵抗差によって、半田バンプ6に流れる電流の電流密度を均一化し、電流の集中によるマイグレーションを抑制できる。

(もっと読む)

配線パターン

【課題】コンタクトホールを起点とした絶縁膜の剥がれの伸展を防ぐことができる配線パターンを得る。

【解決手段】半絶縁性GaAs基板1上に、配線メタル2が設けられている。配線メタル2上に金メッキ4が設けられている。金メッキ4は、ボンディングパッド部5と配線部6を有する。ボンディングパッド部5及び配線部6を覆うように金メッキ4上に連続してSiN膜7が設けられている。ボンディングパッド部5上においてSiN膜7にコンタクトホール8が設けられている。ボンディングパッド部5と配線部6の間において金メッキ4に段差が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】スルーホールの微細化による半導体装置の高集積化と、スルーホール内に埋め込まれる導体のカバレッジ性と、を両立させる。

【解決手段】半導体装置は、下層配線2と、下層配線2上に形成され、下層配線2の上面を露出させる開口31を有する第1絶縁膜(例えば、有機絶縁膜3)と、第1絶縁膜上に形成され、スルーホール5が形成された第2絶縁膜(例えば、無機絶縁膜4)とを有する。半導体装置は、更に、スルーホール5に埋め込まれ、下層配線2と電気的に接続された導体9を有する。開口31は、上側に向けて拡径するテーパー形状に形成されている。スルーホール5の側壁5aの少なくとも下端は、開口31の側壁31aを構成する傾斜面の上に位置している。

(もっと読む)

半導体装置

【課題】3次元的に積層された複数の半導体チップを有する半導体装置の製造歩留まりを向上できる技術を提供する。

【解決手段】半導体基板1の第2面1bからパッド3に達する貫通電極17が形成されている。貫通電極17の内部にある貫通空間は、第1孔7および第1孔7よりも孔径の小さい第2孔11によって構成されている。半導体基板1の第2面1bから半導体基板1を貫通して層間絶縁膜2の途中まで第1孔7が形成されている。そして、第1孔7の底部から層間絶縁膜2を貫通してパッド3に達する第2孔11が形成されている。このとき、半導体基板1の第1面1aに形成されている層間絶縁膜2は、第1孔7の底面と半導体基板1の第1面1aとの段差を反映して段差形状になっている。すなわち、第1孔7の底面とパッド3間に存在する層間絶縁膜2の膜厚がその他の場所の層間絶縁膜2の膜厚よりも薄くなっている。

(もっと読む)

バリア層の形成方法

【課題】 本発明は、以上の点に鑑み、異種金属からなる導電層間に介在されるような場合でも十分なバリア性能を発揮し得るバリア層を生産性よく形成することができるバリア層の形成方法を提供する。

【解決手段】 バリア層BMは、処理対象物Wを一方の導電層CL1を有するものとし、この処理対象物と、例えばTi製のターゲット2とを真空処理室1a内に配置し、真空処理室内に希ガスを導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして一方の導電層表面に第1金属層を形成し、真空処理室内に酸素ガス及び窒素ガスを含むガスを導入してプラズマ雰囲気を形成し、第1金属層の表面を酸窒化処理すると共に、ターゲットをもプラズマ雰囲気に曝して当該ターゲット表面を酸窒化し、真空処理室内に希ガスを更に導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして酸窒化処理された表面に第2金属層を形成してなる。

(もっと読む)

三次元積層構造を持つ半導体装置の製造方法

【課題】 三次元積層構造を持つ半導体装置において、積層された半導体回路層間の積層方向の電気的接続を、埋込配線を使用して容易に実現する半導体装置の製造方法を提供する。

【解決手段】 第1半導体回路層1aの半導体基板11の表面に、絶縁膜14で内壁面が覆われたトレンチ13を形成し、トレンチ13の内部に導電性材料を充填して導電性プラグ15を形成する。次に、トレンチ13とは重ならないように所望の半導体素子を基板11の表面または内部に形成し、その上に層間絶縁膜19を介して多層配線構造30を形成してから、多層配線構造30の表面にプラグ15に電気的に接続されたバンプ電極37を形成する。そして、電極37を用いて基板11を支持基板40に固定してから基板11をその裏面側から選択的に除去し、絶縁膜14を基板11の裏面側に露出させる。基板11の裏面側に露出せしめられた絶縁膜14を選択的に除去してプラグ15を露出させ、その端に電極42を形成する。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

機能性膜の形成方法、積層構造体、多層配線基板、アクティブマトリクス基板及び画像表示装置、並びに図面製造装置、インクジェット装置、積層構造体製造装置

【課題】インクジェット法により微細なパターンでショートさせることなく機能性膜を形成することができる機能性膜の形成方法を提供する。

【解決手段】被印刷面上に、低表面エネルギー領域を隔てて隣接する高表面エネルギー領域231,241を有する表面において、高表面エネルギー領域231,241の形状及び機能液の着弾範囲に基づいて、高表面エネルギー領域231(241)に機能液を供給する際に該機能液が高表面エネルギー領域231(241)のみに触れるための滴下許容範囲231A(241A)を決定し、ついで滴下許容範囲231A(241A)内の任意の位置を高表面エネルギー領域231(241)に対する機能液の滴下位置231C(241C)として決定し、高表面エネルギー領域231(241)の滴下位置231C(241C)にインクジェット法を用いて選択的に機能液を供給して所定パターンの機能性膜を形成する。

(もっと読む)

バンプオンリード相互接続を形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】半導体ダイの表面上に形成された複数の複合バンプを有する、半導体ダイを提供するステップであって、前記複合バンプは、可融性部分および非可融性部分を有する、ステップと、基板を提供するステップと、エスケープルーティング密度を増加させるための平面図から、伝導性トレースと平行な縁を有する相互接続部位を伴って前記基板上に複数の伝導性トレースを形成するステップであって、前記複合バンプは、前記相互接続部位よりも幅広い、ステップと、前記可融性部分が前記相互接続部位の頂面および側面を覆うように、前記複合バンプの前記可融性部分を前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記複合バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

導電性金属ペースト

【課題】150℃〜250℃の範囲に選択する温度で焼結処理を施すことで、膜厚が厚く、利用する金属の3倍以下の体積固有抵抗率を有する導電体層を高い再現性で作製する用途に十分に適合する、バインダー樹脂成分を含有していない、新規な構成の導電性金属ペーストを提供する。

【解決手段】導電性金属ペースト中に含有される、金属微細粉末の体積比率Vmetal-particle、金属ナノ粒子の体積比率Vnano-particle、その被覆剤分子層の形成に利用される被覆剤分子の体積比率Vcoating-molecule、分散溶媒の体積比率Vsolventについて、比Vmetal-particle:(Vnano-particle+Vcoating-molecule+Vsolvent)を1:1〜1:4.6の範囲に、比(Vnano-particle+Vcoating-molecule):Vsolventを1:0.7〜1:3の範囲に、比(Vmetal-particle:Vnano-particle)を90:10〜60:40の範囲に選択する。

(もっと読む)

固定用構造および嵌合構造

【課題】チップの縁領域は、膨張係数が異なることによって、温度サイクル中に、TC応力とも称される特定の負荷を受けることが多い。これらの縁領域は特にTC応力を受け易いため、同領域内において様々な不良が生じる可能性がある。これによって、実際のデバイスにおける信頼性のリスクが増大する可能性がある。

【解決手段】半導体デバイスの金属構造210のための固定用構造200は、オーバーハング形状の側壁230を少なくとも1つ含んだ固定用凹部構造220を含んでいる。上記金属構造210は、少なくとも部分的に上記固定用凹部構造220内に配置されている。

(もっと読む)

メッキ金属膜基板とその製造方法、及び半導体装置

【課題】一度の成膜で、所望の平面パターンと膜厚分布を有するメッキ金属膜を成膜することが可能なメッキ金属膜基板とその製造方法を提供する。

【解決手段】メッキ金属膜基板1は、基板上に少なくとも1層の給電金属膜20と少なくとも1層のメッキ金属膜30とを順次有し、少なくとも1層の給電金属膜20は、少なくとも1層のメッキ金属膜30の下地が相対的に高抵抗な高抵抗部20Hと、メッキ金属膜30の下地が相対的に低抵抗な低抵抗部20Lとを有するものである。

(もっと読む)

電力増幅装置及び連結電力増幅装置

【課題】ソース電極からビアホールまでの距離をさらに短くし、インダクタンスの影響をできる限り低下させる増幅装置を提供する。

【解決手段】電力増幅装置は、接地のためのビアホールと接続する接地部と、接地部を接続するソース電極接地導体と、ソース電極接地導体に連結したソース電極と、ソース電極接地導体に接触しない内側ソース電極と、ドレイン電極と、ゲート電極と、内側ソース電極と接地部とを直接接続する接地ブリッジと、を備える。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

半導体デバイス用基板洗浄液及び洗浄方法

【課題】基板表面を腐食することなく微粒子付着による汚染、有機物汚染及び金属汚染を同時に除去することができ、しかも水リンス性も良好で、短時間で基板表面を高清浄化することができる半導体デバイス用基板洗浄液を提供する。

【解決手段】

半導体デバイス製造における化学的機械的研磨工程の後に行われる、半導体デバイス用基板の洗浄工程に用いられる洗浄液であって、以下の成分(A)〜(D)を含有してなる半導体デバイス用基板洗浄液。

(A)有機酸

(B)スルホン酸型アニオン性界面活性剤

(C)ポリビニルピロリドン及びポリエチレンオキシド−ポリプロピレンオキシドブロック共重合体から選ばれる少なくとも1種の高分子凝集剤

(D)水

(もっと読む)

半導体装置

【課題】 製造が容易でかつ絶縁性に優れ、平坦な上面(表面)を持つパッシベーション構造を備えた配線構造を、低コストかつ短リードタイムで形成する、半導体装置を提供する。また、配線抵抗が小さくボンディング耐性が高い配線構造を提供する。

【解決手段】 所望の素子領域の形成された基板表面に形成された配線層と、前記配線層表面を覆う層間絶縁膜と、前記層間絶縁膜表面全体を覆うように形成された窒化シリコン膜と、前記窒化シリコン膜の上層に形成された最上層メタルとしての金層からなるメタル配線層と、前記窒化シリコン膜と前記メタル配線層との間に形成されたバリア層と、前記メタル配線層上に形成されたポリイミドからなる平坦化絶縁膜とを含み、前記バリア層と前記配線層は、前記窒化シリコン膜と前記層間絶縁膜に形成されたスルーホールを通じて接続されており、前記平坦化絶縁膜が一部領域で除去せしめられ、前記メタル配線層にボンディングがなされていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

101 - 120 / 1,453

[ Back to top ]