Fターム[5F033KK07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842)

Fターム[5F033KK07]の下位に属するFターム

Fターム[5F033KK07]に分類される特許

201 - 220 / 751

半導体装置

【目的】プロービング試験での導電パッド下に配置された金属配線上の絶縁膜のクラック発生を抑制することが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、導電パッドと、前記導電パッド上に配置され、前記導電パッドの一部が露出するように開口領域が形成された第1の絶縁膜と、前記導電パッドの下方に配置された第2の絶縁膜と、銅(Cu)を用いた配線を有し、前記第2の絶縁膜を介して前記導電パッドの下方に配置され、前記開口領域と重なる領域での最上層における前記配線の最大配線幅w(nm)と前記配線の被覆率R(%)とがある条件を満たすように配置された少なくとも1層の配線層と、を備えたことを特徴とする。

(もっと読む)

半導体基板と半導体基板の製造方法および半導体パッケージ

【課題】高信頼性の貫通電極を有する半導体基板と半導体基板の製造方法を提供することを目的とする。

【解決手段】第1絶縁層(2)を介して第1配線層(3)が形成され、貫通孔(4)の内周に第2配線層(5)を形成し、貫通孔(4)は、第1の開口部(4a)と、第1の開口部(4a)よりも開口面積が小さい第2の開口部(4b)で形成され、第2の開口部(4b)に第3配線層(103a)を形成するとともに、第3配線層(103a)を第1の開口部(4a)よりも先に形成することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 信号線の形成位置に関わらず、信号線とMIM構造のキャパシタ11との間で発生する寄生容量が抑制できるようにする。

【解決手段】 MIM構造のキャパシタ11と、絶縁膜12a,12bを介してMIM構造のキャパシタ11を挟む、少なくとも一対の遮蔽部13a,13bとを備える。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

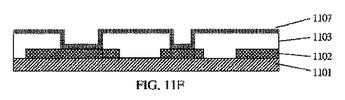

光焼結及び/またはレーザー焼結を強化するためのバッファ層

電子部品間に電気を伝えるための配線を製造するために、基板上に導電線を堆積させる。基板上にパターン形成された金属層が形成され、次いで低熱伝導率を有する材料の層が、パターン形成された金属層及び基板上に被覆される。低熱伝導率を有する材料の層を通るビアが形成されることによって、パターン化された金属層の一部が露出される。次いで、導電性インクの膜が低熱伝導率を有する材料の層上及びビア内に被覆されることによって、パターン化された金属層の前記部分が被覆され、その後焼結される。パターン化された金属層の部分に被覆された導電性インクの膜は、低熱伝導率を有する材料の層上に被覆された導電性インクの膜ほど、焼結由来のエネルギーを吸収しない。低熱伝導率を有する材料の層は、ポリイミドなどのポリマーであり得る。  (もっと読む)

(もっと読む)

半導体装置

【課題】小型化及び利得等の高周波性能の向上を図ることができる半導体装置として、実用的な高周波増幅器を実現する。

【解決手段】トランジスタ101の入力端に配線層103がコプレーナ線路で接続されており、配線層103には、開放端を有する配線層104が二つの方向に分岐されて終端され、配線層103上の位置から、高周波信号が入出力される。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

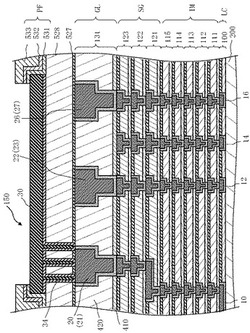

半導体集積回路装置の製造方法

【課題】Cuダマシン多層配線構造におけるセミ・グローバル配線の形成方法において、ダマシン配線構造を形成する際、ドライ・エッチングによりビア底のエッチ・ストップ絶縁膜を除去した後、ビア底表面上のカーボン系堆積物等を抑制する為に、窒素プラズマ処理を行うことが一般的である。その後、連続放電によって窒素プラズマ除電を行ってウエハ搬送するシーケンスを実行すると、ビア・チェーン終端部にて、ある閾値以上の長さを有するパッド引き出し配線に接続された終端部のビア底で、Cuえぐれが発生ことが、本願発明者らの検討によって明らかとなった。

【解決手段】本願発明は、ダマシン・セミ・グローバル配線等のビア・ホール形成工程において、ビア底エッチ・ストップ膜に対するドライ・エッチング処理後、同処理室内で行われる窒素プラズマ処理に引き続いて、アルゴン・プラズマによる除電処理を実行するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアを有する半導体装置において、微細化・高集積化・低コスト化を図りつつ、貫通ビアに起因する寄生容量の低減と、基板材料と貫通ビア材料との熱膨張係数の違いに起因する応力ミスマッチの緩和とをそれぞれ可能として信頼性を向上させる。

【解決手段】半導体基板5を貫通するようにビアホール21を形成する。ビアホール21内に絶縁性のビア被覆材料7aを埋め込む。ビアホール21の内壁を覆う部分のビア被覆材料7aをビア被覆膜7cとして残してビア被覆材料7aを除去する。ビア被覆膜7cが残存するビアホール21内に導電膜10を埋め込むことにより貫通ビア22を形成する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】表面性状が良好でかつ高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にウエハWを収容し、チャンバー1内にカルボン酸第1銅錯体、例えばCH3COOCuとこれを還元する還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110との間に、酸化しても導電性を有する導電材料(例えば金属)からなる導電層112を形成し、ここでは、導電プラグ110の下地膜を導電層112(Ag,Ni,Cu,Zn,In,Sn,Ir,Ru,Rh,Pd,Osから選ばれた少なくとも1種を材料として形成される。)とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】近年、半導体集積回路装置の製造プロセスにおいて、窒化シリコン膜等が有する応力に起因する歪を利用したキャリア移動度向上技術が活用されている。これに伴って、ウエハの表側における複雑なデバイス構造上の窒化シリコン膜を高選択で除去するため、熱燐酸によるバッチ方式ウエット処理が必須となっている。これによって、ウエハの裏面の窒化シリコン膜も除去され、一群の歪付与工程の後のプロセスにおいては、ウエハの裏側の表面はポリ・シリコン部材ということとなる。しかし、一般的なウエハの裏面等の洗浄に使用する方法は、裏面が窒化シリコン膜等であることを前提とするものであり、その特性の異なるポリ・シリコン主体の裏面を有するウエハでは洗浄の効果が十分といえない恐れがある。

【解決手段】リソグラフィ工程の前に、FPM処理の後SPM処理を実行する2工程を含むウエハ裏面に対するウエット洗浄処理を実行する。

(もっと読む)

半導体装置およびその製造方法

【課題】フリップチップ実装構造の半導体装置では、半導体基板(半導体チップ)裏面に抵抗を低減するための厚い金属層が設けられる。しかし、半導体チップの薄化が進むと、厚い金属層との応力の差により、半導体基板に反りが発生し、歩留まりが悪化する原因となっていた。

【解決手段】第1主面に動作領域が設けられ、第2主面に金属層が設けられる半導体基板(半導体チップ)の、少なくとも動作領域と一部重畳する第2主面側の半導体基板に凹部を設ける。これにより周辺部において第1の厚みを有し、凹部において第1の厚みより薄化された第2の厚みを有する半導体チップとする。周辺部が第1の厚みを有するため、第2主面側に厚い金属層を形成しても、半導体チップの反りを防止できる。

(もっと読む)

半導体装置の製造方法

【課題】 柱状電極上に半田バンプが形成された半導体装置において、柱状電極の平面サイズが異なっても、同一径の半田ボールを用いて、全ての半田バンプの高さを均一にする。

【解決手段】 柱状電極10a、10b、10c、10dは、縦方向の長さが同じで縦方向に直交する横方向の長さが異なる平面方形状であって、縦方向に同一ピッチで配置されている。そして、柱状電極10a、10b、10c、10dの上面に同一径の半田ボール25を柱状電極10a、10b、10c、10dの平面サイズに応じて3個、6個、8個、9個搭載する。次に、リフロー処理を行うと、それぞれ複数個の半田ボール25が溶融して互いに融合することにより、柱状電極10a、10b、10c、10dの上面に半田バンプが均一な高さとなるように形成される。

(もっと読む)

半導体装置の製造方法

【目的】従来よりも比抵抗の低いW膜のプラグ或いは配線が得られる半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜に開口部を形成する工程(S106)と、前記開口部の少なくとも底面に、ルテニウム(Ru)膜を形成する工程(S112)と、前記Ru膜が形成された前記開口部内に、水素(H2)還元による化学気相成長(CVD)法によりタングステン(W)膜を埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】チャネル形成領域にSiOxを含む酸化物半導体層を用い、電気抵抗値の低い金属材料からなるソース電極層及びドレイン電極層とのコンタクト抵抗を低減するため、ソース電極層及びドレイン電極層と上記SiOxを含む酸化物半導体層との間にソース領域またはドレイン領域を設ける。ソース領域またはドレイン領域は、SiOxを含まない酸化物半導体層または酸窒化物膜を用いる。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー内にウエハを搬入し、安定化させた後、ウエハを加熱しつつチャンバー内にCu錯体からなる成膜原料を気相状態で導入してウエハ上にCVD法によりCu膜を成膜し、成膜後、チャンバー内をパージして残留ガスを除去し、その後、チャンバーから基板を搬出するCu膜の成膜方法を実施するにあたり、パージの際に、ウエハへの入熱をCu膜成膜の際よりも低下させる。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供する。

【解決手段】ウエハW上の絶縁膜にビアホールとトレンチを形成し、この上にバリア層としてCVD−Ru膜を成膜する。チャンバー1内にウエハWを収容し、チャンバー1内に1価Cuβジケトン錯体であるCu(hfac)TMVSと、これを還元するアンモニア、還元性Si化合物、カルボン酸などの還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、ウエハWに形成されたCVD−Ru膜上にCVD−Cu膜を成膜するにあたり、チャンバー1内の圧力をCVD−Ru膜表面に吸着したCu(hfac)2の脱離および拡散が進行する圧力に制御する。

(もっと読む)

半導体装置

【課題】半導体デバイスに対する多様な要求に対し、柔軟に対応することができる半導体デバイスを提供する。

【解決手段】基板(2)と、ゲート絶縁膜(6)を介して基板(2)の上に設けられるゲート電極(3)と、ゲート電極(3)に隣接して配置されるサイドウォール(5)とを具備する半導体装置(1)を構成する。ゲート電極(3)は、引き出し電極部分(3−2)と実効ゲート電極部分(3−1)とを備えることが好ましい。また、引き出し電極部分(3−2)は、第1方向に沿って延伸する素子分離(9)の上に形成され、第1方向に沿った第1側面(16)(17)を有する部分とする。実効ゲート電極部分(3−1)は、素子分離(9)で分離される領域の上に形成され、第1側面(16)(17)を含む面に交差する面に沿った第2側面を有する部分とする。サイドウォール(5)は、第1側面(16)(17)を覆うことなく第2側面を覆うものとする。

(もっと読む)

201 - 220 / 751

[ Back to top ]