Fターム[5F033KK07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842)

Fターム[5F033KK07]の下位に属するFターム

Fターム[5F033KK07]に分類される特許

121 - 140 / 751

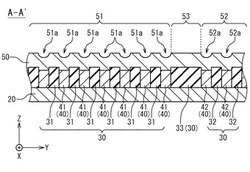

半導体装置および半導体装置の製造方法

【課題】電極パッドのプローブ領域とボンディング領域とを、光学顕微鏡による拡大観察で明確に識別することができる半導体装置を提供する。

【解決手段】半導体基板に形成された回路と接続される下層メタル配線20と、下層メタル配線20の上に形成され、複数のビアホール35、36を有する層間絶縁膜30と、複数のビアホール35、36を埋める複数の配線部40と、層間絶縁膜30及び複数の配線部40の上に形成され、複数の配線部40を介して下層メタル配線20と電気的に接続する上層メタル配線50とを具備する。層間絶縁膜30は、複数の第1ビアホール35を有する第1絶縁部31と、複数の第2ビアホール36を有する第2絶縁部32と、第1絶縁部31と第2絶縁部32との間に位置し、上面が平らな第3絶縁部33とを備える。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の信頼性の高い半導体装置を提供する。

【解決手段】半導体基板42上に台形状の凸部領域と台形状の凹部領域を設け、凹部領域のシリコン表面にはゲート酸化膜45が設けられ、ゲート酸化膜上にはゲート電極46が形成されている。凹部領域に設けられたゲート電極46の両側の凸部領域にはソース・ドレイン高濃度領域48が位置し、ソース・ドレイン高濃度領域48とゲート電極46の間にはソース・ドレイン低濃度領域47が形成されている。ソース・ドレイン高濃度領域48の上表面には第1層目の金属配線49と第2層目の金属配線50と第3層目の金属配線52が積層され、ソース・ドレイン高濃度領域48から第3金属配線までの接続にコンタクトホールやビアホールなどを利用していない。このように本発明の半導体装置は、コンタクトホールやビアホールなどの接続孔を形成しないで素子と配線との接続や配線間接続を行なうことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。更に、その回路基板とその他のチップとを積層して、それらをボンディングワイヤで絶縁基板に支持されないリードへ接続する。

(もっと読む)

積層集積回路のための二面の相互接続されたCMOS

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

評価用半導体チップ、評価システム及びそのリペア方法

【課題】半導体チップを評価する技術を提供する。

【解決手段】

シリコン基板の一方の面に、複数領域からなる抵抗測温体としての金属配線膜101、及び、1つ又は複数領域からなるヒータとしての金属配線膜102の少なくとも何れかと、金属配線膜101及び金属配線膜102を実装基板と接続するための電極103と、が積層された半導体チップを実装基板に実装して、金属配線膜101を電流計及び電圧計と、金属配線膜102を電源と、電気的に接続することで、半導体チップの上記各領域における測温及び加熱、及び、その温度プロファイルが評価可能な評価システムを提供する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置の製造方法

【課題】貫通孔となるべきアスペクト比が20以上の深孔を埋め込む貫通電極金属としては、埋め込み特性が良好なタングステンが使用されることが多いが、通常のドライエッチングによる深孔は、ボッシュプロセスによるものに比べて寸法の大きなものとなる。この比較的大きな深孔を埋め込むためには、必然的にウエハの表面に成膜すべきタングステン膜の膜厚も厚くなり、その結果、ウエハの反りが、プロセスを正常に実行できる限界を超える程度にまで増加する。また、このような問題が許容できる限度内である場合にも、タングステン膜を堆積する際に、ウエハの周辺で下地膜の剥がれが発生する等の問題がある。

【解決手段】本願発明は、貫通ビアを形成するための非貫通孔をタングステン部材で埋め込むに当たり、ウエハの周辺部において、下地のバリアメタル膜の外延部より内側に、タングステン部材の外延部を位置させるように成膜を実行するものである。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】基板を薄板化しても基板の反りを抑制でき、耐熱性、機械特性に優れた絶縁膜で保護された半導体素子及びその製造方法を提供する。

【解決手段】基板1の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板の表面に、芳香族テトラカルボン酸及び芳香族テトラカルボン酸二無水物から選ばれる1種以上のアシル化合物を、前記芳香族ジアミンよりも1モル%以上多く反応して得られるポリアミド酸を含むポリイミド前駆体組成物を塗布し、イミド化して絶縁膜3を形成し、第1表面電極2及び絶縁膜3が少なくとも形成された基板1を、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

低誘電率誘電体を含む超小型電子構造およびその構造内の炭素分配を制御する方法

本発明の実施形態は、超小型電子構造の形成に関する。32nmの次のテクノロジーノード向けの低誘電率誘電体材料は、約2.6未満の誘電率を呈する必要がある。本発明により、全体として超小型電子構造の曲げおよび剪断強度の完全性を向上させながら、そのような低誘電率誘電体材料を使用する半導体デバイスを形成することが可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

伝送線のためのシールド構造体

シールド構造体は、集積回路上の第1金属化層に形成された櫛状構造体が複数の歯を備え櫛状構造体の歯は他方の櫛状構造体に向かって延びる第1、第2櫛状構造体と、第1櫛状構造体から上方に延びる複数の第1導電性ビアと、第2櫛状構造体から上方に延びる複数の第2導電性ビアと、第1金属化層の上方の第2金属化層に配置された第1、第2平面構造体と、第1平面構造体から複数の第1導電性ビアに向かって下方に延びる複数の第3導電性ビアと、第2平面構造体から複数の第2導電性ビアに向かって下方に延びる複数の第4導電性ビアとを備え、第1、第2櫛状構造体、第1、第2平面構造体及び第1〜第4導電性ビアは全て同電位であり接地されることが好ましい。ある実施形態では1つ以上の信号線が第1、第2平面構造体間の第2金属化層に配置され、他の実施形態では1つ以上の信号線が第1、第2平面構造体間の第3金属化層に配置される。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】ロジック回路のコンタクト抵抗の増加を抑制しつつ、メモリ回路のキャパシタ容量を最大限に高めることが実現される半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置においては、ロジック回路を構成する配線を有する配線層の層数をMとし、メモリ回路を構成する配線を有する配線層の層数をNとしたとき(MおよびNは自然数であって、M>N)、(M−N)層あるいは(M−N+1)層の配線層にわたって、容量素子150が設けられている。

(もっと読む)

配線基板の製造方法

【課題】スループットが向上し、且つ少ない液滴量でも第1の電極と第2の電極とを導通性を確保する。

【解決手段】基体10の表面10aに形成された微細穴2の底部2aとなる下面電極3と、基体10の表面10aであって微細穴2の内壁部2bの上端近傍に配置された上面電極5とを導通させる導電層12を形成する。この導電層12の形成において、まず、金属ナノ粒子11を分散させるためのクリアインク8を微細穴2に充填する。次に、微細穴2に金属ナノ粒子11を含有する液滴を供給し、金属ナノ粒子11を微細穴2内のクリアインク8で分散させる。次に、微細穴2内のクリアインク8を揮発させることで、微細穴2の底部2a及び内壁部2bに析出した金属ナノ粒子膜11Aを有する導電層12を形成する。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備した半導体装置において、低コストで、半導体ウエハからEM保護の施されたダイを形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように形成される。この傾斜サイドウォール上、および、半導体ダイの底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIから保護する。

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

EM保護が施された半導体ダイを形成する方法

【課題】電磁(EM)妨害あるいはEMIに対してある程度の保護を具備し半導体装置において、半導体ウエハからダイを低コストで形成する方法を提供する。

【解決手段】半導体ダイ12,13,14は、傾斜したサイドウォール35,36,37を有するように輸送テープあるいはキャリヤ・テープ38上に形成される。この傾斜サイドウォール上、および、底部表面上に導体40が形成される。導電材料である導体40は、ダイ12−14に対しEMIからの保護を提供する。

(もっと読む)

半導体装置及びその製造方法

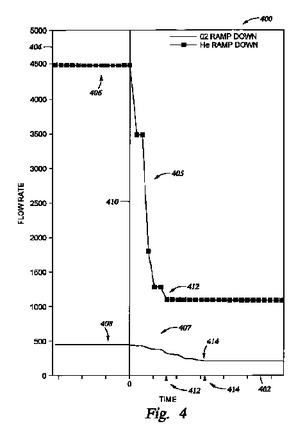

【課題】配線が形成される多孔質絶縁膜がプラズマダメージ等を受けるのを防ぐことにより、高歩留り且つ高信頼性な半導体装置を得られるようにする。

【解決手段】半導体基板の上に、化学気相成長法により、炭素濃度、空孔形成剤濃度及び酸素濃度がそれぞれ異なる複数の領域を有する空孔形成剤含有膜を形成する工程を備えている。この工程は、前駆体、空孔形成剤及び酸化剤を第1の流量で流す第1の期間と、第1の期間の後に、前駆体の流量に対する空孔形成剤の流量を減少させる第2の期間と、第2の期間の後に、前駆体の流量に対する空孔形成剤の流量の減少を停止し、前駆体、空孔形成剤及び酸化剤を第2の流量で流す第3の期間と、第3の期間の後に、前駆体の流量に対する酸化剤の流量を増大させる第4の期間と、第4の期間の後に、前駆体、空孔形成剤及び酸化剤を第3の流量で流す第5の期間とを含む。

(もっと読む)

121 - 140 / 751

[ Back to top ]