Fターム[5F033KK07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842)

Fターム[5F033KK07]の下位に属するFターム

Fターム[5F033KK07]に分類される特許

61 - 80 / 751

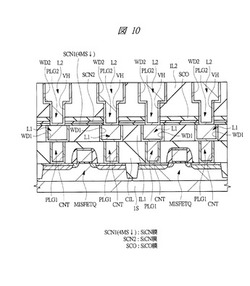

半導体装置およびその製造方法

【課題】半導体装置を構成する配線の信頼性向上を図る。

【解決手段】テトラメチルシランガスの流量を通常条件よりも下げて形成したSiCN膜SCN1(4MS↓)と、このSiCN膜SCN1(4MS↓)上に形成され、通常のテトラメチルシランガスの流量で形成したSiCN膜SCN2と、このSiCN膜SCN2上に形成されたSiCO膜SCOからバリア絶縁膜を構成する。これにより、耐透水性の向上と低誘電率化をバランス良く実現することができる。

(もっと読む)

抵抗回路を有する半導体装置

【課題】高抵抗・高精度の抵抗素子からなる抵抗回路を提供する。

【解決手段】500Å以下に薄膜化した薄膜材料からなる抵抗素子の上にシリコン窒化膜などの絶縁膜を形成する。この窒化膜により抵抗素子に対するコンタクトホールの突き抜けを防止する。

(もっと読む)

積層した接続レベルを有する集積回路装置用マスク数の低減法

【課題】3D積層メモリ装置は、各接続レベル毎に別個のマスクが使用されるので必要なマスク数は多くなるが、パターンを工夫して必要マスク数を減らす。

【解決手段】3次元積層集積回路装置は配線領域に接続レベルの積層部を有する。接続レベルの積層部で2のN乗個のレベルまで含む配線接続領域を形成するためのN個のエッチングマスクの組だけが必要とされる。幾つかの例によれば、2のX−1乗(2X−1)個の接続レベルは、連続番号Xのエッチングマスクでエッチングされ、1つのマスクがX=1であり、他の1つのマスクがX=2であり、X=Nまで付与される。当該方法は接続レベルでの形成領域に整合した配線接続領域を形成する。

(もっと読む)

バッチ製作された3D相互接続

【課題】ウェハ貫通ビア(TWV)を使用した相互接続において、ダイ区域の消費を低減し、ダイ区域を利用可能とする、バッチ製作された3D相互接続を提供する。

【解決手段】1つまたは複数の垂直相互接続を製作する。ウェハ積層体を形成するために複数のウェハをパターニングおよび積層するステップを含む。ウェハ積層体の1つまたは複数の切断刃の通り道内でウェハ積層体に複数の開口を形成し、導電性材料を複数の開口の側壁に堆積させる。ウェハ積層体は、側壁の導電性材料が、結果として得られる積層ダイの縁部部分に露出されるように、1つまたは複数の切断刃の通り道に沿い、複数の開口を通ってダイシングする。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

半導体装置

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を備える半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体素子が設けられた半導体基板と、前記半導体基板上に形成された、上下層の導電部材を電気的に接続する接続部材と、前記接続部材と同じ層に形成された第1の絶縁膜と、前記接続部材の上面の一部と接する第1の領域、および前記第1の領域上に位置し、前記第1の領域よりも幅の広い第2の領域を含む配線と、前記第1の絶縁膜上に、前記配線の前記第1の領域の側面の上側から少なくとも一部、および前記第2の領域の底面に接して形成された第2の絶縁膜と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】凹形状を有するホールの内壁側面上に側壁保護膜の一部を残留させることにより、ホールの内壁側面を平滑化する。後の工程でホール内に材料を埋設する際にも、ボイドを発生させることなく優れた埋設性でホール内を材料で埋設させる。

【解決手段】半導体基板の裏面上にマスクを設ける工程と、マスクを用いて半導体基板を貫通すると共に凹形状の内壁側面を有するホールであって内壁側面が側壁保護膜で覆われたホールを形成する工程と、側壁保護膜の一部を残留させるようにマスクを除去する工程と、を有する半導体装置の製造方法。

(もっと読む)

熱型検出器、熱型検出装置及び電子機器

【課題】 熱型検出素子を基体から熱分離する空洞部の深さを規定するスペーサー部材を配線構造として兼用し、かつ、その配線構造により、確実に熱分離できる空洞部の深さを確保することができる熱型検出器、熱型検出装置及び電子機器を提供すること。

【解決手段】 熱型検出器は、基体100と、基体100より突出するスペーサー部材104と、スペーサー部材104に支持される支持部材210と、支持部材に支持される熱型検出素子220と、基体内に配置されて熱型検出素子と接続される検出回路510,520と、熱型検出素子と検出回路とを接続する配線部と、を有する。配線部は、基体内に配置された少なくとも一層の第1導電層LIA,LIBと、スペーサー部材内に配置された少なくとも一層の第2導電層LIC,LIDと、支持部材に支持された第3導電層214,238と、第1,第2及び第3導電層の隣接層同士を接続する複数のプラグHLA〜HLDとを含む。

(もっと読む)

半導体集積回路装置用ルテニウムバリア膜とその作製方法及び該ルテニウムバリア膜を有する半導体集積回路装置とその製造方法

【課題】クレバスの面積比が小さく、低抵抗を維持した薄膜の状態で、配線層を構成する銅又はアルミニウム等の拡散を防止できるルテニウムバリア膜とその作製方法及び該ルテニウム膜を有する半導体集積回路装置とその製造方法を提供する。

【解決する手段】ルテニウムバリア膜は、ルテニウムを主成分とする金属からなり、表面上に観測されるクレバス(溝、割れ目又は深く鋭いくぼみ)の占める面積比が、前記バリア膜表面の全面積に対して15%以下であり、広角X線回折測定によって得られるX線回折プロファイルにおいて、ルテニウムの結晶配向面(002)及び(100)に起因するスペクトルのそれぞれのピーク強度比であるRu(002)/Ru(100)が10以上であり、また、スパッタリング法によって、温度を500℃以上に加熱した状態の半導体基板の配線溝上に成膜されることを特徴とする。

(もっと読む)

半導体集積回路装置用バリア材の探索方法及び当該探索方法によって探索される半導体集積回路装置用バリア材

【課題】従来のルテニウムバリア材と同様に優れた銅拡散の抑制効果を有し、供給性の点で問題がなく、比較的低コストの金属又はその金属を含む金属間化合物からなる新規な半導体集積回路装置用バリア材の探索方法及び当該探索方法によって探索される半導体集積回路用バリア材を提供する。

【解決する手段】バリア膜若しくはバリア膜とシード膜からなる複合膜の上に銅配線層を有する半導体集積回路装置の前記バリア膜を構成するバリア材として、単位結晶格子の最近接原子間距離(DM)がルテニウムの単位結晶格子の最近接原子間距離(DRu)に近い領域、具体的には、オングストローム(Å)単位で−0.200Å<(DM―DRu)<0.12Åの関係にあって、かつ融点若しくは変態点が650ケルビン(K)以上である金属又は金属間化合物を選択することを特徴とする。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体装置及びその製造方法

【課題】銅又は銅合金からなる配線との密着性が高いバリアメタル層を備え、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置では、半導体基板100の上方に配置された絶縁膜106と、絶縁膜106中の溝に配置され、銅又は銅合金からなる配線115とを備え、絶縁膜106と配線115との間に、白金族元素、又は白金族元素の合金からなるバリアメタル層を有しており、バリアメタル層は、非晶質構造を有する第1のバリアメタル層109と第1のバリアメタル層109の上に配置された多結晶構造を有する第2のバリアメタル層110からなる積層構造であり、第2のバリアメタル層110には銅が含まれており、第2のバリアメタル層110中の金属に占める銅の割合は50at%以下である。

(もっと読む)

表面被覆方法、並びに半導体装置、及び実装回路基板

【課題】配線及び絶縁膜へダメージを与えることなく、絶縁膜上の導電性の不純物によるめっきの異常成長を抑制することができる表面被覆方法、並びに該方法を用いて製造される半導体装置、及び実装回路基板の提供。

【解決手段】水溶性樹脂、有機溶剤、及び水を含有する表面被覆材料を、表面に露出した絶縁膜及び表面に露出したパターニングされた金属配線を有する積層体の少なくとも前記絶縁膜の表面を覆うように塗布し、前記絶縁膜の表面に被膜を形成する表面被覆方法である。

(もっと読む)

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】有機電界効果トランジスタにおけるビア形成を、低コストで効率的なプロセスで実現する。

【解決手段】誘電層106内にビア113を形成する際、まず各ビア位置にパターン化された導電材よりなるポストを印刷し、次にパターン化されていない誘電層106を堆積させ、次に第2のパターン化された導電層を堆積させる。ビア113は、誘電層106を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールすることにより形成される。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

(もっと読む)

半導体装置の製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】半導体素子の第1領域と接続される表面電極17、および通路12の少なくとも一部に、半導体素子の第2領域と接続される第1金属配線18を形成する。その後、はんだ29が実装されない通路12bに形成する第1保護膜25の高さが、はんだ29が実装される通路12aに形成する第1保護膜25の高さよりも高くなるように、注入器32を用いて第1保護膜25を通路12に塗布する。続いて、表面電極17および第1保護膜25の上に金属層27、28を形成してはんだ29が実装されない通路12bに形成した第1保護膜25が金属層27、28から露出するように、はんだ29が実装されない通路12bに形成した第1保護膜25の一部および金属層27、28を切削する。

(もっと読む)

バリア層の形成方法

【課題】 本発明は、以上の点に鑑み、異種金属からなる導電層間に介在されるような場合でも十分なバリア性能を発揮し得るバリア層を生産性よく形成することができるバリア層の形成方法を提供する。

【解決手段】 バリア層BMは、処理対象物Wを一方の導電層CL1を有するものとし、この処理対象物と、例えばTi製のターゲット2とを真空処理室1a内に配置し、真空処理室内に希ガスを導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして一方の導電層表面に第1金属層を形成し、真空処理室内に酸素ガス及び窒素ガスを含むガスを導入してプラズマ雰囲気を形成し、第1金属層の表面を酸窒化処理すると共に、ターゲットをもプラズマ雰囲気に曝して当該ターゲット表面を酸窒化し、真空処理室内に希ガスを更に導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして酸窒化処理された表面に第2金属層を形成してなる。

(もっと読む)

61 - 80 / 751

[ Back to top ]