Fターム[5F033KK07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842)

Fターム[5F033KK07]の下位に属するFターム

Fターム[5F033KK07]に分類される特許

21 - 40 / 751

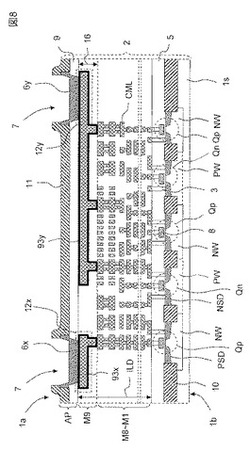

半導体集積回路装置

【課題】銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。

【解決手段】本願発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

(もっと読む)

半導体装置の製造方法

【課題】SiCOH膜からなる層間絶縁膜に形成された埋め込み用の凹部に銅材を埋め込んで導電路を形成するにあたり、導電路の抵抗を低くすること。

【解決手段】SiCOH膜にプラズマにより凹部を形成すると表面が疎水性になる。このSiCOH膜に水素ガスのリモートプラズマを供給し、Hラジカル及びHイオンにより凹部の表面を親水性に改質する。またプラズマに代えて過酸化水素水を供給してもよく、この場合表面にOH基が形成される。次いで例えばRu3(CO)12ガスとCOガスとを用いてCVDによりRu膜4を成膜し、その後銅材5を埋め込み、CMP処理をして上層側の配線構造を形成する。また改質にあたって、グリム、DMEDAなどを用いてもよい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

集積回路構造及び裏面照射型イメージセンサデバイス

【課題】裏面照射(BSI)型イメージセンサチップのパッド構造を提供する。

【解決手段】前面及び背面を含む半導体基板、前記半導体基板の前記前面に配置される低k誘電体層、前記低k誘電体層に配置される非低k誘電体層、前記非低k誘電体層に配置される金属パッド、前記半導体基板の背面から延伸し、前記半導体基板、前記低k誘電体層、及び低k誘電体層を貫通し、前記金属パッドの表面を露出する開口、及び前記開口の側壁及び底部上に形成され、前記開口の底部は、前記金属パッドの前記露出された表面を部分的に覆う保護層を含む集積回路構造。

(もっと読む)

貫通配線付き接合基板

【課題】貫通孔内に配した樹脂が熱膨張することによって電極を破損することを防止した貫通配線付き接合基板の提供。

【解決手段】

一面1aに電極層2が形成された第一基板1、及び電極層2と接合樹脂層3を介して、第一基板1と接合された第二基板4とを備えた貫通配線付き接合基板10Aであって、第一基板1の他面1b側から電極層2が露出するまで第一基板1を貫通する貫通孔5と、貫通孔5の内部において、貫通孔5の内側面5c及び電極層2を覆う貫通配線層6と、貫通配線層6を覆い貫通孔5の内部に充填された充填樹脂部7とを有し、充填樹脂部7を構成する樹脂のヤング率は、接合樹脂層3を構成する樹脂のヤング率よりも小さいことを特徴とする貫通配線付き接合基板10A。

(もっと読む)

相互接続構造体及びその形成方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

半導体装置の製造方法

【課題】生産性および信頼性を向上することができる半導体装置の製造方法を提供すること。

【解決手段】第一の接合工程では、半導体チップ10、第一樹脂層11、半導体チップ12、第二樹脂層13、半導体チップ14を積層することにより得られ、半導体チップ10,12同士、半導体チップ12,14同士が半田接合されていない状態の積層体2を加熱して、半導体チップ10,12間、半導体チップ12,14間の半田接合を行う。その後、半田接合した積層体2を基材18上に設置する。積層体2の基材18への接続用端子162と、基材18の積層体2への接続用端子181とが当接するように、積層体2を基材18上に設置する。

(もっと読む)

回路基板、回路基板の製造方法、表示装置および電子機器

【課題】被蒸着膜を高精細なパターンで形成することが可能な蒸着用マスクを提供する。

【解決手段】蒸着用マスクは、1または複数の第1開口部を有する基板と、この基板の一主面側に設けられると共に、各第1開口部と対向して1または複数の第2開口部を有する高分子膜とを備える。蒸着の際には、蒸着材料が第1開口部および第2開口部を順に通過することにより、第2開口部に対応した所定のパターンで被蒸着膜が形成される。基板と高分子膜とを組み合わせて用いることにより、機械的強度を保持しつつも、金属膜のみで構成されている場合に比べ、第2開口部において微細かつ高精度な開口形状を実現できる。

(もっと読む)

半導体装置、電子機器、及び、半導体装置の製造方法

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置1を、接合界面Sj側の表面に形成された第1金属膜16を有する第1半導体部10と、接合界面Sjで第1金属膜16と接合された第2金属膜26を有する第2半導体部20と、界面バリア部28とを備える構成とする。第2金属膜26の接合界面Sj側の表面面積は第1金属膜16の接合界面Sj側の表面面積より小さくする。そして、第1金属膜16の接合界面Sj側の面領域のうち第2金属膜26と接合しない面領域を含む領域に界面バリア部28を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】高アスペクト比の溝内にカバレッジ性良く絶縁膜を埋め込むと表面にスリット状の空孔が形成され、CMPで平坦化すると、CMPで用いた組成物や、研磨された除去物、その他の残渣が空孔内に残り易く、この残渣は後の工程での発塵の一原因となり得る。

【解決手段】基板1の第1の主面に、俯瞰形状が環状となる第1の溝部2Tを形成し、第1の主面全面に第1の絶縁膜2aを形成し、第1の絶縁膜2aの表面から前記第1の溝部の内部まで達する深さの空孔を残しつつ、前記第1の絶縁膜を第1の溝部に埋め込み、空孔内を埋め込むように第1の絶縁膜上に第2の絶縁膜を形成し、第1の溝部内に第1の絶縁膜および第2の絶縁膜を残しつつ、基板表面高さまで化学機械研磨法により平坦化する。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりを向上することができる半導体装置の製造方法を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、絶縁膜形成工程と、周縁部露出工程と、導体膜形成工程とを含む。前記絶縁膜形成工程では、半導体ウェハ上に絶縁膜を形成する。前記周縁部露出工程では、前記絶縁膜の形成後に、前記半導体ウェハの周縁部を露出させる。前記導体膜形成工程では、前記半導体ウェハにおける露出させた周縁部および前記絶縁膜上に導体膜を形成する。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

電子デバイス及びその製造方法

【課題】貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイスを提供する。

【解決手段】基板1と、基板1の表面上方に形成された配線18と、基板1の裏面から基板1を貫通しており、基板1の深さ方向において、第1の開孔1Aaと、第1の開孔1Aaよりも開口総面積が小さい第2の開孔1Abとが接続された貫通孔1Aに形成されてなる貫通ビア30とを含み、貫通ビア30は、第1の開孔1Aaに形成された第1の電極部30aと、第2の開孔1Abに形成された第2の電極部30bとが、最外側面が一体形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板の反射率に依存せず、アライメントマークの識別性を確保することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、シリコン基板24と、シリコン基板24上に少なくともNiCoパターン31とアルミ電極30とを含んで形成される回路部3と、シリコン基板24上に回路部3のNiCoパターン31と同工程において形成される低反射パターンとしてのNiCoパターン22と、NiCoパターン22上に形成され、回路部3のアルミ電極30と同工程において形成される高反射パターンとしてのアルミパターン20とを有する。

(もっと読む)

21 - 40 / 751

[ Back to top ]