Fターム[5F033KK07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842)

Fターム[5F033KK07]の下位に属するFターム

Fターム[5F033KK07]に分類される特許

81 - 100 / 751

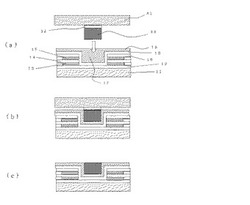

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体構造同士を直接結合する方法、およびこの方法を使用して形成された結合された半導体構造

【課題】半導体構造同士を直接結合する方法を提供すること。

【解決手段】本発明の実施形態は、半導体構造同士を直接結合する方法を含む。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ間の境界面に、キャップ層を提供することができる。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ内に、不純物が提供される。そのような方法を使用して、結合された半導体構造が形成される。

(もっと読む)

半導体装置の製造方法

【課題】低コストで、かつ簡便な方法で、コンタクトプラグ上に形成される銅配線の上面にヒロックが生じて短絡が発生することを抑制可能な半導体装置の製造方法を提供する。

【解決手段】配線13を覆う層間絶縁膜15の上面に、層間絶縁膜よりもエッチング速度の遅いエッチングストッパ膜16を形成する。エッチングストッパ膜のうち、配線と対向する部分を貫通する第1の開口部16Aを形成する。エッチングストッパ膜よりも層間絶縁膜がエッチングされやすい条件を用いて、配線の上面が露出するまで第1の開口部の下方に位置する層間絶縁膜をエッチングして、第1の開口部と共にコンタクトホールを構成する第2の開口部15Aを形成する。第1の開口部を埋め込むように、コンタクトホール内に導電膜を成膜することでコンタクトプラグ27を形成する。電解メッキ法により、コンタクトプラグの上面と接触する銅配線39を形成する。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

半導体装置

【課題】超高周波帯におけるシリコン基板による損失を低減すると共に、貫通配線のインダクタンス成分の影響を小さくした半導体装置を実現できるようにする。

【解決手段】半導体装置は、回路素子105が形成された半導体基板100と、半導体基板100の主面の上に形成された第1の誘電体層121と、第1の誘電体層121の上に形成された第2の誘電体層131と、第1の誘電体層121を貫通し、回路素子105と接続された第1の貫通配線122と、第2の誘電体層131を貫通し、第1の貫通配線122と接続された第2の貫通配線132とを備えている。第2の貫通配線132は、第1の貫通配線132よりもインダクタンスが小さい。

(もっと読む)

半導体装置、およびその製造方法、ならびにデータ処理装置

【課題】テーパー部を有する溝を備えた半導体装置を容易に形成する。溝内に空洞が形成されるのを防止すると共に、製造歩留まりの低下を抑制する。

【解決手段】半導体装置は、第1の面を有する材料層と、材料層内に設けられ、第1の面に開口部を有する溝を備える。溝は、開口部に接し1以上のスキャロップ形成溝を有するテーパー部と、おおむね垂直な側壁を有する垂直部を有する。スキャロップ形成溝の幅は、垂直部の溝幅よりも大きくなっている。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

半導体装置、及び、その製造方法

【課題】微細配線を有する半導体装置の信頼性を向上させる。

【解決手段】本発明に係る半導体装置は、第1のCu配線102と、第1のCu配線102の上に設けられ、第1のCu配線102からCuの拡散を防ぐ第1のバリア絶縁膜103とを備える。また、第1のバリア絶縁膜103の上には、第2のCu配線105と、第1のCu配線105の上に設けられ、第2のCu配線105からCuの拡散を防ぐ第2のバリア絶縁膜106と、を備える。第1、第2のバリア絶縁膜103、106は、分枝アルキル基、及び、炭素−炭素二重結合を有するシリコン系絶縁膜からなる。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な半導体装置を提供する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

(もっと読む)

ウエハレベルパッケージ構造およびその製造方法

【課題】切削刃の磨耗を抑制して切削刃の寿命を延ばすことが可能なウエハレベルパッケージ製造方法を提供する。

【解決手段】ウエハレベルパッケージ製造方法は、例えば、基板450の表面に、配線が形成される溝462を含む絶縁性の第1の樹脂460を形成する樹脂形成工程400と、第1の樹脂460の表面に、配線の一部となる第1の金属470を、物理気相成長によって成膜する第1の成膜工程410と、第1の金属470の表面に、配線の一部となる、第1の金属470より硬度が低い第2の金属480を、更に成膜する第2の成膜工程420と、溝462の側面において第1の金属470が成膜されていない場所または薄くなっている場所に該当する高さH0、H1に切削刃490を設置する設置工程430と、切削刃490を走査することにより、少なくとも第1の樹脂460を切削する切削工程440とを含む。

(もっと読む)

半導体装置

【課題】マイクロバンプの半導体素子側への接着力を向上できる半導体装置を提供する。

【解決手段】半導体素子2と半導体素子の電極パッドと、電極パッド20を露出する開口41を有するバッファーコート膜40と、開口を介して電極パッドに電気的に接続されたマイクロバンプ50とを備え、マイクロバンプと開口の側面41bとの接触面積は、マイクロバンプと開口の底面60aとの接触面積より大きいことを特徴とする半導体装置。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】カーボンナノチューブ配線の製造方法は、第1導電層200上に、絶縁膜18を形成し、前記絶縁膜内に、前記絶縁膜を貫通するホール40を形成し、前記ホール内の底面の前記第1導電層上および前記ホール内の側面の前記絶縁膜上に、触媒下地膜19を形成し、前記ホール内の側面の前記触媒下地膜上に、触媒不活性膜20を形成し、前記ホール内の底面の前記触媒下地膜上および前記ホール内の側面の前記触媒不活性膜上に、触媒膜21を形成し、前記ホール内の底面の前記触媒膜上から複数のカーボンナノチューブ22を成長させる。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置及び製造方法

【課題】 基板及び表面層にビアホールが形成された半導体装置において、表面層の剥離及び破壊を抑制すること。

【解決手段】 本半導体装置は、基板10と、基板10上に設けられた基板10と異なる材料からなる表面層20と、表面層20上に設けられた電極パッド50と、を備え、基板10及び表面層20にはビアホール30が形成され、ビアホール30内には、電極パッド50と電気的に接続された金属層32が設けられ、ビアホール30の開口部の周囲には、ビアホール30を囲むように表面層20に溝22が形成されている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を提供する。またこのような半導体装置の作製方法を提供する。

【解決手段】半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこのように作製したコンタクトを用いて半導体装置を作製すればよい。

(もっと読む)

81 - 100 / 751

[ Back to top ]