Fターム[5F033LL02]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142) | 金属 (317)

Fターム[5F033LL02]に分類される特許

61 - 80 / 317

耐ITOピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供すること。

【解決手段】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記Al合金膜は、Geを0.1〜5原子%含むと共に、前記Al合金膜の3倍以上のGeを含む第1層と、第1層よりもGe含有率の低いAl合金からなる第2層と、を含む積層構造を有すること。

(もっと読む)

薄膜の形成方法

【課題】埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させることが可能な薄膜の形成方法を提供する。

【解決手段】表面に凹部8を有する被処理体Wの表面に薄膜を形成する形成方法において、被処理体の表面に埋め込み用の金属膜16して凹部を埋め込む埋め込み工程と、金属膜を覆うようにして被処理体の表面の全面に拡散防止用の金属膜18を形成する拡散防止膜形成工程と、被処理体をアニールするアニール工程とを有する。これにより、埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させる。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

パターンの形成方法と当該パターンを備えた液晶表示装置の製造方法

【課題】透明膜を露光する際に、下地となる電極配線や露光ステージの溝等の存在により露光の光が局所的に強度が変動する反射光となってレジストを露光するため、高精細なパターニングができない。

【解決手段】透明膜上に遮光膜を形成する工程と、前記遮光膜上にレジスト層を塗布し、露光を行なってレジストパターンを形成する工程と、前記レジストパターンをマスクとして、前記遮光膜を除去する工程と、前記レジストパターンをマスクとして遮光膜を除去した後、透明膜を除去する工程と、前記レジストパターンを除去する工程と、前記レジストパターン除去後に、透明膜上の遮光膜を除去する工程を含むことを特徴とする。

(もっと読む)

表示装置及びその製造方法

【課題】ソース・ドレイン電極に、剥離やストレスマイグレーションによるボイドが発生するのを抑制する。

【解決手段】複数の薄膜トランジスタが配列された基板を有する表示装置であって、薄膜トランジスタは、半導体層6と、半導体層6上に形成されるコンタクト層7と、コンタクト層7上に形成されるソース電極10及びドレイン電極9とを有し、ソース電極10およびドレイン電極9は、コンタクト層7の上側に形成される第1の導電層9a,10aと、第1の導電層9a,10aの上側に形成される第2の導電層9b,10bとを有し、第2導電層9b,10bは、第1添加元素と、銅とを含有する銅合金層であり、前記第1添加元素は、ジルコニウム、チタン、銀、インジウム、金、錫、クロム、ケイ素から選ばれた少なくとも1種類の元素である、ことを特徴とする表示装置。

(もっと読む)

表示装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置用Al合金膜である。

(1)Alと、X群から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含む第1の析出物について、円相当直径20nm以上の析出物が500,000個/mm2以上の密度で存在する。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

半導体装置の製造方法

【課題】銅配線を有する半導体装置において、銅配線の配線抵抗やコンタクトと抵抗を増加することなく信頼性を向上しうる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に形成された開口部内に、銅に対して拡散防止作用を有する第1金属材料を含む第1の膜と、酸素を含有する銅膜を含む第2の膜と、銅と、酸素と結合することにより銅に対して拡散防止作用を有する第2金属材料とを含む第3の膜と、銅を主材料とする第4の膜とを含む配線層を形成した後、熱処理により、絶縁膜と第4の膜との間に、第1金属材料、第2金属材料及び酸素を含むバリア層を形成する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置の薄膜トランジスタ基板において、水素プラズマ処理時の水素による影響を低減する。

【解決手段】非晶質ケイ素の膜により形成された非晶質ケイ素層上に形成される銅配線において、第1添加元素として水素化物の生成エネルギーが負の元素、さらに第2添加元素を含む銅を主成分とする合金により形成された銅合金層107Aと、前記銅合金層の上に純銅により形成された純銅層107Bとを有する薄膜トランジスタ基板を備える。

(もっと読む)

回路基板及び電子デバイス

【課題】導体の亀裂、基板のクラック、絶縁膜の破壊等を生じ難い高信頼度・高品質の回路基板及び電子デバイスを提供する。

【解決手段】基板1と、導体3とを含んでおり、導体3は、金属または合金でなり、基板1に設けられ、少なくとも基板1と対面する領域に、等軸晶31の領域を有する。この構造によれば、基板1と対面する領域で、導体3の等軸晶組織による等方性が得られるため、導体3の亀裂、絶縁膜の破壊及び基板1のクラックなどの発生が抑制される。

(もっと読む)

表示装置

【課題】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を備えた表示装置であって、上記腐食防止用塗料の塗布や剥離といった更なる工程を設けることなく、ピンホール腐食を防止することのできる表示装置を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を備えた表示装置であって、前記Al合金膜が、Niおよび/またはCoを0.15原子%以下(0原子%を含まない)、Geを0.2原子%以上2.0原子%以下、およびLa、Gd、NdおよびYよりなる群から選択される1種以上の元素を0.05原子%以上1.0原子%以下含有し、かつ、前記Al合金膜の表面において観察される腐食孔のアスペクト比(腐食深さ/腐食直径)が0.12以下であることを特徴とする表示装置。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

半導体装置及び半導体装置の製造方法

【課題】凹部内のボイドの発生を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板10の表面に形成されている絶縁膜100に、凹部111を形成する工程と、凹部111内にシード膜104を形成する工程と、凹部111内に、カバーメタル膜106を形成する工程と、カバーメタル膜106を選択的に除去して、凹部111の底部にシード膜104を露出させる工程と、凹部111の底部に露出されたシード膜104をシードとして、凹部111内を埋め込むめっき膜140を成長させる工程と、を含む。

(もっと読む)

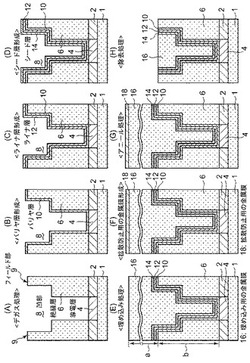

薄膜トランジスタおよびその製造方法

【課題】オフ電流および漏れ電流が抑制された薄膜トランジスタ、および前記薄膜トランジスタを歩留り良く製造することのできる薄膜トランジスタの製造方法を提供する。

【解決手段】ゲート電極12上にゲート絶縁膜12を介して順次形成されるSi(i)膜13およびSi(n)膜14上に金属膜を形成し、フォトレジストパターン22をマスクとしてエッチングし、ソース電極15およびドレイン電極16を形成する。酸素を含むプラズマで処理して、フォトレジストパターン22の側面を後退させるとともに、ソース電極15およびドレイン電極16の側面および露出した上面にAl酸化皮膜17を形成する。残存するフォトレジストパターン22およびAl酸化皮膜17をマスクとして、チャネル部18のSi(n)膜14およびSi(i)膜13の表面の一部をエッチングする。

(もっと読む)

無電解銅めっき液、無電解銅めっき方法、及び埋め込み配線の形成方法

【課題】孔の内径の大小にかかわらず、該孔の奥まで均一な無電解銅めっき層を形成しうる無電解銅めっき液および無電解銅めっき方法を提供する。また、該無電解銅めっき層を形成することにより孔の内部に信頼性の高い埋め込み配線を形成することのできる埋め込み配線の形成方法を提供する。

【解決手段】チオール基又はジスルフィド結合を有するポリエチレングリコール化合物、及び銅イオンを含有することを特徴とする無電解銅めっき液、さらに、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6を形成することを特徴とする無電解銅めっき方法、及び、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6からなる埋め込み配線を形成することを特徴とする埋め込み配線の形成方法。

(もっと読む)

Cu系配線材料前駆体、Cu系配線材料およびこれらの形成方法

【課題】Cu-Ti系スパッタ膜を従来よりも低い温度で熱処理しても、配線表面にTi系自己拡散バリア膜を形成できるようにする。

【解決手段】極薄のTi系膜を第一の膜2として基材1上に形成した後、Ti系材料のTi系材料とCu系材料との傾斜構造を持つ複合膜を第二の膜3として形成し、その上にCu系電極となる第三の膜4を形成することにより、3層構造の前駆体を形成する。この前駆体を450℃以下で熱処理することで、Ti系バリア膜を有するCu系電極を形成することが可能となる。

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】基板側から順に、絶縁膜と、Cu合金膜と、薄膜トランジスタの酸化物半導体層と、を備えた配線構造であって、TiやMoなどのバリアメタル層を省略してCu合金膜を、基板および/または絶縁膜と電気的に直接接続しても、これらとの密着性に優れており、しかもCu系材料の特徴である低電気抵抗、並びに酸化物半導体層および/または画素電極を構成する透明導電膜との低いコンタクト抵抗を実現できる新規な表示装置用Cu合金膜を有する配線構造を提供する。

【解決手段】本発明の配線構造において、Cu合金膜は、Mn、Ni、Zn、Al、Ti、Mg、Ca、W、およびNbよりなる群から選択される少なくとも1種の元素を含有している。上記Cu合金膜は、基板および/または絶縁性、並びに半導体層と直接接続されている。

(もっと読む)

半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲット

【課題】 バリア膜形成による配線の抵抗値増大及びボイドの発生を防ぐことができる半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲットを提供すること。

【解決手段】 Si酸化物を含む絶縁膜1にCuの配線が設けられている半導体装置であって、絶縁膜1に設けられた溝状の開口部1aの内面に形成されたバリア膜4と、開口部1a内であってバリア膜4上に形成されたCuからなる配線本体2と、を備え、バリア膜4が、バリア膜4が、少なくとも絶縁膜1上に形成されたBa酸化物及びSr酸化物の少なくとも一方を含有するCu合金下地層を有し、該Cu合金下地層と絶縁膜1との界面にBaSi酸化物及びSrSi酸化物の少なくとも一方が偏析している。

(もっと読む)

61 - 80 / 317

[ Back to top ]