Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

2,241 - 2,260 / 2,960

半導体装置の製造方法

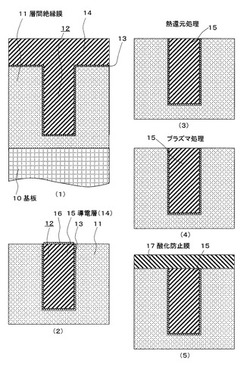

【課題】水素を主成分とした還元性ガスを用いた熱還元処理および還元性ガスを用いたプラズマ処理を併用して行うことで、自然酸化膜の除去を可能とする。

【解決手段】基板10に形成された層間絶縁膜11に、表面が露出する様に銅を含む導電層15を形成する工程と、前記導電層15表面に対して水素を主成分とした還元性ガスを用いた熱還元処理を行う工程と、前記導電層15表面に対して還元性ガスを含むプラズマ処理を行うことによって前記導電層15表面に対して還元処理を行うとともに前記熱還元処理により吸着された水素を脱離させる工程と、前記プラズマ処理後の前記導電層15表面が酸素を含む雰囲気にさらされることなく前記導電層15表面を被覆する酸化防止膜17を形成する工程とを備えた半導体装置の製造方法である。

(もっと読む)

外部接続端子

【課題】基板上に形成される外部接続端子に関し、電極、配線又はパッドとして使用される金属パターンとはんだとの密着性を向上すること。

【解決手段】外部接続端子は、基板上又は基板上の絶縁膜の上に形成された電極と、電極上に形成されてリン又はホウ素のいずれかの第1元素を含有する第1元素含有ニッケル銅層と、第1元素含有ニッケル銅層の上に形成され且つ第1元素を第1元素含有ニッケル銅層よりも多く含む高第1元素含有ニッケル銅層と、高第1元素含有ニッケル銅層の上に形成されたニッケル銅錫合金層と、ニッケル銅錫合金層の上に形成された錫合金はんだ層とを有する。前記錫合金はんだ層は、銅を含んでいるようにしても良い。

(もっと読む)

半導体装置及びその製造方法

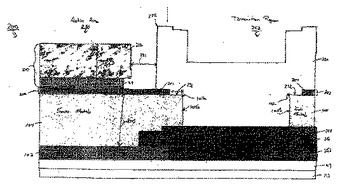

【課題】 容量密度を高めることが可能な、立体構造のMIMキャパシタにおいてMIMキャパシタ直下の配線領域が配線として利用でき、配線層数の増大や、ICチップ面積の増大を防ぐことのできるMIMキャパシタを備えた半導体装置及びその製造方法を提供する。

【解決手段】 下層配線を被覆するように層間絶縁膜301を形成し、層間絶縁膜に対し、下層配線の上面を基準とする層間絶縁膜の膜厚よりも小さな高さの開口部を形成し、開口部を被覆するように上部電極204、容量膜401、下部電極203から構成されるMIMキャパシタを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性を向上させるとともに配線の高抵抗化を防ぐ半導体装置の製造方法および半導体装置を提供する。

【解決手段】基板11上に下層側に酸素含有絶縁層21aを有する層間絶縁膜21を形成する。次に、層間絶縁膜21の上層側に配線溝22を形成し、酸素含有絶縁層21aに接続孔23を形成する。次いで、接続孔23の側壁が露出するように配線溝22の内壁を覆う状態で、層間絶縁膜21上に、第1のバリア膜24を形成する。次に、配線溝22と接続孔23の内壁を覆う状態で、CuMn合金膜25を形成する。続いて、配線溝22と接続孔23とを埋め込む状態で、CuMn合金膜25上に銅を含む導電層26を形成する。その後、熱処理を行い、CuMn合金膜25中のMnを拡散させて、酸素含有絶縁層21a中の酸素と反応させることで、接続孔23の側壁に、金属含有酸化物からなる第2のバリア膜27を形成することを特徴とする半導体装置の製造方法および半導体装置である。

(もっと読む)

二重ダムシーン相互接続上のキャッピング層形成

半導体装置について導電性相互接続上のキャッピング層を形成するための方法を提供し、この方法は、次の工程、即ち、(a)1種又はそれよりも多くの導体を誘電体層において提供する工程、及び(b)キャッピング層を少なくとも若干の1種又はそれよりも多くの導体の上側表面上に堆積する工程を備え、方法に更なる工程、即ち、(c)キャッピング層を堆積するのに先立ち、誘電体層を有機化合物と液相において反応させる工程であり、前記有機化合物は、以下の一般式、即ち、

の(I)を持ち、そこで、Xは官能基であり、Rは有機基又はオルガノシロキサン基であり、Y1は官能基又は有機基又はオルガノシロキサン基のいずれでもよく、及びY2は官能基又は有機基又はオルガノシロキサン基のいずれでもよく、及びそこで、官能基(群)は、無関係に以下の、即ち、NH2、2級アミン、3級アミン、アセトアミド、トリフルオロアセトアミド、イミダゾール、ウレア、OH、アルキオキシ、アクリルオキシ、アセタート、SH、アルキルチオール、スルホナート、メタンスルホナート、及びシアニド、及びそれらの塩から選ばれる工程が含まれることにおいて特徴付けられる。  (もっと読む)

(もっと読む)

半導体ウエハの貫通ホールめっき方法

本発明は、半導体要素を製作するために、半導体ウエハ内に垂直貫通コンタクト(マイクロ・ビア)、すなわち、ウエハの前側から半導体ウエハを貫通してウエハの後側にいたるコンタクトを形成する方法に関する。本発明はまた、以下のステップを含む方法にも関する、すなわち、コンタクト接続点上のブラインド・ホールがウエハの後側から半導体基板内へレーザ穴開けされ、ウエハが洗浄され、ウエハの活性層スタックに到達するまで半導体基板が材料選択性の方法でプラズマ・エッチングされ、ウエハの後側に接続される予定のコンタクトに到達するまで、ウエハの活性層スタックが材料選択性の方法でプラズマ・エッチングされ、めっきベースがウエハの後側およびブラインド・ホール内に適用され、金が電気めっきによりウエハの金属化された後側およびブラインド・ホール上に適用される。 (もっと読む)

配線構造およびその製造方法

【課題】金属キャップの横方向の成長を無くし、その選択的成長を良好に調整することが可能な配線構造およびその製造方法を提供する。

【解決手段】誘電体層30のビア部およびトレンチ部に、誘電体層30の上表面よりも低い上表面を有する銅50’を充填し、上部に銅凹部52を有するダマシン構造を形成する。銅凹部52に金属コバルト,コバルトタングステン,コバルトタングステンリン化合物,またはコバルトタングステンホウ化物からなる金属キャップ54を形成する。

(もっと読む)

半導体デバイスの電極のための保護バリア層

【課題】 無鉛はんだに含まれている酸性のフラックスから電極を保護し、それによって、その下の活性な半導体接合を保護するバリア層を電極の直上に設けた半導体デバイスを提供する。

【解決手段】 半導体デバイスは、1つの表面上に、少なくとも1つの電極を有する半導体ダイと、電極の上方に形成されている少なくとも1つのはんだ付け可能なコンタクトと、電極の上方に形成され、かつ、はんだ付け可能なコンタクトを露出する開口を有するパッシベーション層とを備え、パッシベーション層の開口は、はんだ付け可能なコンタクトよりも広く、はんだ付け可能なコンタクトとパッシベーション層との間に、空隙が存在する。さらに、電極の上面上であって、はんだ付け可能なコンタクトの下面に沿って、および、空隙の全域にわたって、バリア層を配置されている。バリア層は、パッシベーション層の下に広がっている場合もあり、また、電極の全上面を覆っている場合もあり、さらに、電極の側壁に沿って広がっている場合もある。バリア層は、チタン層を備えている場合もあり、チタン層とニッケル層とを備えている場合もあり、電極およびその下の半導体ダイを、無鉛はんだに含まれている酸性のフラックスから保護する。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】シード層から導電部表面に拡散して酸化物を形成する金属の酸化物層で形成することで、配線信頼性の向上、微細化によるRC遅延の問題を解決することを可能とする。

【解決手段】基板11上の絶縁膜(層間絶縁膜21)に形成された凹部22の内面にバリア層25を介してシード層26を形成する工程と、シード層26を介して凹部22を導電部(銅)27で埋め込む工程と、層間絶縁膜21上に形成された銅およびシード層26を除去して、凹部22内に銅を主材料とする導電部27を形成する工程とを備えた半導体装置の製造方法であって、シード層26は導電部27表面に拡散して酸化物を形成する金属を含む銅材料で形成され、凹部22内に銅を主材料とする導電部27を形成した後に熱処理を行って導電部27表面に酸化物を形成する金属を含む酸化物層31を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ウェハのエッジ部からの膜剥がれを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】Cu配線工程において、有機系低誘電率層間膜32形成後に、ウェハベベルの側面上および裏面上、ウェハエッジの裏面上に保護膜33を堆積させる。その後、リソグラフィ工程およびエッチング工程を経て銅膜を形成した後に保護膜33を除去する。

(もっと読む)

シリカ系被膜の製造方法、シリカ系被膜および半導体装置

【課題】 誘電率と被膜強度を表わすヤング率とに優れたシリカ系被膜、特に、比誘電率が2.7以下と小さく、さらに被膜強度を表わすヤング率が半導体配線層作製プロセスに耐えうるだけの強度特性を備えたシリカ系被膜の形成方法を提供する。

【解決手段】 (i)シリカ系被膜形成用塗布液を基板上に塗布し、(ii)塗布後の基板を加熱処理し、(iii)加熱後の基板に、ケイ素の不対電子を安定化できる物質を含む雰囲気中で活性エネルギー線を照射して、シリカ系被膜を得る。

(もっと読む)

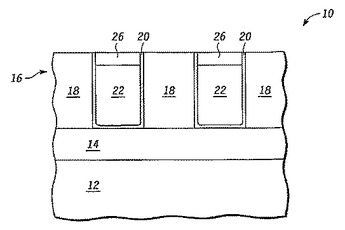

キャップ層を半導体素子の上に形成するための方法

半導体素子を形成する方法は、複数の空洞(15)を有するパターニング済み誘電体(18)を能動回路の上に形成する工程を含む。拡散バリア(20)をパターニング済み誘電体(18)の上に形成する。導電層(22)を複数の空洞の中の拡散バリアの上に形成する。導電層を、導電層が誘電体の上部表面の下方に位置するようにエッチバックして、後退領域(24)を、複数の空洞の中の導電層の上に形成する。次に、後退領域にキャップ膜(26)を充填する。キャップ膜及び拡散バリアを除去すると、非常に平滑な平坦化表面が得られる。非常に平滑な平坦化表面を形成することにより、複数の導体の間のリーク電流を低減する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の微細化にともない、金属配線の表面の凹凸によって電子が散乱され、配線の電気伝導度が低下し電気抵抗が増加する。これを抑制する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上の低誘電率絶縁膜22に配線溝28tと接続孔26hを形成する。溝内部にバリアメタル24を形成するがこの表面は必ずしも平滑ではない。そこで、CMPスラリを溝内部に循環させることによりバリアメタルの表面を平滑にする。CMPスラリには研磨砥粒とエッチング液が含まれているため凹凸を有するバリアメタルの凸部を研磨、除去することができる。この後Cuを堆積し溝部以外のCuを除去すると表面粗さの小さいCu配線28を形成することができる。

(もっと読む)

電解加工装置および電解加工方法

【課題】例えばダマシン法により基板上の配線を形成する場合に、基板にダメージを与えることなく、低い圧力で基板の表面を全面にわたって均一に平坦化することができる電解加工装置を提供する。

【解決手段】電解加工装置10は、表面に金属膜が形成されたウェハを保持しつつ、ウェハを回転させるウェハホルダ14と、ウェハに対して電解加工を行う電解加工ユニット16とを備えている。電解加工ユニット16は、回転可能な加工電極52と、加工電極52に取り付けられた研磨パッド53と、研磨パッド53をウェハに押圧する押圧機構72と、電解加工液をウェハと加工電極52との間に供給する液供給機構と、ウェハと加工電極52とを相対運動させる相対運動機構と、加工電極52がカソード、ウェハの金属膜がアノードとなるように、加工電極52とウェハの金属膜との間に電圧を印加する電源103とを備えている。

(もっと読む)

膜パターンの形成方法、デバイス、電気光学装置、電子機器、及びアクティブマトリクス基板の製造方法

【課題】幅の異なる幾つかの領域を有するパターン形成領域に機能液を配置する場合等において、形成される膜パターン間での膜厚さを無くした該膜パターンの形成方法を提供する。

【解決手段】本発明の膜パターンの形成方法は、基板18上に第1バンク層35と第2バンク層36とを積層形成する工程と、前記第1バンク層35及び第2バンク層36をパターニングすることで、第1のパターン形成領域56と、該第1のパターン形成領域56に連続し、かつ該第1のパターン形成領域56より幅が広い第2のパターン形成領域55とからなるパターン形成領域13を有するバンク34を形成する工程と、を有し、前記第1バンク層35、第2バンク層36の形成材料がいずれもシロキサン結合を主鎖としてなる材料であり、前記第2バンク層の形成材料が、側鎖にフッ素結合を有する材料であることを特徴としている。

(もっと読む)

半導体装置の製造方法

【課題】銅配線形成時のディッシングを防止する。

【解決手段】半導体基板12上面12a上の第1絶縁膜14の表面を覆う拡散防止膜22、拡散防止膜上を覆う第2絶縁膜24、及び第2絶縁膜上を覆うキャップ膜26を順次に積層する。拡散防止膜、第2絶縁膜及びキャップ膜を貫通する配線溝部30であって、この配線溝部の底面からキャップ膜の表面までの高さh1に対する、配線溝部の延在方向に直交する方向の幅w1の比率を最大でも2.8倍として当該配線溝部を形成する。キャップ膜の表面及び配線溝部の表面を覆うバリアメタル膜を形成する。バリアメタル膜上を覆う配線膜を成膜する。配線膜の表面からキャップ膜の表面が露出するまで、配線膜及びバリアメタル膜を削り取って、配線溝部を埋め込む配線部を形成する。

(もっと読む)

電解加工方法および基板処理方法

【課題】ダマシーン法による基板上の配線形成において、微細な凹凸を有する基板上の金属膜の表面を低い加工圧力で平坦化することができ、かつ金属膜をその全面に亘って均一な加工速度で加工することができる電解加工方法を提供する。

【解決手段】給電電極31と加工電極32とをテーブル12上に配置し、給電電極31と加工電極32の間に絶縁体36を配置し、金属膜6が給電電極31および加工電極32に対向するように基板Wを絶縁体36に接触させ、第1の電解液および第2の電解液を、絶縁体36により電気的に絶縁させた状態で給電電極31と基板Wとの間、および加工電極32と基板Wとの間にそれぞれ供給し、給電電極31と加工電極32との間に電圧を印加し、基板キャリアー11とテーブル12を相対運動させて基板W上の金属膜6の電解加工を行う。

(もっと読む)

障壁金属スペーサを備える半導体素子及びその製造方法

【課題】障壁金属スペーサを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板に形成された第1金属ラインと、第1金属ラインの一部分と電気的に連結されたビアプラグを備え、ウィンドウを含むエッチング停止膜と、ビアホール及びトレンチを含む層間絶縁膜と、ビアホール内の層間絶縁膜の側壁を覆っており、第1金属ラインの一部分を露出し、ウィンドウ内のエッチング停止膜の少なくとも側壁の下端を露出する第1障壁金属スペーサと、を備える半導体素子である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】多孔質膜の絶縁耐性が安定するとともに、隣接する配線間におけるリーク電流等が生じることがなく、配線の信頼性を向上させた半導体装置の製造方法が提供する。

【解決手段】半導体基板12上に、多孔質膜16を形成する工程と、多孔質膜16に半導体基板12の表面が底部に露出した凹部22を形成する工程と、凹部22の内壁と多孔質膜16の全面を覆うように非多孔質膜24を形成する工程と、異方性エッチングにより、凹部22の底部に形成されている非多孔質膜24と、多孔質膜16上に位置する非多孔質膜24とを選択的に除去する工程と、凹部22を埋設するようにバリアメタル膜28と金属膜を形成する工程とを含む。異方性エッチングを行う工程が、式:(窒素含有化合物ガス+不活性ガス)/フッ素含有化合物ガスで表される混合比を45以上100以下としたエッチングガスにより行われる。

(もっと読む)

半導体装置の製造方法

【課題】 本発明の目的は、製造プロセスの容易化及び信頼性の向上を図ることにある。

【解決手段】 半導体装置の製造方法は、(a)電極パッド16及びパッシベーション膜18を有する半導体基板10の上方に、樹脂層30を形成する工程と、(b)樹脂層30をキュアすることにより、樹脂突起40を形成する工程と、(c)電極パッド16と電気的に接続する導電層50を、電極パッド16の上方から樹脂突起40の上方に至るように形成する工程と、(d)検査端子70の成型面72により導電層50を介して樹脂突起40を押し潰すことにより、樹脂突起40を成型するとともに電気的検査を行う工程と、を含む。

(もっと読む)

2,241 - 2,260 / 2,960

[ Back to top ]