Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

341 - 360 / 2,960

薄膜トランジスタ表示板の製造方法

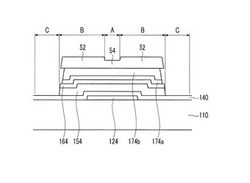

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

半導体装置

【課題】ディッシング及び埋め込み不良のないパッド構造を短時間で安定して形成する。

【解決手段】基板100上に形成された第1の絶縁膜108Bに、複数のパッド配線109pを含むパッドが形成されている。第1の絶縁膜108B上に、前記パッドの少なくとも一部分の上に位置する開口部を有する第2の絶縁膜110が形成されている。複数のパッド配線109pのうち互いに隣り合う配線同士を電気的に接続するように配線接続部109qが設けられている。各パッド配線109pの幅W1は、各パッド配線109pの高さよりも小さく且つ配線接続部109qの幅W3よりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】機械的強度および密着力に優れた低誘電率の層間絶縁層を有する半導体装置を提供すること。

【解決手段】基板上に形成された、SiO2骨格を含む第1の多孔質層6と、第1の多孔質層6の直上に形成された、SiO2骨格を含む第2の多孔質層7と、第1の多孔質層6に埋め込まれたビア10と、第2の多孔質層7に埋め込まれた配線11と、を有し、第1の多孔質層6の孔密度x1は40%以下であり、第2の多孔質層7の孔密度x2は、(x1+5)%以上である半導体装置を提供する。

(もっと読む)

半導体デバイス製造方法

【課題】バリア金属膜とCVD法によって形成される金属導体膜である銅膜との間の密着性に優れた半導体デバイスの製造方法を提供すること。

【解決手段】基板上に直接にまたは絶縁体膜を介してバリア金属膜を形成する工程と、該バリア金属膜上にCVD法によって銅膜を形成する工程とを含む半導体デバイス製造方法において、該バリア金属膜を形成する工程と該銅膜を形成する工程との間に、加熱条件下アンモニア、水素、またはシランのうちの少なくともいずれか1つを含む第1の還元性ガスに暴露する工程と、該銅膜を形成する工程の後に、加熱条件下第2の還元性ガスに暴露する工程と、を有することを特徴とする。

(もっと読む)

マスクおよびその製造方法、半導体ウエハ

【課題】半導体ウエハ面内における金属配線の抵抗分布のばらつきを抑え、得られるデバイスの特性や精度を面内で均一化させることが可能なマスクを提供する。

【解決手段】本発明のマスクは、金属配線を有するデバイス10を基板2の一面上に多数形成する際に、該基板の一面に対向配置されて用いられるマスクであって、個々の前記デバイスが配される前記基板上の位置に応じて、それぞれのデバイスが有する前記金属配線に対応する部位の形状を変えたこと、を特徴とする。

(もっと読む)

プラズマ処理方法及び半導体装置の製造方法

【課題】サイドエッチングによるパターン細りを抑制しつつ、ドライ処理によってパターン側壁に堆積した金属を含む堆積物を効率良く除去することのできるプラズマ処理方法及び半導体装置の製造方法を提供する。

【解決手段】基板に形成された金属層をプラズマエッチングする工程を経て積層構造中に金属層を有するパターンを形成した後、金属層を構成する金属を含みパターンの側壁部に堆積した堆積物を除去するプラズマ処理方法であって、金属層の側壁部に当該金属の酸化物又は塩化物を形成する保護層形成工程と、フッ素原子を含むガスのプラズマを作用させて堆積物を除去する堆積物除去工程と、保護層形成工程及び堆積物除去工程の後、水素を含むプラズマを作用させて金属の酸化物又は塩化物を還元する還元工程とを具備している。

(もっと読む)

半導体装置の製造方法

【課題】CMP法による研磨のばらつきを抑制できる半導体装置の製造方法を提供する。

【解決手段】ウェハ1の周辺領域2の第3層間絶縁膜に、ダミーパターン41を形成する。ダミーパターン41は、ウェハ1の接線及び法線に交差する斜パターン42と、斜パターン42に連結され、ウェハ1の周方向に延びる分離パターン43とを有する。配線溝に導電性材料を埋め込んだ後に、CMP法により余分な導電性材料を除去するときは、ダミーパターン41に形成された溝を通って研磨剤が分散されるので、導電性材料や第3層間絶縁膜の研磨量が均一になる。

(もっと読む)

半導体装置及びその製造方法

【課題】パッシベーション膜にクラックを生じさせるか否かを容易に判定できる構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、下部電極23の上面に達する接続孔30hを持つパッシベーション膜30を備える。パッシベーション膜30は、接続孔30hを除いて下部電極23の周縁部を含む領域を被覆する。下部バリアメタル膜31は、下部電極23とパッシベーション膜30の凸状部分30bとを被覆するように形成されている。バンプ電極35から離れた領域でパッシベーション膜30に形成されている段差部分を被覆するように金属膜パターン31Tが形成されている。

(もっと読む)

導電部形成方法、導電部及び発光装置

【課題】導電部の欠損を防止すること。

【解決手段】Al含有膜2からなるゲートラインLgやコンタクト部42などの導電部を形成する際に、下層保護導電膜/Al含有膜/上層保護導電膜の導体膜を成膜した後、その導体膜に改質処理として酸化処理を施して、上層保護導電膜3で覆われずにピンホールPから露出してしまったAl含有膜2部分に酸化保護領域4を形成することによって、Al含有膜2がレジストの剥離液などに晒されて消失してしまうことを防ぎ、導電部の欠損を防止した。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

Co膜形成方法

【課題】膜中及び膜表面の不純物が効果的に除去でき、Cu配線構造に適用したときにバリア層及びCu配線層に対する密着性に優れて一層の低抵抗を実現できるCo膜形成方法を提供する。

【解決手段】基材Sを処理室10内に配置して処理室内を真空引きすると共に、基材を一の所定温度に加熱し、アルキル基を有するイオン又は分子がコバルトに配位した有機金属材料Lを気化させ、気化させた有機金属材料を基材表面に供給し、有機金属材料を熱分解させてCo膜を成膜する。その後、同一の処理室内で、またはCo膜が成膜された基材を他の処理室内に配置し、この基材をアンモニアガスと水素ガスとを含む混合ガス雰囲気中にて他の所定温度でアニールする。

(もっと読む)

固体撮像装置

【課題】 暗電流やリーク電流の発生を抑制することが可能な固体撮像装置を提供する。

【解決手段】 固体撮像装置は、光電変換素子が主面に配された第1基板と、導電体を含む第1の接合部を有する第1配線構造と、周辺回路の一部が主面に配された第2基板と、導電体を含む第2の接合部を有する第2配線構造と、を有する。そして、第1基板と、第1配線構造と、第2配線構造と、第2基板とがこの順に配置されるように第1の接合部及び第2の接合部とが接合されている。そして、第1の接合部の導電体と、第2の接合部の導電体とは、導電体に対する拡散防止膜で囲まれている。

(もっと読む)

半導体装置の製造方法

【課題】ビアを形成するとともに配線を形成する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、まず、第1のパターンを導電体上に形成された被加工材に転写することにより、第1のパターンを有する第1の溝を被加工材の上部に形成する工程を行い。次に、第1のパターンと一部が重なる第2のパターンを被加工材に転写することにより、第1および第2のパターンの和集合からなるパターンを有する第2の溝を被加工材の上部に形成し、第1および第2のパターンの積集合からなるパターンを有し、底部に導電体が露出する孔を被加工材の第2の溝の下に形成する工程を行い。孔内にビアを形成し、第2の溝内に配線を形成する工程を行う、ことを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留まりの低下を抑制する半導体装置及びその製造方法を提供する。

【解決手段】実施の形態の半導体装置1は、配線20を有する配線層11bと、配線層11b上に形成された層間絶縁膜26と、層間絶縁膜26上に形成され、上部がシリサイド化されたアモルファスシリコン層27を有するTFT14と、TFT14上に、層間絶縁膜47を介して形成された配線50を有する配線層12aと、層間絶縁膜47、アモルファスシリコン層27及び層間絶縁膜26を貫通し、第1及び第2の配線を電気的に接続するコンタクトプラグ32と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】高さのばらつきが低減された埋め込みビット線を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板内にビット線とワード線を有する半導体装置の製造方法において、半導体基板をエッチングして第1の方向に延在する第1の溝を形成することによって、複数の第1の半導体ピラーを形成する工程と、第1の半導体ピラーの側面の一部に拡散層を形成する工程と、隣接する前記第1の半導体ピラー間の前記第1の溝に、拡散層に接続するビット線を形成する工程と、第1の半導体ピラーと前記ビット線を覆う第1の絶縁膜を形成する工程と、第1の半導体ピラーの少なくとも一部が露出するように前記第1の絶縁膜に、第1の方向に直交する第2の方向に延在する第2の溝を形成する工程と、露出した第1の半導体ピラー上にエピタキシャル層を成長させて第2の半導体ピラーを形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置の配線形成方法、半導体装置の製造方法および半導体装置の配線形成システム

【課題】絶縁層の凹部に導電体を十分に充填させることができる半導体装置の配線形成方法を提供する。

【解決手段】はじめに、低誘電率層21上に所定パターンで形成されたメタルハードマスク層25をマスクとして低誘電率層21をエッチングすることにより形成された凹部24を有する基板を準備する。次に、低誘電率層21上のメタルハードマスク層25を薬液により除去する。その後、低誘電率層21の凹部24に導電体23を充填する。このようにして、ダマシン法により、半導体装置30の配線が形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】研磨工程を含む新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、絶縁膜を形成する工程と、絶縁膜に、第1の深さを有するダミー溝と、第1の深さよりも深い第2の深さを有する配線溝と、配線溝の底面に配置されるビアホールとを形成する凹部形成工程と、ダミー溝内、配線溝内、ビアホール内、及び絶縁膜上方に、導電材を堆積させる工程と、絶縁膜上方の導電材を研磨除去する工程とを有する。

(もっと読む)

低誘電率材料形成用原料

【課題】 耐水性に優れた低誘電率材料を得る。

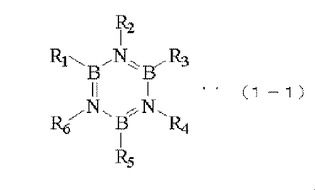

【解決手段】 化学式(1―1)

【化1】

で示されるボラジン系原料を有機溶媒に分散または溶解させたものを低誘電率材料形成用原料とする。式中のホウ素原子もしくは窒素原子が備える手が結合手となってボラジン環が結ばれたボラジン骨格系構造を形成し、上記ボラジン骨格系構造が繰り返されたオリゴマーまたはポリマーとして低誘電率材料を生成する。ただし式中、上記結合手以外のR1〜R6は、水素原子、炭素原子数1〜2のアルキル基の少なくともいずれかであって、少なくとも1つは水素原子ではなく、少なくとも1つは水素原子である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】生産性の低下を抑制しつつ、配線部分の抵抗の増大を抑制することができるとともに、電気的なリークの発生を抑制することのできる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】層間絶縁膜としてポーラス状の低誘電率膜を有する半導体装置を基板上に形成する半導体装置の製造方法であって、前記基板に前記低誘電率膜を形成する低誘電率膜形成工程と、エッチングにより前記低誘電率膜にトレンチ又はホールを形成するエッチング工程と、前記トレンチ又はホール内に、ニトロ化合物のプラズマを作用させて前記低誘電率膜のエッチングにより露出された面を改質する改質工程と、前記トレンチ又はホール内に導体を充填する導体形成工程と、を具備している。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

341 - 360 / 2,960

[ Back to top ]