Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

301 - 320 / 2,960

装置

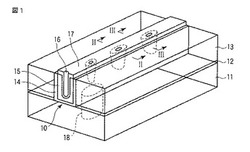

【課題】ボイドが存在しても高い信頼性を確保可能な配線構造を提案する。

【解決手段】実施形態に係わる装置は、第1の溝10を有する絶縁層13と、第1の溝10内に形成され、上部に凹部16を有する銅を含む第1の配線層15と、第1の配線層15の凹部16の内面上に形成され、少なくとも1つのグラフェンシートから構成されるグラフェン層17とを備える。

(もっと読む)

半導体装置の製造方法

【課題】微細で良好な形状のコンタクトホールを有する半導体装置の製造方法を提供する。

【解決手段】絶縁膜36上にフォトレジスト膜42を形成する工程と、フォトレジスト膜42に開口部44を形成する工程と、開口部44が形成されたフォトレジスト膜42をマスクとして絶縁膜36をエッチングすることによりコンタクトホール48を形成する工程とを有し、コンタクトホール48を形成する工程は、開口部44が形成されたフォトレジスト膜42上に保護膜46を堆積しながら絶縁膜36をプラズマエッチングする第1の工程と、フォトレジスト膜42上に堆積された保護膜46を一旦除去する第2の工程と、保護膜46が一旦除去されたフォトレジスト膜42上に他の保護膜を新たに堆積しながら絶縁膜36を更にプラズマエッチングする第3の工程とを含んでいる。

(もっと読む)

成膜方法及び成膜装置

【課題】 ボイド等の発生を防止できるように凹部内に金属膜の成膜を施すことができる成膜方法である。

【解決手段】 処理容器22内でプラズマにより金属のターゲット76から金属イオンを発生させてバイアスにより引き込んで凹部4が形成されている被処理体に金属の薄膜を堆積させる成膜方法において、ターゲットから金属イオンを生成し、その金属イオンをバイアスにより引き込んで凹部内に下地膜90を形成する下地膜形成工程と、金属イオンを発生させない状態でバイアスにより希ガスをイオン化させると共に発生したイオンを引き込んで下地膜をエッチングするエッチング工程と、ターゲットをプラズマスパッタリングして金属イオンを生成し、その金属イオンをバイアス電力により引き込んで金属膜よりなる本膜92を堆積しつつ、その本膜を加熱リフローさせる成膜リフロー工程とを有する。

(もっと読む)

半導体ウェハおよびそれにより形成した半導体装置

【課題】半導体ウェハの保護層に形成された溝のアスペクト比が0.5以上である場合においても、再配線を形成する際のレジスト膜に破壊が生じることを防止する手段を提供する。

【解決手段】半導体ウェハが、集積回路を形成した複数の能動領域と、隣合う能動領域間に設けられたダイシング領域と、能動領域とダイシング領域とを覆う保護層5と、保護層の能動領域の外側を掘込んで形成されたガイド溝21と、能動領域の保護層上を覆う保護膜7と、保護膜上に形成され、集積回路に電気的に接続する第2の配線9とを備え、ガイド溝のアスペクト比が0.5以上の場合にそのガイド溝を保護膜で覆う。

(もっと読む)

配線形成方法

【課題】下層配線層と配線シード層との密着性を低下させないで高く維持することが可能な配線形成方法を提供する。

【解決手段】下層配線層4と絶縁性バリヤ層6と層間絶縁膜8と上層配線層が順次積層された被処理体に対して上層配線層と、連通配線層16とを形成する配線形成方法において、絶縁性バリヤ層を残した状態で連通ホール9Bを形成し、連通ホール内に犠牲膜を埋め込み、トレンチ9Aを形成するパターンマスク62を形成する前処理工程と、トレンチを形成するトレンチ形成工程と、犠牲膜60とパターンマスクとをアッシングするアッシング工程と、トレンチ内と連通ホール内に熱処理によりバリヤ層10を形成するバリヤ層形成工程と、異方性エッチングにより連通ホールの底部のバリヤ層と絶縁性バリヤ層とを除去する異方性エッチング工程と、配線シード層12を形成する配線シード層形成工程とを有する。

(もっと読む)

半導体装置

【課題】抵抗値の温度依存性の小さい抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、金属抵抗素子層Rm1,Rm2を有する。金属抵抗素子層Rm1は、金属抵抗膜層Rm11を含む。金属抵抗素子層Rm2は、金属抵抗膜層Rm12を含む。金属抵抗膜層Rm11は、窒化チタン抵抗および窒化タンタル抵抗のうちの一方であり、金属抵抗膜層Rm12は、窒化チタン抵抗および窒化タンタル抵抗のうちの他方である。窒化チタン抵抗の抵抗値は正の温度係数を有する一方、窒化タンタル抵抗の抵抗値は負の温度係数を有する。コンタクトプラグCP2によって、金属抵抗膜層Rm11と金属抵抗膜層Rm12とが電気的に接続されるので、窒化チタン抵抗の温度係数と窒化タンタル抵抗との温度係数が相殺される。これにより温度係数を小さくすることができる。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタル層の金属配線に対する密着性を向上させつつ、金属配線の低抵抗化を図った半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜15に形成された凹部16、17内にバリアメタル層20を形成した後、凹部16、17内にCu配線層23を形成する。バリアメタル層20の形成工程は、凹部16、17内にTi含有量が50原子%を超える第1のTiNx膜18を形成した後、側壁部上と比較して底部上に相対的に多く形成されるように、Ti含有量が第1のTiNx膜18より多い第2のTiNx膜(またはTi膜)19を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置の製造システム

【課題】ダマシン配線構造を有する半導体装置において、CMP法によるCu配線への処理により発生するCu配線の腐食(コロージョン)の発生を防止し、配線抵抗の上昇を抑制し、信頼性の担保された半導体装置の製造方法および半導体装置の製造システムを提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法であって、基板上の層間絶縁膜に形成される配線パターン溝にバリアメタル膜およびCu膜が形成された状態で、ケミカルメカニカルポリッシングによって配線パターン溝以外に堆積したCuを除去する工程と、配線パターン溝以外に堆積したバリアメタルをケミカルメカニカルポリッシングによって除去する工程と、前記バリアメタルを除去する工程後、除電する工程と、基板上に残るスラリーおよび残渣物を洗浄する工程と、を有する半導体装置の製造方法が提供される。

(もっと読む)

半導体ウエハ装置およびその製造方法

【課題】 所望の配線構造を形成することができ、かつウエハ有効領域の欠陥率の増加を防止することのできる半導体ウエハ装置の製造方法を提供する。

【解決手段】 半導体ウエハ装置の製造方法は、(a)回路領域に半導体素子を形成した半導体ウエハ上に半導体素子に接続された下層配線パターンを形成する工程と、(b)下層配線パターンを覆って半導体ウエハ上に層間絶縁膜を形成する工程と、(c)回路領域上で下層配線パターンに接続されたビア導電体とその上に配置された配線パターンとを、回路領域外の周辺領域上で配線パターンに対応する導電体パターンを、層間絶縁膜に埋め込んで形成する工程とを含む。導電体パターンは電気的に分離された状態で形成される。

(もっと読む)

半導体装置の製造方法

【課題】めっき工程の埋設不良を抑制する。

【解決手段】半導体基板100上に設けられた層間絶縁膜320に開口部を形成する工程と、開口部上面にバリア層340を形成するバリア層形成工程と、バリア層340上に配線シード層を形成する配線シード層形成工程を有する。また、バリア層形成工程は、選択成膜工程と、スパッタエッチング工程を有する。バリア層340の選択成膜工程は、バリア層340を、開口部の平面部342のみに選択的に成膜する。次いで、バリア層340のスパッタエッチング工程は、平面部342のバリア層340をスパッタエッチングしながらバリア層340のスパッタ粒子を開口部の側壁部344に堆積させる。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシン配線構造を有する半導体装置において、フルオロカーボン膜へのエッチングダメージによるCu配線構造でのリーク電流の増加や誘電率の低下を抑制し、信頼性の担保された半導体装置の製造方法を提供する。

【解決手段】エッチング処理の施されたフルオロカーボン膜の表面に対し、窒化プラズマ処理またはCFプラズマ処理を行う、半導体装置の製造方法が提供される。これによれば、配線溝形成時のフルオロカーボン膜へのエッチングダメージが修復され、Cu配線構造におけるリーク電流の増加や誘電率の低下を抑制することができる。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

ウエハレベルパッケージ構造およびその製造方法

【課題】切削刃の磨耗を抑制して切削刃の寿命を延ばすことが可能なウエハレベルパッケージ製造方法を提供する。

【解決手段】ウエハレベルパッケージ製造方法は、例えば、基板450の表面に、配線が形成される溝462を含む絶縁性の第1の樹脂460を形成する樹脂形成工程400と、第1の樹脂460の表面に、配線の一部となる第1の金属470を、物理気相成長によって成膜する第1の成膜工程410と、第1の金属470の表面に、配線の一部となる、第1の金属470より硬度が低い第2の金属480を、更に成膜する第2の成膜工程420と、溝462の側面において第1の金属470が成膜されていない場所または薄くなっている場所に該当する高さH0、H1に切削刃490を設置する設置工程430と、切削刃490を走査することにより、少なくとも第1の樹脂460を切削する切削工程440とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の検査効率を向上させる。

【解決手段】複数の接続パッド12が設けられた半導体デバイスウエハ10と、半導体デバイスウエハ10の接続パッド12が設けられた面を被覆するとともに、接続パッド12を露出させる開口14aが設けられた絶縁膜14Aと、開口14aから露出された接続パッド12及び絶縁膜14Aの上部に設けられた配線15Aと、を備える半導体装置である。配線15Aは、無電解めっき用シード層16Aと、無電解めっき用シード層16Aを核とする無電解めっきにより形成される配線層19Aと、を含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】プラズマCVD法を用いてCu配線上に良好な拡散バリア膜を形成する技術を提供する。

【解決手段】ダマシン法を用いて形成したCu配線19上にCuの拡散を防止する窒化シリコン膜21を形成する工程は、Cu配線19が形成された基板1をプラズマCVD装置のチャンバ内に搬入し、基板1を所定の温度に加熱する工程と、チャンバ内にアンモニアを供給し、第1のRFパワーでアンモニアをプラズマ分解することによって、Cu配線19の表面を還元処理する工程と、RFパワーが印加された状態で、チャンバ内にアンモニアとモノシランとを含む原料ガスを供給し、第2のRFパワーでアンモニアとシラン系ガスとをプラズマ分解することによって、Cu配線19上に窒化シリコン膜21を形成する工程とを含んでいる。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、微細化された埋め込みビット線を容易に形成可能であると共に、埋め込みビット線の抵抗値を低くすることで高性能化を実現可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13の主面13aに形成された第1の溝15と、第1の溝15の底面15a、及び第1の溝15の底部15Aに位置するピラー26の側壁面26a,26bに設けられ、側壁面26aを露出する第1の開口部16A、及び側壁面26bを露出する第2の開口部16Bを有した絶縁膜16と、第1の開口部16Aから露出された側壁面26aに形成された半導体基板と反対導電型の下部不純物拡散領域18と、絶縁膜16を介して、第1の溝15の底部15Aに設けられ、第1及び第2の開口部16A,16Bを埋め込むと共に、下部不純物拡散領域18及び側壁面26bと接触し、かつ金属膜よりなる埋め込みビット線21と、を有する。

(もっと読む)

301 - 320 / 2,960

[ Back to top ]