Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

81 - 100 / 2,805

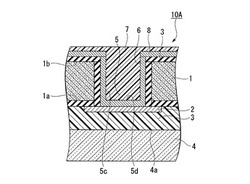

貫通配線付き接合基板

【課題】貫通孔内に配した樹脂が熱膨張することによって電極を破損することを防止した貫通配線付き接合基板の提供。

【解決手段】

一面1aに電極層2が形成された第一基板1、及び電極層2と接合樹脂層3を介して、第一基板1と接合された第二基板4とを備えた貫通配線付き接合基板10Aであって、第一基板1の他面1b側から電極層2が露出するまで第一基板1を貫通する貫通孔5と、貫通孔5の内部において、貫通孔5の内側面5c及び電極層2を覆う貫通配線層6と、貫通配線層6を覆い貫通孔5の内部に充填された充填樹脂部7とを有し、充填樹脂部7を構成する樹脂のヤング率は、接合樹脂層3を構成する樹脂のヤング率よりも小さいことを特徴とする貫通配線付き接合基板10A。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

半導体装置、電子機器、及び、半導体装置の製造方法

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置1を、接合界面Sj側の表面に形成された第1金属膜16を有する第1半導体部10と、接合界面Sjで第1金属膜16と接合された第2金属膜26を有する第2半導体部20と、界面バリア部28とを備える構成とする。第2金属膜26の接合界面Sj側の表面面積は第1金属膜16の接合界面Sj側の表面面積より小さくする。そして、第1金属膜16の接合界面Sj側の面領域のうち第2金属膜26と接合しない面領域を含む領域に界面バリア部28を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】2枚の基板の貼り合わせによって電極間接合がなされた構成において、電極材料の拡散を防止しつつも貼り合わせ強度が確保され、これによって信頼性の向上が図られた三次元構造の半導体装置を提供する。

【解決手段】第1電極33、および第1電極33の拡散防止材料で構成され第1電極33の周囲を覆う第1絶縁膜35を含むと共に、第1電極33と第1絶縁膜35とで貼合せ面41が構成された第1基板2と、第1基板2に貼り合わせて設けられ、第1電極33に接合された第2電極67、および第2電極67の拡散防止材料で構成され第2電極67の周囲を覆う第2絶縁膜69を含むと共に、第2電極67と第2絶縁膜69とで第1基板2に対する貼合せ面71が構成された第2基板7とを備えた。

(もっと読む)

金属付着物の除去方法、基板処理装置、および記録媒体

【課題】有機化合物ガスによる基板処理を清浄に行うことが可能となる金属付着物の除去方法および基板処理装置を提供する。

【解決手段】金属付着物の除去方法は、金属層が形成された被処理基板を処理する処理空間を内部に有する処理容器の内部に付着した金属付着物を昇華させるように、前記処理容器内部の温度と、前記処理空間の圧力とを、制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

半導体装置

【課題】半導体チップのバンプ電極と実装基板の配線との接続信頼性を向上できる技術を提供する。特に、バンプ電極下の最上層配線層に配線を配置しても、バンプ電極の平坦性を確保してバンプ電極とガラス基板に形成されている配線との接続信頼性を向上できる技術を提供する。

【解決手段】バンプ電極BP1の非重複領域Y直下にある最上層配線層に電源配線や信号配線からなる配線L1と、ダミーパターンDPを形成する。ダミーパターンDPは、配線L1間のスペースを埋めるように配置され、配線L1とスペースによって最上層配線層に生じる凹凸を緩和する。さらに、最上層配線層を覆うように形成される表面保護膜に対してCMP法による平坦化処理を実施する。

(もっと読む)

半導体装置およびその製造方法

【課題】前記半導体装置をスクライブ工程により切り離す際に、クラックが歪みを蓄積した保護膜を伝播して半導体装置内部に侵入するのを抑制し、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記保護溝部の底面の一部及び前記保護溝部の内側の側壁面に連続して形成された保護膜と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン基板表面に到達する深い溝部であっても、所望の保護溝部形成を安定して行うことができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜上に下地金属層と上部金属層からなる配線を備えた半導体装置において、下地金属層のサイドエッチングによる絶縁膜と上部金属層との密着性の劣化を抑制することができる半導体装置、及び、その製造方法を提供する。

【解決手段】配線本体16が形成される絶縁膜14の上面には、配線本体16のパターンに対応し、かつ、絶縁膜14の上面から所定の深さの凹部14aが設けられ、当該凹部14aを含む絶縁膜14上面に、配線の一部であり、かつ、密着層であるチタン薄膜15を介して配線本体16が設けられている。凹部14aの幅は、配線本体16の幅よりも狭くなるように設定される。チタン薄膜15は配線本体16の配線幅よりも狭く形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 絶縁膜に、底面及び側面の形状を良好に保って配線溝を形成する技術が望まれている。

【解決手段】 基板の上に、仮のパターンを形成する。仮のパターンを囲むように、基板の上に層間絶縁膜を形成する。層間絶縁膜を形成した後、仮のパターンを除去する。仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する。シード膜の上に、配線材料を堆積させることにより、凹部を配線材料で埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器

【課題】装置の信頼性や、製品の歩留まりなどを向上させる。

【解決手段】第1の開口と第2の開口との内部に金属材料を埋め込んで第1プラグと第2プラグとを設けると共に、第1プラグと第2プラグとの間を接続する接続配線を設けることで、接続導電層を形成する。そして、接続導電層において接続配線の上面を被覆するようにパッシベーション膜を形成する。このパッシベーション膜の形成工程では、高密度プラズマCVD法などのように埋め込み性に優れた成膜法で、SiO2などの絶縁膜を成膜することによって、パッシベーション膜を形成する。

(もっと読む)

成膜装置及び成膜方法

【課題】 タングステン膜を成膜する際に半導体ウェーハがエッチングされることを抑制する成膜装置及び成膜方法を提供することである。

【解決手段】 実施形態に係る成膜装置は、半導体ウェーハを載置するためのステージと、前記ステージ上に載置される半導体ウェーハの周縁部を覆うように配置されるエッジカット部を備え、前記半導体ウェーハ上にタングステン膜を成膜する。前記エッジカット部は、前記半導体ウェーハの周縁部と接触可能に設けられた第1のエッジカット部と、前記第1のエッジカット部に接続され、前記半導体ウェーハと実質的に垂直な方向に上下動可能な接続部と、前記接続部に接続され、前記接続部の上下動により前記半導体ウェーハの内側面に当接するように配置された第2のエッジカット部と、を備える。

(もっと読む)

半導体装置

【課題】多層配線内の信号線とそれに接続されるビアとを共に同軸構造にする。

【解決手段】多層配線には、例えば、異なる層に設けられる信号線10,20と、これらの信号線10,20間を接続する接続部30(ビア)が設けられる。信号線10,20は、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。更に、信号線10,20間を接続する接続部30も、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。信号線10,20のほか接続部30も同軸構造とすることで、信号線10,20及び接続部30を伝送される信号の、周囲からの、又は周囲への、電磁気的な影響が効果的に抑制されるようになる。

(もっと読む)

アルミニウム体を備えた基体の製造方法

【課題】基体上に成膜特性(反射率、及び密着性)に優れた膜状のアルミニウム体を形成することができるアルミニウム体を備えた基体の製造方法を提供する。

【解決手段】基体をプラズマ処理するプラズマ処理工程と、プラズマ処理された基体上に、アミン化合物と水素化アルミニウムとの錯体及び有機溶媒を含有するアルミニウム体形成用組成物を塗布して、上記基体上に上記組成物からなる塗布層を形成させる塗布工程と、上記塗布層に加熱および光照射の少なくともいずれか一方を行うことにより、膜状のアルミニウム体を形成させるアルミニウム膜形成工程と、を含むアルミニウム体を備えた基体の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】高精細化に伴う、貫通孔の微細化とさらに高アスペクト化の貫通電極を有する半導体装置の製造方法を提案する。

【解決手段】半導体基板1の厚み方向に貫通する貫通電極4を有する半導体装置の製造方法であって、半導体基板1の第1の面1aから第1孔10を開口する第1の工程と、第1孔10を含む半導体基板1の第1の面1aに絶縁膜2を形成する第2の工程と、半導体基板1の第1の面1aと反対の面である第2の面1bから、少なくとも2つの第1孔10を含んで第1孔10へ貫通する第2孔11を開口する第3の工程と、第2孔11側よりスパッタ法によりシード層3を成膜する第4の工程と、シード層3に金属材料4aをメッキ法により半導体基板1の第1の面1aに達するまで第1孔10を埋める第5の工程と、半導体基板1の第2の面1bを第2孔11の深さ寸法より深く、厚み方向に研削する第6の工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】大電流を流す第1ビアおよび第1配線を有し、且つ、当該第1ビアおよび第1配線が形成された第1面が平坦な半導体装置を提供する。

【解決手段】第1基板100と、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420と、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続する第1配線440と、を備えている。また、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

(もっと読む)

半導体装置とその製造方法

【課題】クラック伝播を抑制できる新規な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に形成された半導体素子と、半導体素子を囲む第1金属リングと、半導体素子を覆って形成され、内部に前記第1金属リングが配置された絶縁膜と、絶縁膜に形成された溝とを有し、第1金属リングは、複数の金属層が積層されて形成され、各々の金属層の外側の側面が一致しているか、または、下側に位置する金属層の外側の側面よりも上側に位置する金属層の外側の側面が内側に位置しており、溝の底面は、第1金属リングより内側に配置された第1部分で、第1金属リングの最上層に位置する金属層の上面以下である。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

81 - 100 / 2,805

[ Back to top ]