Fターム[5F033QQ41]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | リフトオフ (276)

Fターム[5F033QQ41]の下位に属するFターム

リフトオフ材 (96)

Fターム[5F033QQ41]に分類される特許

1 - 20 / 180

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

電子装置およびその製造方法

【課題】信頼性の高いコンタクト構造を提供する。

【解決手段】電子装置は第1の絶縁膜と、前記第1の絶縁膜の表面に形成された配線溝と、Cuよりなり前記配線溝を充填する配線パタ―ンと、前記配線パタ―ンの表面に形成され、Cuよりも大きな弾性率を有する金属膜と、前記第1の絶縁膜上に形成された第2の絶縁膜と、Cuよりなり、前記第2の絶縁膜中に形成され、前記金属膜とコンタクトするビアプラグと、を備える。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】 より一層、製品の歩留まりを向上させることのできる半導体装置の製造方法を提供する。

【解決手段】 本開示の半導体装置の製造方法では、まず、第1半導体部及び第2半導体部を貼り合わせた半導体部材の一方の面上に形成された絶縁膜30上に、所定の薬液で処理された際に該所定の薬液が絶縁膜に浸透しないような耐性を有するストッパー膜31を形成する。次いで、半導体部材のストッパー膜31側に、第1半導体部及び第2半導体部を電気的に接続するためのCu配線接合部34を形成する。次いで、Cu配線接合部34上にCu拡散防止膜34を形成する。次いで、Cu配線接合部34の形成領域以外の領域のCu拡散防止膜33を除去して該領域に存在する不要なCu部210,211を露出させる。そして、所定の薬液を用いて、不要なCu部210,211を除去する。

(もっと読む)

半導体装置の製造方法

【課題】アライメント光によるアライメントマークの検出感度を向上させて、低コストで貫通孔の位置合わせを行う。アライメントマークの誤検出を防ぐ。また、アライメントマーク検出時のアライメント光の露光マージンを大きくして、微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板の非有効ショット領域において、半導体基板の主面又は主面よりも上方にアライメントマークを形成する。半導体基板の裏面の方から、アライメントマークが形成された位置に対応する開口を形成する。半導体基板内に形成されている半導体装置の構成パターンと露光用マスクパターンとの位置合わせをして、有効ショット領域の半導体基板内に貫通孔を形成する。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

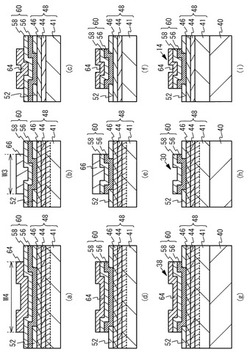

半導体装置の製造方法

【課題】レジスト形状の制限が無く、またステップカバレッジの悪い成膜方法を用いなくても良いリフトオフ工程が行えるようにする。

【解決手段】レジスト2の上に被パターニング膜3を成膜したのち、イオン照射によって被パターニング膜3のコーナ部を選択的にエッチングすることでレジスト2を露出させるようする。そして、レジスト2を除去することで、レジスト2の上の被パターニング膜3をリフトオフさせ、被パターニング膜3をパターニングする。このようにしてリフトオフ工程を行えば、レジスト2の側面において被パターニング膜3が厚く形成されていたとしても、イオン照射によってレジスト2を露出させることができる。このため、レジスト2の側面での被パターニング膜3の厚みの制限を受けないため、あえてステップカバレッジの悪い成膜方法を用いなくても良くなり、ステップカバレッジの良い成膜方法を選択することもできる。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】本発明は、絶縁膜を金属に密着させることができる半導体装置の製造方法と半導体装置を提供することを目的とする。

【解決手段】本願の発明に係る半導体装置の製造方法は、基板上に多結晶の金属を形成する工程と、該金属の表面粗さRaが0.051μmより大きくなり、かつ該金属の表面に1〜10μm径のランダムな方向に伸びる複数の穴が形成されるように、該金属の表面を1.0μm/min未満のエッチングレートでウェットエッチする工程と、該金属の表面に絶縁膜を形成する工程と、を備えたことを特徴とする。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】良好な側壁形状の開口を有する半導体装置の製造方法および半導体装置を提供する。

【解決手段】GaAs基板101上に形成された誘電体膜102の一部を誘電体膜102の表面から所定の深さまでエッチングする第1のエッチング工程と、第1のエッチング工程により誘電体膜102がエッチングされた第1のエッチング領域11において誘電体膜102をエッチングしてGaAs基板101の表面を露出し、かつ、第1のエッチング領域11を包含する第2のエッチング領域12において第1のエッチング領域11以外の領域に配置された誘電体膜102を所定の膜厚までエッチングする第2のエッチング工程とを含む。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の薄い抵抗体もつ抵抗素子を形成する際に、抵抗体の断線に対して強い抵抗素子を提供する。

【解決手段】バリアメタル膜とアルミ電極膜からなる積層電極の先端領域を単層のバリアメタル電極とし、並列するバリアメタル電極間に電気的に接続する抵抗体をリフトオフ法にて形成する。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】有機電界効果トランジスタにおけるビア形成を、低コストで効率的なプロセスで実現する。

【解決手段】誘電層106内にビア113を形成する際、まず各ビア位置にパターン化された導電材よりなるポストを印刷し、次にパターン化されていない誘電層106を堆積させ、次に第2のパターン化された導電層を堆積させる。ビア113は、誘電層106を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールすることにより形成される。

(もっと読む)

メッキ金属膜基板とその製造方法、及び半導体装置

【課題】一度の成膜で、所望の平面パターンと膜厚分布を有するメッキ金属膜を成膜することが可能なメッキ金属膜基板とその製造方法を提供する。

【解決手段】メッキ金属膜基板1は、基板上に少なくとも1層の給電金属膜20と少なくとも1層のメッキ金属膜30とを順次有し、少なくとも1層の給電金属膜20は、少なくとも1層のメッキ金属膜30の下地が相対的に高抵抗な高抵抗部20Hと、メッキ金属膜30の下地が相対的に低抵抗な低抵抗部20Lとを有するものである。

(もっと読む)

1 - 20 / 180

[ Back to top ]