Fターム[5F033WW10]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | パラメータを工程途中で変化させるもの (113)

Fターム[5F033WW10]に分類される特許

1 - 20 / 113

シリコン膜の形成方法及び半導体装置の製造方法

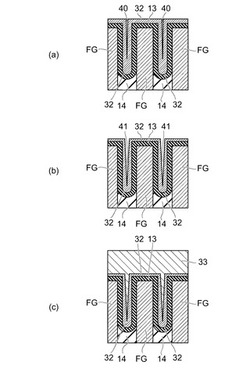

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Cu配線内における空孔の集中を抑制することでCu配線内でのボイドの形成を抑え、例えば2層間配線系におけるビア接続部等における、いわゆるストレスマイグレーションと呼ばれる断線等の配線不良の発生が抑制される半導体装置の製造方法を提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法において、配線形成後に被処理基板を加熱および除熱する熱サイクル工程を行う、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】配線幅が異なる第1及び第2の配線を有する配線パターンの上に形成された絶縁層を、十分に平坦化すること。

【解決手段】基板上に、第1の配線及び第1の配線よりも配線幅が小さい第2の配線を有する配線パターンを形成する配線形成工程S10と、配線パターンの上から、第1の絶縁層及び第2の絶縁層をこの順に形成する絶縁層形成工程S20と、第2の絶縁層の上に、配線パターンの反転パターンを有するレジストパターンを形成するレジスト形成工程S30と、第2の絶縁層の方が第1の絶縁層よりもエッチングされやすい条件で等方性エッチングするエッチング工程S40と、レジストパターンを除去するレジスト除去工程S50と、を有する半導体装置の製造方法。

(もっと読む)

3Dフラッシュ構造用のエッチングプロセス

【課題】プラズマ処理室において、ウェハ上でスタックを形成するシリコン系の複数の二重層の中に高アスペクト比のフィーチャをエッチングするための方法を提供する。

【解決手段】プラズマ処理室に主エッチングガスが流入される。第1の圧力を提供しながら、主エッチングガスがプラズマにされる。20℃未満のウェハ温度が維持される。プラズマにより上記複数のシリコン系二重層のうちの複数の組を貫いてエッチングする間に、第1の圧力よりも低い第2の圧力まで圧力を降下させる。上記複数の二重層のうち第1の複数の組がエッチングされた後に、主エッチングガスの流入を停止させる。

(もっと読む)

厚膜レジストの現像方法、及び半導体デバイスの製造方法

【課題】生産性を低下させることなく、基板の外周部にレジスト残渣が発生することを抑制可能な厚膜レジストの現像方法、及び半導体デバイスの製造方法を提供する。

【解決手段】回路素子層の上面に、厚膜レジストを形成する工程と、厚膜レジストを露光する工程と、露光後に、30〜50rpmの範囲内の一定の回転速度で炭化珪素基板を回転させながら、厚膜レジストの上方から現像液を供給することで、厚膜レジストの上面に現像液よりなるパドルを形成し、該パドルにより厚膜レジストを現像して、厚膜レジストに回路素子層の上面を露出する開口部を形成する工程と、を有する。

(もっと読む)

プラズマエッチング方法

【課題】マスクをプラズマから保護することができ、形成する穴部の側壁を基板の表面に対して垂直にできるプラズマエッチング方法を提供する。

【解決手段】上方にパターニングされたシリコン酸化膜が形成されてなる被処理基板におけるシリコン層を第1の処理ガスによりエッチングして穴部を形成するプラズマエッチング方法において、一酸化炭素ガスを含む第2の処理ガスによりシリコン酸化膜の表面に保護膜を堆積させる第1の堆積ステップS11と、第1の処理ガスによりシリコン層をエッチングする第1のエッチングステップS12と、穴部の側壁に第2の処理ガスにより保護膜を堆積させる第2の堆積ステップS13と、第1の処理ガスによりシリコン層を更にエッチングする第2のエッチングステップS14とを有し、第2の堆積ステップS13と第2のエッチングステップS14とを少なくとも2回ずつ交互に繰り返す。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2膜33およびSiC膜35からなる積層膜36を形成し、この積層膜36をパターニングすることによりハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、当該エッチングによりSiC膜35から解離したCを含む反応生成物を含む側壁保護膜32を、エッチング途中のAlCu膜30の側面に形成しながらAlCu配線層34をパターニングすることによって、第1AlCu配線20を形成する。

(もっと読む)

半導体装置の製造方法

【課題】CMP法により、金属膜を研磨して、層間絶縁膜に設けられた開口部内に導体パターンを形成する際、リセス、ディッシング、及びエロージョンを抑制可能な半導体装置の製造方法を提供する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜を確実に除去して半導体装置の欠陥発生を低減する。

【解決手段】第1の層間絶縁膜の上に、絶縁膜と、反射防止膜と、レジスト膜とを順番に形成する。レジスト膜を用いて反射防止膜と絶縁膜をエッチングし、絶縁膜からハードマスクを作成する。この後、ラジカル照射によってレジスト膜と反射防止膜を除去する。ラジカル照射は、基板温度を100℃、150℃、250℃と順番に上昇させながら行う。基板温度が低い初期段階では、反射防止膜の膜材料の飛散防止と、反射防止膜の表面に残留する他の物質の除去が行われる。この後、基板温度を高くすることで、反射防止膜が確実に除去される。

(もっと読む)

半導体装置、およびコンタクトプラグの形成方法

【課題】半導体装置内の回路に用いる構造として、半導体回路の電極体と導通電極とのコンタクト抵抗を良好に維持する。

【解決手段】半導体装置内の回路に用いる構造として、半導体回路の電極体とするシリサイドと、そのシリサイドと電気的に接続され、ストッパ層を取り除いて該シリサイドの側面を露出させた空間に形成された導通電極とするコンタクトプラグとを設ける。

(もっと読む)

偏在率算出方法、半導体装置の製造方法及びプログラム

【課題】レイアウトデータからCu残が発生しやすい品種やレイヤであるか否かを判定することのできる偏在率算出方法を提供する。

【解決手段】CPUは、検証レイヤにおいて所定サイズの検証エリア毎にパターン密度を算出するステップS13と、算出されたパターン密度を複数の密度範囲に分別し、各々の密度範囲に属するパターン密度の分布を示す複数の密度マップMAP0〜MAP7を生成するステップS14とを実行する。また、CPUは、各密度マップMAP0〜MAP7に所定量のプラスシフトを加えるステップS15と、パターン密度の密度差が第1基準値以上となる組み合わせの密度マップMAP0〜MAP7を重ね合わせ、両密度マップで重複した領域を抽出するステップS16とを実行する。CPUは、その抽出した領域の総面積を算出するステップS17と、算出した総面積と第2基準値とを比較するステップS18とを実行する。

(もっと読む)

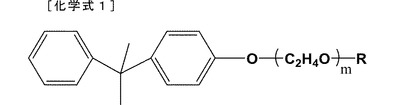

銅めっき溶液およびこれを用いた銅めっき方法

【課題】高縦横比のビアホールを埋め込むのに好適な銅めっき溶液および銅めっき方法を提供する。

【解決手段】シード層を有する基板を浸漬し、水、銅供給源、電解物質、塩素イオン、第1添加剤、第2添加剤、および第3添加剤を含み、前記第1添加剤は、化学式1に示す化合物である銅めっき溶液を用いて銅めっきを行う。

(式中、Rは、水素原子または炭素原子数1〜6のアルキル基であり、mは、平均重合度であり6〜14の実数である。)

(もっと読む)

半導体装置の製造方法、及び固体撮像装置の製造方法

【課題】 精度よく開口を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 第1の絶縁膜となる部材と、第1の絶縁膜となる部材と異なる材料からなる第2の絶縁膜となる部材と、第3の絶縁膜となる部材と、第3の絶縁膜となる部材と異なる材料の第4の絶縁膜となる部材とがこの順に積層された半導体基板の上に、複数の絶縁膜の開口を形成するための開口を有するマスクを形成する工程と、第3の絶縁膜となる部材のマスクの開口に対応する部分と第4の絶縁膜となる部材のマスクの開口に対応する部分を連続して除去する第1の工程と、第1の工程を行った後に、第2の絶縁膜となる部材のマスクの開口と対応する部分を除去する第2の工程と、を有する。

(もっと読む)

成膜方法

【課題】窒化シリコン膜と酸化シリコン膜との積層構造体を単一のプラズマCVD装置にて一貫して成膜する際に、両膜間に異質な薄膜が形成されないという機能を有しつつ、短時間で効率のよい成膜が可能な成膜方法を提供する。

【解決手段】本発明の成膜方法は、反応室2aに処理すべき基板Wを設置し、真空雰囲気中にてシリコンを含む原料ガスと窒素を含む一の反応ガスとを反応室内に導入し、放電用の高周波電力を投入してプラズマCVD法にて窒化シリコン膜を成膜する第1工程と、前記原料ガスを供給しながらプラズマ放電を維持した状態で、反応室内の窒素分圧を高める第2工程と、一の反応ガスの供給のみを停止し、酸素を含む他の反応ガスを反応室内に供給してプラズマCVD法にて酸化シリコン膜を成膜する第3工程とを含む。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

電子部品の製造方法

【課題】高温で成膜される低融点金属の凝集を防止し、十分なバリア性及びぬれ性を有するバリア層を形成して、凹部に低融点金属を付け回り良く充填する。

【解決手段】電子部品の製造方法が、4Pa以上20Pa以下の圧力下で、被処理体306と接する電極301に第1のバイアス電力を印加し、プラズマ処理により被処理体306の上にTiNxからなる第1のバリア層404を成膜する手順と、4Pa以上20Pa以下の圧力下で、電極301に第1のバイアス電力よりも小さいイオン入射エネルギーを与える第2のバイアス電力を印加し、またはバイアス電力を印加しないで、プラズマ処理により第1のバリア層の上にTiNxからなる第2のバリア層405を成膜する手順と、第2のバリア層405の上に、Tiからなる第3のバリア層409を成膜する手順と、第3のバリア層409の上に低融点金属406を充填する手順と、を有する。

(もっと読む)

半導体素子の製造方法

【課題】タングステン層の膜残りの発生を抑制する。

【解決手段】半導体基板1、コンタクトホール3を備えた絶縁膜2、絶縁膜2の表面およびコンタクトホール3の表面を被覆する被覆層4、並びに、コンタクトホール3を埋込むタングステン(W)層5を有するウエハに対し、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で高速でドライエッチングする工程と、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で、低速でドライエッチングする工程と、ウエハを冷却しつつ、被覆層4が露出するまで、W層5を低速でドライエッチングする工程と、ウエハを冷却しつつ、コンタクトホール3内のW層5を絶縁層2の高さまで低速でドライエッチングする工程と、を有する半導体素子の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の接続孔側壁の寸法制御を高精度に且つ低コストで行うことができる半導体装置を提供する。

【解決手段】半導体装置1は、基材10の主面を被覆し、下部電極11の上面に達する接続孔12hを有する絶縁膜12を備える。絶縁膜12の膜密度は、基材10の主面から絶縁膜12の厚み方向に離れるに従って低減する。接続孔12hの内径は、絶縁膜12の膜密度の低減に伴って拡大する。

(もっと読む)

1 - 20 / 113

[ Back to top ]