Fターム[5F033XX05]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | エレクトロマイグレーション防止 (477)

Fターム[5F033XX05]に分類される特許

21 - 40 / 477

半導体装置

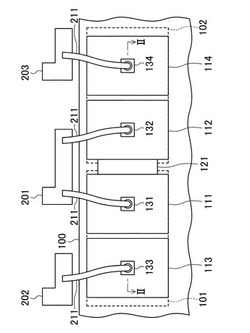

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

金属薄膜の成膜方法、半導体装置及びその製造方法

【課題】単膜でCu拡散のバリア膜及びめっきシード層として機能するとともに、Cuとの密着性にも優れた金属薄膜の成膜方法を提供する。

【解決手段】金属薄膜の成膜方法は、Ti膜を成膜する工程(STEP1)、Ti膜上にCo膜を形成する工程(STEP2)、Ti膜及びCo膜を熱処理してCo3Ti合金を含む金属薄膜を形成する工程(STEP3)を備えている。Co3Ti合金を含む金属薄膜は、優れた導電性とCu拡散バリア性を有し、Cuとの格子不整合が0.15%と非常に小さいため、Cu配線と優れた密着性が得られる。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】電位ドロップに起因するセルの動作不良を防止すること。

【解決手段】本発明に係る半導体集積回路は、チップ1上に配置された電源パッド2aと、電源配線構造10を介して電源パッド2aに接続された回路群21,22とを備える。その電源配線構造10は、異なる配線層に形成され複数の交差点IS1,IS2においてオーバーラップする複数の第1電源配線11及び複数の第2電源配線12と、それら複数の第1電源配線11と複数の第2電源配線12を接続するビア13とを有する。上記回路群は、第1領域R1に配置された機能ブロック21を含む。ビア13は、第1領域R1と電源パッド2aの間の第2領域R2における複数の交差点IS2の一部に配置されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】アルミ膜を用いて生産コストの低減を図りながら、歩留りおよび信頼性を両立できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上に形成された酸化膜3上に指向性スパッタによってチタン膜41が形成される。このチタン膜41上に通常のスパッタによって窒化チタン膜42が形成される。さらに、窒化チタン膜42上に、通常のスパッタによってアルミ膜43が形成される。チタン膜41は、(002)配向し、アルミ膜43は(111)配向する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】配線中に残留した不純物金属の濃度が少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板上に絶縁膜を形成し、絶縁膜に凹部を形成し、凹部の形成された絶縁膜の表面に所定の金属元素を含む前駆体膜を形成し、前駆体膜上に配線形成膜を堆積させ、酸化雰囲気下で熱処理を施すことにより、前駆体膜と絶縁膜を反応させ、その境界面に所定の金属元素と絶縁膜の構成元素を含む化合物を主成分とする自己形成バリア膜を形成し、未反応の所定の金属元素を配線形成膜内に拡散移動させて配線形成膜表面で雰囲気中の酸素と反応させ、未反応金属酸化膜として析出させ、未反応金属酸化膜を除去し、未反応金属酸化膜を除去する工程の後、配線形成膜上に、配線形成膜と同一の材料を堆積させて、配線形成膜を積み増した後、凹部外の絶縁膜が露出するまで配線形成膜を平坦化して配線構造を形成する。

(もっと読む)

半導体用銅合金配線及びスパッタリングターゲット並びに半導体用銅合金配線の形成方法

【課題】半導体用銅合金配線自体に自己拡散抑制機能を有せしめ、活性なCuの拡散による配線周囲の汚染を効果的に防止することができ、またエレクトロマイグレーション(EM)耐性、耐食性等を向上させ、バリア層が任意に形成可能かつ容易であり、さらに半導体用銅合金配線の成膜工程の簡素化が可能である半導体用銅合金配線及び同配線を形成するためのスパッタリングターゲット並びに半導体用銅合金配線の形成方法を提供する。

【解決手段】Mn0.05〜5wt%を含有し、Sb,Zr,Ti,Cr,Ag,Au,Cd,In,Asから選択した1又は2以上の元素の総量が10wtppm以下、残部Cuである自己拡散抑制機能を備えた半導体用銅合金配線。

(もっと読む)

Cu−Mn合金スパッタリングターゲット及び半導体配線

【課題】半導体用銅合金配線自体に自己拡散抑制機能を有せしめ、活性なCuの拡散による配線周囲の汚染を効果的に防止することができ、またエレクトロマイグレーション(EM)耐性、耐食性等を向上させ、バリア層が任意に形成可能かつ容易であり、さらに半導体用銅合金配線の成膜工程の簡素化が可能である半導体用銅合金配線及び同配線を形成するためのスパッタリングターゲット並びに半導体用銅合金配線の形成方法を提供する。

【解決手段】Mn0.05〜20wt%を含有し、Be,B,Mg,Al,Si,Ca,Ba,La,Ceの総計が500wtppm以下、残部がCu及び不可避的不純物であることを特徴とするCu−Mn合金スパッタリングターゲット。

(もっと読む)

半導体装置

【課題】 半導体素子の電極がはんだバンプを介して接続パッドに電気的に接続されているとともに、エレクトロマイグレーションが効果的に抑制された半導体装置を提供する。

【解決手段】 半導体基板1の電極3の外周の一部に電子回路2が直接に接続されてなる半導体素子と、半導体素子の電極3と対向して配置された接続パッド5を備える配線基板4と、電極3と接続パッド5との間に介在して、電極3および接続パッド5に接合されたはんだバンプ6とを備え、電極3とはんだバンプ6との界面に沿って、電極3の外周の電子回路2が接続されている一部に接した部分において他の部分よりも厚いニッケル層7が介在している半導体装置である。ニッケル層7の厚みの差に応じた電気抵抗差によって、半田バンプ6に流れる電流の電流密度を均一化し、電流の集中によるマイグレーションを抑制できる。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

装置

【課題】ボイドが存在しても高い信頼性を確保可能な配線構造を提案する。

【解決手段】実施形態に係わる装置は、第1の溝10を有する絶縁層13と、第1の溝10内に形成され、上部に凹部16を有する銅を含む第1の配線層15と、第1の配線層15の凹部16の内面上に形成され、少なくとも1つのグラフェンシートから構成されるグラフェン層17とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体装置の製造方法、配線用銅合金、及び半導体装置

【課題】半導体装置の歩留まりと信頼性を向上させる。

【解決手段】配線凹部に埋め込まれた部分以外のバリアメタル膜3b上のCu膜5bを化学機械研磨によって除去する。そして配線凹部内のCu膜5b上に、添加元素からなる層6bを形成する。添加元素を層6bからCu膜5b中に拡散させて、Cu表面、及びCu結晶粒の粒界及び該粒界近傍の位置においてCu結晶粒内部よりも添加元素の濃度が高い界面及びその近傍を形成するとともに、Cu膜5b中の酸素を層6bにゲッタリングさせる。その後、余剰な層6bを除去し、さらに絶縁膜上のバリアメタル膜3bを除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグを、配線のバリア層に安定して接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、バリア層を介して配線に接続されたコンタクトプラグ、第1及び第2の絶縁膜を有する。第1の絶縁膜は、配線及びバリア層の側面を覆い少なくともバリア層よりも上方で配線が延在する方向と直交する方向の幅が狭まる傾斜面を有し、バリア層の上面の一部を露出すると共に配線及びバリア層の側面を露出させないように形成された開口部を備える。第2の絶縁膜は、開口部の内側を除き第1の絶縁膜上に形成され、かつ開口部を備える。

(もっと読む)

半導体装置の製造方法

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】ポーラスLow−k膜からなる第2ファイン層の層間絶縁膜IL2内の空孔10および空孔11の平均径を1.0nm以上1.45nm未満とすることで、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置およびその製造方法

【課題】Cuを主成分とする材料からなる最上層配線からのパッシベーション膜の剥離を防止することができる、半導体装置を提供する。

【解決手段】半導体装置1は、層間絶縁膜26と、絶縁材料からなり、層間絶縁膜26上に形成されたパッシベーション膜33と、銅を主成分とする材料からなり、層間絶縁膜26の表面とパッシベーション膜33との間に形成された最上層配線28と、アルミニウムを主成分とする材料からなり、パッシベーション膜33と最上層配線28の表面との間に介在され、最上層配線28の表面を被覆する配線被覆膜31とを含む。

(もっと読む)

薄膜の形成方法

【課題】埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させることが可能な薄膜の形成方法を提供する。

【解決手段】表面に凹部8を有する被処理体Wの表面に薄膜を形成する形成方法において、被処理体の表面に埋め込み用の金属膜16して凹部を埋め込む埋め込み工程と、金属膜を覆うようにして被処理体の表面の全面に拡散防止用の金属膜18を形成する拡散防止膜形成工程と、被処理体をアニールするアニール工程とを有する。これにより、埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させる。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーションの影響を低減できるCu配線を備えた半導体装置

及びその製造方法を目的とする。

【解決手段】

Cu配線10を備える半導体装置1において、

Cu配線10の断面構造は、側部及び下部をバリアメタル20に接し、上部を絶縁膜3

0に接し、絶縁膜30に接するCu配線10の上部のグレインサイズが、Cu配線10の

中央部のグレインサイズより小さ。さらに、バリアメタルに接するCu配線10の側部及

び下部のグレインサイズが、Cu配線10の中央部のグレインサイズより小さい。

(もっと読む)

21 - 40 / 477

[ Back to top ]