Fターム[5F033XX05]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | エレクトロマイグレーション防止 (477)

Fターム[5F033XX05]に分類される特許

61 - 80 / 477

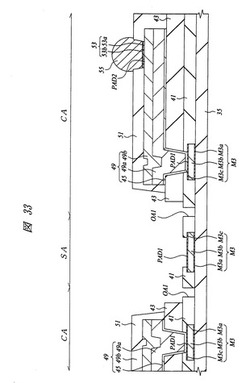

半導体集積回路装置の製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】プログラム後の誤読み出しを抑制でき、高い信頼性を備える半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1上のチャンネル領域に形成されたゲート酸化膜3と、前記ゲート酸化膜3上に形成されたゲート電極4と、前記チャンネル領域の少なくとも一部に形成されたシリサイド層2と、を有し、前記シリサイド層2は、前記チャンネル領域のうち前記ゲート電極4の全体を除く領域の少なくとも一部を被覆する。

(もっと読む)

薄膜抵抗素子、および、その製造方法

【課題】安定して配線と抵抗体薄膜との接触が可能な接続構造をもつ薄膜抵抗素子を実現する。

【解決手段】互いに離間する2つの電極配線(3A,3B)に、抵抗体薄膜5を接続させている。2つの電極配線の各々が、主配線部3mと、当該主配線部3mのコア配線部3cより酸化されにくい導電材料で側面に形成されている側壁導電膜3sとを有する。抵抗体薄膜5は、2つの電極配線の各々に対して、側壁導電膜3sを介して電気的に接続している。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

電子デバイス

【課題】製造工程数や面積の増大を招くことなく、金属薄膜抵抗の抵抗率を異ならせる素子構造を提案する。

【解決手段】基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜5が配置されている。また、抵抗膜5の厚さ方向の少なくとも一方の他の導電膜配置階層に、水素吸蔵金属3が、抵抗膜5と絶縁された状態で、かつ金属抵抗膜の少なくともコンタクトエッジ間の領域の全域と平面視で重なる位置と大きさで配置されている。

(もっと読む)

半導体装置

半導体装置が半導体基板上のゲートを含む。ゲートの1つの側壁が少なくとも1つの突出部を含んでいてもよく、ゲートの反対側壁が少なくとも1つの凹部を含んでいてもよい。接触部が、ゲート上に配置された絶縁層を通して形成されている。接触部は、ゲートの少なくとも1つの突出部に少なくとも部分的に重なっている。金属層が絶縁層上に配置されている。金属層は、ゲートの第1の側に移動した第1の構造を含む。接触部が絶縁層を通して第1の構造をゲートに電気的に連結するように、第1の構造は接触部に少なくとも部分的に重なっている。 (もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体ウエハ上に形成された第1の保護膜上にポリイミド系樹脂等からなる第2の保護膜を形成するとき、半導体ウエハが反りにくいようにする。

【解決手段】 所定の相隣接する2本の配線7の接続パッド部7b間に形成された5本の引き回し線部7cおよびその両側における相隣接する2つの接続パッド部7bの周辺部を含む第1の保護膜5の上面に、スクリーン印刷法やインクジェット法等により、ポリイミド系樹脂等からなる第2の保護膜10を形成する。この場合、当該5本の引き回し線部7cの互いに平行とされた部分がエレクトロマイグレーションに起因するショートが発生しやすい領域であるので、この領域のみを第2の保護膜10で覆えば、当該領域でエレクトロマイグレーションに起因するショートが発生しにくいようにすることができる。この結果、第2の保護膜10の形成領域を可及的に小さくすることができ、これにより半導体ウエハ21が反りにくいようにすることができる。

(もっと読む)

Cu−Al合金粉末、それを用いた合金ペーストおよび電子部品

【課題】本発明は、配線や電極をペーストから焼成して製造する電子部品や、ガラス又はガラスセラミックス部材と接する配線を有する電子部品において、酸化による電気抵抗増大を抑制でき、あるいは、ガラス又はガラスセラミックスの気泡の発生を抑制可能で、マイグレーション耐性に優れたCu系配線材料を用いた電子部品を提供することを目的とする。

【解決手段】本発明は、ガラスまたはガラスセラミックス部材と接する配線・電極・コンタクト部材、あるいはガラスまたはガラスセラミックスと共にペーストを形成し焼成して成る配線・電極・コンタクト部材を有する電子部品であって、Cu及びAlを含む合金粉末粒子から構成され、かつ、Cu及びAlを含む合金粉末粒子の表面が80nm未満の酸化Al皮膜(Al2O3)で覆われていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線に断線が発生することを抑制し、かつエレクトロマイグレーションに対する耐性、及び熱ストレスに起因したボイドの発生に対する耐性を配線に持たせる。

【解決手段】第2導電パターン104は端が第1導電パターン100につながっており、第1導電パターン100より幅が細い。第1導電パターン100及び第2導電パターン104は、シード層110及びメッキ層120を有する。シード層110及びメッキ層120は、それぞれ銅により形成されている。メッキ層120は、底層に、表層より結晶粒が小さい小粒層122を有している。そして第2導電パターン104を形成するメッキ層120は、小粒層122を、第1導電パターン100を形成するメッキ層120より厚く有している。

(もっと読む)

半導体装置

【課題】グラフェンのバリスティック(弾道)伝導性を利用し、パターン形状によらず電気抵抗の上昇を抑えることができ、さらにエレクトロマイグレーションやストレスマイグレーション等のマイグレーションに対する耐性に優れた低抵抗配線を備えた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、配線層絶縁膜5中に形成されたシングルダマシン構造を有する配線10と、コンタクト層絶縁膜2中に形成され、上層の配線10と下層の導電部材1を電気的に接続するコンタクト3と、コンタクト層絶縁膜2と配線層絶縁膜5との間に形成されたエッチングストッパ膜4と、配線層絶縁膜5上に形成された拡散防止膜6と、を有する。配線10は、芯材14と、芯材14の底面および両側面に接するグラフェン層13と、グラフェン層13の底面および両側面に接する触媒層12と、触媒層12の底面および両側面に接する下地層11とを含む。

(もっと読む)

半導体装置

【課題】ビアホールのアスペクト比が高くなればなるほど、バリアメタルのカバレッジが悪くなる。つまり、ビアホールの直径に対して深さが深ければ深いほど、ビアホールのボトム部に形成されるバリアメタルが不十分になり易い。その結果、ビアホール底部のアルミ層やチタン膜において、高抵抗化が起きる。また、ビアホール底端においては、電界が集中し、EM(ElectroMigration)によって劣化し、品質や寿命の低下が起きる。

【解決手段】ビアホールの開口後、2度のエッチングによってボトム部およびトップ部の形状をラウンド化する。その結果、ビアホールの低抵抗化および品質や寿命の向上が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 絶縁膜に設けた凹部の側壁にシール絶縁膜を形成し、シール絶縁膜の内側に順にシール絶縁膜との密着性が優れている第1の導電性バリア層、Cu拡散阻止能力が高い第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設ける。

(もっと読む)

半導体デバイスのための電力グリッド構造体及びその製造方法

【課題】 半導体デバイスに電力を提供する電力グリッド構造体及びその製造方法を提供する。

【解決手段】 本発明の一実施形態は、誘電体層の内部に形成された第1の導電性材料のスタッドと、底部及び側壁を有する第2の導電性材料のビアであって、底部及び側壁は導電性ライナで覆われ、底部はスタッドの直接上に形成され、かつ、導電性ライナを通してビアと接触した状態にある、ビアと、ビアの側壁において導電性ライナを通してビアに接続する第3の導電性材料の1つ又は複数の導電性パスとを含むことができる半導体構造体を提供する。半導体構造体を製造する方法も提供される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線抵抗の増加を抑えつつ、配線のエレクトロマイグレーション寿命、およびストレスマイグレーション寿命を向上させる。

【解決手段】半導体装置100は、基板102上に形成された層間絶縁膜104に形成された凹部に、高融点金属を含むバリアメタル膜106と、配線金属膜114を構成する銅および銅とは異なる不純物金属を含むシード合金膜ならびに銅を主成分として含むめっき金属膜とを形成し、シード合金膜およびめっき金属膜を、200℃以上、10分以下で熱処理する第1の熱処理工程と、第1の熱処理工程の後、凹部外部に露出しためっき金属膜、シード合金膜、およびバリアメタル膜106を除去する工程と、シード合金膜およびめっき金属膜を熱処理する第2の熱処理工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】実用上十分なエレクトロマイグレーション耐性及び動作速度を有する半導体装置を得られるようにする。

【解決手段】半導体基板1の上に第1の絶縁膜2を形成し、第1の絶縁膜2に配線溝3を形成し、配線溝3の内部に金属膜5を埋め込んで第1の配線6を形成し、第1の絶縁膜2及び第1の配線6の上に保護膜7を形成し、第1の配線6と保護膜7との界面に反応層8を形成する。

(もっと読む)

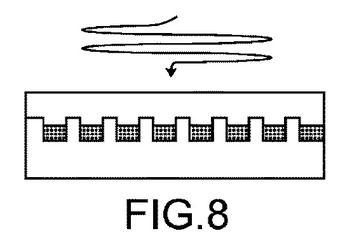

金属結晶領域、特に集積回路における金属結晶領域を生成する方法

本方法は、例えば相互接続ラインを形成するために、薄い結晶(8)のシートを、基板(1)のトレンチに堆積される、このシートと同一のタイプであるが、アモルファスであるか小さな粒径である金属(6)に固定することを含む。焼鈍しは、このラインにシートの結晶構造を徐々に与える。結晶(8)が除去されると、高度の導電結晶ラインが得られる。それは、その粒径が非常に拡大されているからである。金属は、銅、銀及びアルミニウムから選択される。  (もっと読む)

(もっと読む)

61 - 80 / 477

[ Back to top ]