Fターム[5F038AC14]の内容

Fターム[5F038AC14]の下位に属するFターム

Fターム[5F038AC14]に分類される特許

21 - 40 / 295

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体装置

【課題】キャパシタ構造の信号線およびGND電極を抵抗成分やインダクタンス成分を最小限にできる構造の配線基板を有する半導体装置を提供する。

【解決手段】信号線の一部を構成する中心導体2cの周囲に誘電体2bを介して同心円状にシールド線を構成する外側導体2aを備えるキャパシタ構造部2を有した構成とする。そして、2つのスルーホール3内に設けた各キャパシタ構造部2の中心導体2cについては、配線基板の表面側で各中心導体2cが上面配線5に電気的に接続され、裏面側でもう一方のキャパシタ構造部2の中心導体2cと第1下面配線6を介して電気的に接続され、さらに、各キャパシタ構造部2の外側導体2aについては、配線基板の裏面側に全面に一様に形成された第2下面配線7で覆われた状態で電気的に接続されるようにする。

(もっと読む)

半導体集積回路、半導体チップ、及び半導体集積回路の設計手法

【課題】容易な設計により、小規模な構成でクロックスキューを抑制させる半導体集積回路を提供する。

【解決手段】ラッチ回路31〜316のデータ入力端子とデータビットの供給元PDとの間に、クロック信号CLLの供給元PCD及びラッチ回路のクロック入力端子間のクロック信号経路中に含まれている論理素子の個数と同一数だけ当該論理素子を直列に接続してなる第1遅延部51,52と、クロック信号経路中の配線の配線長に対応した配線遅延時間と同一長の遅延時間を有する第2遅延部53と、を備える。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置では、コンデンサの容量値が配置場所で変化するため、容量値の見積もりが煩雑になるという問題を解決する。

【解決手段】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置の補償容量部のレイアウト配置の際に、補償容量部を構成する領域に拡散層の矩形領域を配置する。また、該拡散層の矩形領域の各辺に対し、各辺の中心が直行する箇所に矩形開口部を設ける。また、該拡散層の矩形領域の中心線近傍に沿ってゲート電極を直行するように形成する。また、該拡散層の該矩形領域の四隅に上層の金属層と接続するためのコンタクトを形成する。また、該ゲート電極と該拡散層の矩形開口部の重なる箇所にゲート電極と上層の金属層を接続するコンタクトを形成する。また、該ゲート電極が直行する箇所で容量を形成する。また、補償容量の単位セルを構成する。

(もっと読む)

容量素子及びその製造方法並びに半導体集積回路

【課題】高い周波数帯での導体損失の増加を抑え、幅広い周波数範囲で低損失な動作を実現することが可能な容量素子及びその製造方法並びに半導体集積回路を提供すること。

【解決手段】本発明の容量素子10は、第1電極11と、第1電極11上に設けられた誘電体層12と、誘電体層12上に設けられた第2電極13とから構成されている。容量素子10は、誘電体層12を第1電極11と第2電極13とにより挟むようにしたサンドイッチ構造になっており、第2電極13の外表面に凹凸が設けられている。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】シリンダ型下部電極の剥がれ落ちを防止する、半導体装置の製造方法を提供する。

【解決手段】複数の第1の開口を有するコア絶縁膜を半導体基板上に形成し、複数の第1の開口の側面を導電膜で覆う、シリンダ状の複数の下部電極を形成し、少なくとも複数の下部電極間のコア絶縁膜の上面を覆うサポート膜を形成し、サポート膜を用いて少なくとも複数の下部電極が形成される領域の外側を除去したマスク膜を形成し、マスク膜を形成した後、複数の下部電極間の一部にコア絶縁膜が残るように、コア絶縁膜に対して等方性エッチングを行うものである。

(もっと読む)

半導体装置の製造方法

【課題】積層したMIMキャパシタの静電容量の合計値を所望の静電容量に近づけることができる半導体装置の製造方法を得る。

【解決手段】半導体基板1上に、下地金属膜2、下層絶縁膜4、及び中間金属膜5を順に積層する。下層絶縁膜4の厚みを測定する。下層絶縁膜4の厚みを測定した後に、中間金属膜5上に上層絶縁膜7、及び上地金属膜8を順に積層する。下地金属膜2、下層絶縁膜4、及び中間金属膜5から第1のMIMキャパシタが構成される。中間金属膜5、上層絶縁膜7、及び上地金属膜8から第2のMIMキャパシタが構成される。第1のMIMキャパシタの静電容量と第2のMIMキャパシタの静電容量の合計値が所望の静電容量に近づくように、測定した下層絶縁膜4の厚みに基づいて、上層絶縁膜7及び上地金属膜8の少なくとも一方の設計条件を調整する。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

半導体装置

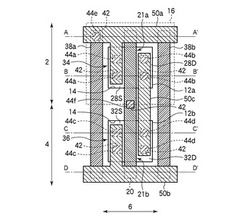

【課題】高出力の高周波信号の影響を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置は、電子回路が設けられた主面を有する半導体基板10と、前記主面の上に絶縁膜2,3,4を介して設けられたパッシブ回路30と、を備える。そして、前記半導体基板と前記パッシブ回路との間に前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙45を有した第1の導体層40と、前記第1の導体層と前記パッシブ回路との間に、前記第1の導体層および前記パッシブ回路から絶縁されて設けられ、前記主面に平行な少なくとも1方向に流れる電流を遮断する間隙55を有し、前記パッシブ回路から見た前記第1の導体層の間隙を覆う第2の導体層50と、を備える。

(もっと読む)

半導体装置

【課題】送信機の変調器のキャリアリークを従来よりも高精度に抑制する。

【解決手段】半導体装置10において、信号分配部37は、発振器26によって生成されて入力部IN1に入力された高周波信号を第1および第2の信号に分配し、第1および第2の出力部OA1,OB1からそれぞれ出力する。変調器30は、ベースバンド信号を第1の信号で変調して出力する。オフセット調整部90は、第2の信号と変調器30の出力から漏洩した第1の信号とを比較することによってベースバンド信号のオフセットを調整する。上記の信号分配部37は、入力部IN1と第1の出力部OA1との間に設けられた第1の容量素子Ccapと、第1の出力部OA1と第2の出力部OB1との間に設けられた第2の容量素子Cpとを含む。第1の容量素子Ccapの静電容量は、第2の容量素子Cpの静電容量よりも大きい。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

半導体装置の作製方法

【課題】必要十分なキャパシティをもつ保持容量を備えた半導体装置を提供する。

【解決手段】金属表面を有する基板11と、前記金属表面を有する基板上に形成された絶縁膜12と、前記絶縁膜上に形成された画素部とを有する半導体装置において、前記画素部は、TFTと、該TFTと接続する配線21とを有しており、保持容量は、前記金属表面を有する基板、前記絶縁膜および前記配線により構成されている。前記絶縁膜の膜厚が薄いほど、また、前記絶縁膜と前記配線の接する領域の面積が大きいほど、大きなキャパシティを得られるので有利である。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

半導体装置

【課題】無線通信によりデータの交信を行う半導体装置において、装置を大型化することなく、アンテナの感度を向上させ、チップをノイズから保護することを課題とする。

【解決手段】コイル状のアンテナと当該コイル状のアンテナに電気的に接続された半導体集積回路とを有する。コイル状のアンテナと重なるように半導体集積回路を配置する。このように、半導体装置内のコイル状のアンテナと半導体集積回路の配置を工夫することで、装置を大型化することなく、アンテナの感度を向上させて、半導体集積回路が動作するために十分な電力を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】容量素子の良好な特性と高い信頼性を実現することが可能な半導体装置を提供する。

【解決手段】半導体基板上に第1の絶縁膜を介して形成されている下部電極と、この下部電極の周囲に形成され、下部電極の表面よりも高い表面を有するダミー電極と、下部電極上にダミー電極の最上表面よりも表面が低い位置にある誘電体膜を介して形成された上部電極と、ダミー電極に周囲を囲まれた窪みを埋める第2の絶縁膜とを具備して成る半導体装置を構成する。

(もっと読む)

キャパシタ構造体およびその製造方法

【課題】シリコン基板に設けられた穴の内部に導電体と誘電体を配置することにより、キャパシタを構成してなるキャパシタ構造体において、穴をより深くしたり、穴の平面形状を複雑な形状とすることなく、導電体間の対向面積を増加させて容量値の増大が実現できるようにする。

【解決手段】穴20は、シリコン基板10の一方の主面に開口する有底穴であり、穴20の内部にはシリコン基板10よりなる突起21が設けられ、穴20の底面は、突起21による凹凸面とされており、穴20の内部では、穴20の底面および側面に、これらの面側から第1の導電体31、誘電体40、第2の導電体32が順次積層されているとともに、第1の導電体31および誘電体40は、突起21による凹凸面の形状を承継した層形状とされている。

(もっと読む)

半導体装置およびバイパスキャパシタモジュール

【課題】バイパスキャパシタは、半導体基板上に形成される半導体装置と一体化されて形成されているが、半導体装置の製造工程が複雑になると言う欠点がある。

【解決手段】バイパスキャパシタをシート状にモジュール化して、半導体装置に対して外付けできるように構成されたバイパスキャパシタモジュールが得られる。

(もっと読む)

半導体装置

【課題】補償容量素子を構成する容量絶縁膜が破壊されることのない半導体装置を提供する。

【解決手段】第1の電圧が供給される第1の電源端子29と、第2の電圧が供給される第2の電源端子23と、容量絶縁膜42と該容量絶縁膜42を挟んで形成される第1及び第2電極とを其々備えており、前記第1及び第2の電源端子間に直列に設けられる複数の補償容量素子4と、奇数番目の前記補償容量素子4と次の偶数番目の前記補償容量素子4とを各々接続する第1の配線層に形成された第1の容量接続配線と、偶数番目の前記補償容量素子4と次の奇数番目の前記補償容量素子4とを各々接続する第2の配線層に形成された第2の容量接続配線と、前記第1及び第2の容量接続配線のいずれか一方に隣接して設けられ、実質的に固定された電圧が供給されるシールド配線5と、を備える。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】キャパシタ装置及びその製造方法を提供する。

【解決手段】本発明に係るキャパシタ装置10は、第1導電型を有して第1電圧が印加される第1ウェル105及び第2導電型を有して第2電圧が印加される第2ウェル110を有する基板100、及び第1または第2ウェル105,110と絶縁されるように第1または第2ウェル105,110の上部に配されたゲート電極126を含み、キャパシタ装置10のキャパシタンスは、第1ウェル105と第2ウェル110との間の第1キャパシタンス及び第1または第2ウェル105,110とゲート電極126との間の第2キャパシタンスを含む。

(もっと読む)

半導体装置

【課題】MIMキャパシタの耐圧を高めることが可能な半導体装置を提供する。

【解決手段】半導体基板上に形成される下部電極層と、この下部電極層上に積層される誘電体層22と、この誘電体層上に積層される上部電極層23とで構成されるMIMキャパシタと、このMIMキャパシタの上部電極層に対して、接続角度が90度より大きくなるように線幅を広くして接続される第1の配線層パターン12と、前記MIMキャパシタの下部電極層に対して、接続角度が90度より大きくなるように線幅を広くして接続される第2の配線層パターン13a、13bと、を有する。

(もっと読む)

21 - 40 / 295

[ Back to top ]