Fターム[5F045AB03]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 4族 (3,529) | Si (2,361) | ポリSi (557)

Fターム[5F045AB03]に分類される特許

101 - 120 / 557

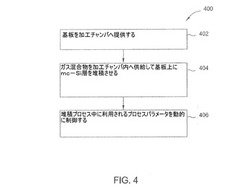

微結晶層内に形成される膜微細構造を動的に制御する方法

【課題】真性微結晶シリコン層のための方法を提供すること。

【解決手段】一実施形態では、真性微結晶シリコン層を形成する方法は、加工チャンバ内に配置された基板の表面へガス混合物中で供給されるシランガスを動的に増加させるステップと、加工チャンバへ供給されるガス混合物中で印加されるRF電力を動的に減少させて、ガス混合物中でプラズマを形成するステップと、基板上に真性微結晶シリコン層を形成するステップとを含む。

(もっと読む)

真空処理装置

【課題】簡素で安価な構成により、放電電極に繋がる高周波給電伝送路を流れる高周波電力の反射波発生を防止または抑制して信頼性および耐久性を向上させることのできる真空処理装置を提供する。

【解決手段】製膜装置(真空処理装置)は、製膜室(真空処理室)と、製膜室の内部に配設された放電電極6と、製膜室の外部に配設された高周波電源および整合器10aと、放電電極6の端部から直線状に延び、製膜室の壁体2bを貫通して整合器10aに直線的に繋がる高周波給電伝送路9aとを備えてなることを特徴とする。高周波給電伝送路9aは、放電電極6の端部から、放電電極6の熱膨張方向に沿って直線的に延設され、この高周波給電伝送路9aが製膜室の壁体2bを貫通する部分には、該壁体2bと高周波給電伝送路9aとの間の気密性を保ちつつ、高周波給電伝送路9aの伝送軸方向への動きを許容する貫通保持構造53を設けた。

(もっと読む)

半導体膜の改良された堆積方法

【課題】均一性の高いSi又はSiGeを基板表面上に堆積する方法を提供する。

【解決手段】化学気相成長プロセスにおいて、輸送量制限領域又はその近傍で、薄膜の堆積を行うことを可能にする化学前駆体を利用する。このプロセスによれば、堆積速度が大きく、さらに組成的にも厚み的にも、通常の化学前駆体を用いて調整した膜より均一な膜を生成することができる。好ましい実施の形態では、トリシランを使用して、トランジスタゲート電極などの様々な用途で半導体産業において有用なSi含有薄膜を堆積する。

(もっと読む)

半導体装置の製造方法および表示パネルの製造方法

【課題】微結晶半導体膜を含むチャネル層の移動度を向上させる半導体装置の製造方法を提供する。

【解決手段】微結晶シリコン膜を堆積する工程と、水素プラズマ処理を施す工程を交互に複数回ずつ繰り返す。このような方法で微結晶シリコン膜を成膜すれば、微粒子内のマイクロクリスタル成分に含まれるシリコン原子の未結合手を終端したり、アモルファス成分を改質したりすることを、より効率的に行なうことができるので、TFTの移動度をより高めることができる。

(もっと読む)

プラズマ処理装置およびそれよって製造される太陽電池の製造方法

【課題】形成される膜の膜質および膜厚が均一となるプラズマ処理装置を提供する。

【解決手段】本発明のプラズマ処理装置1は、処理室2内に配設された第1の電極3と、第1の電極3に対向し、基板10を保持できる第2の電極4と、処理室2内から排気を行なう排気手段と、処理室2内にガスを供給するガス供給手段と、を備え、第1の電極3は、第2の電極4に対向する側に凸部41を有し、凸部41の先端部にガス供給口42が形成されたものであって、複数の凸部41(41a〜41e)の先端部の幅が、第1の電極3の中央部に比べ、外周部の方が小さい。

(もっと読む)

半導体装置とその製造方法

【課題】 結晶シリコンとアモルファスシリコンとを含むシリコンを活性層に有する薄膜半導体装置は、活性層がゲート絶縁層から剥がれやすく、良好な特性が得られない。

【解決手段】 基板(101)に、ゲート電極(102)、窒化シリコンを含むゲート絶縁層(103)、結晶シリコンとアモルファスシリコンとを含むシリコン層(105)、コンタクト層(107)、ならびにソース電極及びドレイン電極(108)が、順に積層された半導体装置であって、前記シリコン層(105)の内部で、前記基板に近い側から前記ソース電極及びドレイン電極に近い側に向かって、前記結晶シリコンの体積比率が大きくなっており、かつ、前記ゲート絶縁層(103)と前記シリコン層(105)との間に酸化シリコンを含む層(104)が挟まれていることを特徴とする半導体装置。

(もっと読む)

半導体膜の作製方法

【課題】量産性に優れた薄膜トランジスタを提供する。また半導体装置の作製において有

用な半導体薄膜を提供する。

【解決手段】プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を形成し、前記半導体膜の一部を除去して、活性層を

形成し、トップゲート型薄膜トランジスタまたはボトムゲート型薄膜トランジスタを作製

する。また、プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を剥離層として用いた半導体装置を作製する。また、

プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1×1021/

cm3で含む半導体膜をゲッタリングサイトとして用いた半導体装置を作製する。

(もっと読む)

真空吸気配管のクリーニング方法

【課題】減圧下で処理を行う成膜装置又は結晶成長装置のクリーニング方法に係り、処理室から真空ポンプによりガスを吸気する吸気配管内のクリーニングを良好に行うようにしたクリーニング方法に関する技術である。

【解決手段】処理室1に接続された吸気配管6における真空ポンプ4との接続口6b近傍に開度調節可能な開閉弁9を設け、吸気配管6における処理室1との接続口6a近傍に設けられた装置仕切弁7を閉じ、前記開閉弁9の開度を調節し、吸気配管6に三フッ化塩素などからなる特定のクリーニングガスを供給するとともに、前記真空ポンプ4を稼動することにより、前記吸気配管6内を所定圧力に保持してクリーニングするようにして、成膜処理又は結晶成長処理時に吸気配管6内に付着した堆積膜を良好に除去し、装置の修理や分解をする際に、有害、危険な堆積膜による災害を防止するようにした。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製法を提供する。または、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】基板上に第1の微結晶半導体膜を形成した後、当該第1の微結晶半導体膜の表面を平坦化する処理を行い、次に、平坦化された第1の微結晶半導体膜の表面側の非晶質半導体領域を除去する処理を行って、結晶性が高く、且つ平坦性を有する第2の微結晶半導体膜を形成する。次に、第2の微結晶半導体膜上に第3の微結晶半導体膜を形成する。

(もっと読む)

シリコン及びシリコン含有膜の原子層堆積

成膜装置および成膜方法

【課題】成膜室内壁を保護するライナ上に副生成物が形成されるのを抑制する。

【解決手段】チャンバ1の頂部には、プロセスガス25の供給部4が、内部には、半導体基板6を載置する回転式のサセプタ7と、チャンバ1の内壁を被覆する筒状のライナ2とがそれぞれ設けられている。ライナ2は、サセプタ7の配置される胴部30と、供給部4の側にあって胴部30より断面積の小さい頭部31と、胴部30と頭部31をつなぐ段部32とを有する。ライナ2の頭部31の周囲には、塩化水素ガスをライナ2内に供給するガス流路26が設けられており、ライナ2内に塩化水素ガスを供給しながら、プロセスガス25を供給部4からチャンバ1内に流下させて、下方に配置されたサセプタ7上の半導体基板6に結晶膜を形成する。

(もっと読む)

エピタキシャルウエハの製造方法

【課題】 半導体ウエハの端面に角張った形状の結晶層を成長させることなく、半導体ウエハ上に厚い単結晶層を成長させることができる技術を提供する。

【解決手段】 半導体ウエハ10上に単結晶層30が形成されたエピタキシャルウエハの製造方法であって、平坦な上面12と、平坦な下面14と、上面12と下面14を接続する端面16を有する半導体ウエハ10の端面16上に、アモルファス層20を形成するアモルファス層形成工程と、アモルファス層形成工程後に、半導体ウエハ10の上面12上に、80μm以上の厚みを有する単結晶層30を気相成長させる単結晶層形成工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

多結晶シリコン堆積のためのシステム及び方法

薄膜形成装置

【課題】基板にシリコン薄膜を形成する際、従来のプラズマ処理装置に比べて純度の高いシリコン薄膜を形成することのできる薄膜形成装置を提供する。

【解決手段】薄膜形成装置は、減圧状態の成膜空間を形成する成膜容器と、前記成膜空間に原料ガスを供給する原料ガス供給部と、前記原料ガスが供給された前記成膜空間で、電磁波を用いてプラズマを生成させるプラズマ生成素子と、を有する。前記プラズマ生成素子は、前記成膜空間と隔壁で隔てられた空間に設けられ、前記隔壁の前記成膜空間に接する表面には、シリコンを主成分とする隔壁基材が設けられている。

(もっと読む)

真空処理装置、真空処理装置の給電装置、製膜方法、および製膜時における給電方法

【課題】製膜されるシリコン薄膜の面積を大きくしても、シリコン薄膜の膜厚分布のばらつきをおさえることができる真空処理装置、真空処理装置の給電装置、製膜方法、および製膜時における給電方法を提供する。

【解決手段】電源部17から高周波電力が給電点に供給され、対向電極に設置した基板との間にプラズマを形成する放電電極3aと、放電電極3aに供給される高周波電力の位相および振幅を、給電点のそれぞれにおいて調節する複数の整合器と、を備え、整合器には、放電電極3aに供給される高周波電力の位相を調節する位相調節コンデンサ23T及びコイル24と、高周波電力の振幅を調節する振幅調節コンデンサ25Mとからなる整合回路が複数設けられ、整合器のインピーダンスは、給電点間における高周波電力の位相差に基づいて、整合回路を切り替えることにより調節される。

(もっと読む)

シリコン生成方法

【課題】SiHCl3からSiを生成する際の反応効率を向上させる。

【解決手段】H2とAr等のキャリアガスをパルス熱プラズマ発生装置であるプラズマ発生部に導入して水素ラジカルを含むプラズマを発生させ、当該プラズマをSiHCl3と反応させる。H2をSiHCl3と反応させる従来技術で優先的に起こるSiCl4生成反応が抑止され、Siを効率よく生成することができる。

(もっと読む)

半導体膜の製造方法および半導体膜の製造装置

【課題】大面積の良質な半導体膜を安定して簡便に作製することが可能な半導体膜の製造方法を得ること。

【解決手段】前記カソード電極上に堆積した半導体膜を前記カソード電極を加熱することにより加熱する工程と、前記加熱された半導体膜中から離脱した脱離水素原子量を前記カソード電極の温度に応じて複数回測定する工程と、前記脱離水素原子量の測定結果を分析して前記半導体膜の膜質を反映させて製膜条件を調整するための指標となる膜質情報を取得する工程と、前記膜質情報に基づいて前記半導体膜の製膜条件を第2の製膜条件に再設定する工程とを含む。

(もっと読む)

半導体装置の製造方法及び基板処理方法及び基板処理装置

【課題】

汚染物やパーティクルがシリコン膜等を有する基板に混入することにより基板の品質や半導体装置の性能が劣化することを抑制し、表面粗さの小さいシリコン膜を形成する。

【解決する手段】

基板にシリコン膜を形成する膜形成工程と、前記シリコン膜に酸化種を供給し、前記シリコン膜を熱処理し前記シリコン膜の表層を酸化シリコン膜に改質する改質工程と、前記酸化シリコン膜を除去する除去工程と、を有する半導体装置の製造方法を提供することで上記課題を解決する。

(もっと読む)

成膜装置及びメンテナンス方法

【課題】シリコン膜を成膜する際に生じるポリシランを含む副生成物を、非成膜時に迅速かつ簡便に処理することが可能な成膜装置を提供すること。

【解決手段】本発明の成膜装置は、CVD法を用いて、真空中で基板Wにシリコン膜を成膜する成膜室11と、前記成膜室内にオゾン含有ガスを導入可能な第一オゾン含有ガス供給手段180と、を少なくとも備え、シリコン膜の成膜を終了した状態にある前記成膜室内に前記オゾン含有ガスを導入することにより、前記シリコン膜の成膜中に生成したポリシランを含む副生成物を酸化させること、を特徴とする。

(もっと読む)

101 - 120 / 557

[ Back to top ]