Fターム[5F048BB11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | ゲート絶縁膜材料 (1,843)

Fターム[5F048BB11]に分類される特許

41 - 60 / 1,843

半導体装置及びその製造方法

【課題】higher-k材料であるチタン酸化膜の半導体基板との界面を安定化でき、さらなる微細化に対応できるゲート構造を実現できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜と、該ゲート絶縁膜の上に形成されたゲート電極とを備えている。ゲート絶縁膜は、アナターゼ型酸化チタンを主成分とする高誘電率絶縁膜5であり、ゲート電極は、第1の金属膜6又は第2の金属膜8を含む導電膜から構成されている。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコン膜との接触に起因するショットキー抵抗を低減する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタは、第1の活性領域の表面の一部を覆い二酸化シリコンよりも高い誘電率を有する第1の絶縁材料からなる第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成された第1の金属材料からなる第1の金属ゲート電極と、第1の金属ゲート電極上に形成されたp型導電型の第1の多結晶シリコン膜を有する。

(もっと読む)

半導体装置とその製造方法

【課題】 チャンネルドーピングあるいは複雑なゲート電極パターン化の必要性なしに、複数のトランジスタが多閾値電圧を有する半導体装置を提供する。

【解決手段】 半導体装置及びその製造方法において、第1トランジスタは、第1材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第2トランジスタは、第3材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第3トランジスタは、第1材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第4トランジスタは、第3材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第1材料乃至前記第4材料の仕事関数は互いに異なる。第1トランジスタ乃至第4トランジスタは、互いに異なる閾値電圧を有する。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用ボトムコンタクト型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。多階調マスクを用いたフォトリソグラフィ工程を用いることで、作製工程を簡略化できる。

(もっと読む)

半導体装置

【課題】小面積、低電力動作、高速動作を並立する論理ゲートを含む半導体装置の構成を提供する。

【解決手段】本発明に係る半導体装置は、基板上にゲート絶縁膜を介してゲート電極と半導体層が配置され、半導体層に接続してソース電極とドレイン電極とが配置される薄膜トランジスタを2つ以上含む論理ゲートで構成される。少なくとも第一の薄膜トランジスタは、そのゲート電極が電気的に浮遊状態にあり、かつ、その半導体層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。また、少なくとも第二の薄膜トランジスタは、そのゲート電極が入力端子に接続され、かつ、そのチャネル層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

EL表示装置

【課題】開口率を向上することができるEL表示装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線と有するEL表示装置である。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

半導体装置

【課題】トンネル型FETのオン電流とオフ電流との比と、単位基板面積あたりのオン電流を増大させる。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側面に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記半導体基板上に順に積層された第1導電型の下部主端子層と、中間層と、第2導電型の上部主端子層とを有し、前記ゲート絶縁膜を介して前記ゲート電極の側面に形成された積層体とを備える。さらに、前記上部主端子層は、前記ゲート電極の側面に、前記ゲート絶縁膜と半導体層を介して形成されている。

(もっと読む)

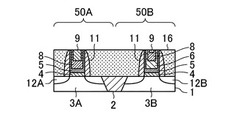

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置

を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以

下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶

縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下

の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半

導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートラストプロセスの工程数を削減しつつ、所望の信頼性及び特性が得られるメタルゲート電極を備えたMISFETを実現できるようにする。

【解決手段】各ゲート溝の少なくとも底面上にゲート絶縁膜112及び保護膜113が順次形成されている。一方のゲート溝内の保護膜113の上には第1の金属含有膜114a及び第2の金属含有膜114bが順次形成されており、他方のゲート溝内の保護膜113の上には第2の金属含有膜114bが形成されている。一方のゲート溝内の保護膜113の厚さと比べて、他方のゲート溝内の保護膜113の厚さは薄い。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜の膜厚が異なる複数のトランジスタを有する半導体装置において、オフリークの増加を抑制する。

【解決手段】半導体装置は、半導体層上に形成された第1MISトランジスタ及び第2MISトランジスタを備える。第1MISトランジスタは、活性領域101が素子分離膜102に囲まれた第1活性領域と、第1活性領域上に第1ゲート絶縁膜111を介して形成された第1ゲート電極104とを有する。第2MISトランジスタは、活性領域101が素子分離膜102に囲まれた第2活性領域と、第2活性領域上に第2ゲート絶縁膜103を介して形成された第2ゲート電極104とを有する。第2ゲート絶縁膜103は、第1ゲート絶縁膜111よりも薄い。第2MISトランジスタは、少なくとも第2ゲート電極104の下方において、第2活性領域と素子分離膜102との境界部上に、素子分離膜102の側面を覆う保護絶縁膜108を有する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

41 - 60 / 1,843

[ Back to top ]