Fターム[5F048BB11]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | ゲート絶縁膜材料 (1,843)

Fターム[5F048BB11]に分類される特許

21 - 40 / 1,843

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

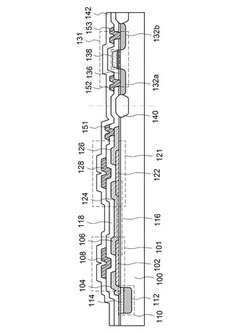

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

トンネルトランジスタ、トランジスタを含む論理ゲート、論理ゲートを使用するスタティックランダムアクセスメモリ、およびトンネルトランジスタの製造方法

【課題】第1、第2ゲートを有するトンネルトランジスタで、第1、第2のゲート間の電圧の差がより小さい場合にしようできるトンネルトランジスタを提供する。

【解決手段】ドレイン2、ソース4およびドレイン2とソース4との間で電流を制御するための少なくとも第1ゲート6とを含み、第1および第2のゲート誘電体材料7、11の第1側9、13が、それぞれ第1および第2の半導体部分14、15に実質的に沿って、実質的に接続して配置されたトンネルトランジスタ1。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

CMOS半導体装置の製造方法及びCMOS半導体装置

【課題】マイクロコンタクト印刷の版を凹版として使用し、微細な電気回路と高生産性のCMOS半導体装置の製造方法を提供するものである。

【解決手段】Pチャネル型電界効果トランジスタのPチャネル領域101とNチャネル型電界効果トランジスタのNチャネル領域102とを、凹版601を用いた印刷によって形成するようにし、凹版601が、第1凹部602と第2凹部603とを備え、インクジェット法によって、第1凹部602にP型半導体インク111を供給し、第2凹部603にN型半導体インク112を供給する工程と、インク供給後に、凹版601を被印刷基板001に押しつけて、第1凹部602に供給したP型半導体インク111と第2凹部603に供給したN型半導体インク112とを一括して被印刷基板001に転写する工程と、を含むCMOS半導体装置の製造方法を提供する事により、上記課題を解決する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】特性の低下を抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、が含まれている。p型半導体層8に含まれるp型不純物として、少なくとも電子走行層3及び電子供給層5のいずれかを構成する元素と同種の元素が用いられている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

酸化物半導体層、半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

半導体装置、及びダイオード

【課題】酸化亜鉛を含む半導体膜を用いたダイオードを提供する。

【解決手段】基板上の、酸化亜鉛を含み、チャネル形成領域を有する半導体膜と、前記半

導体膜とゲート電極との間のゲート絶縁膜と、前記半導体膜と電気的に接続されるソース

電極及びドレイン電極と、を有し、前記ゲート電極は、前記ソース電極及び前記ドレイン

電極の一方と電気的に接続される。前記ゲート電極は前記チャネル形成領域の上又は下に

あり、前記ゲート電極は前記ソース電極及び前記ドレイン電極の上にあってもよい。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

21 - 40 / 1,843

[ Back to top ]