Fターム[5F058BD06]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 少なくとも一層が酸化物 (2,674) | 添加物含有 (311)

Fターム[5F058BD06]に分類される特許

41 - 60 / 311

半導体装置の製造方法

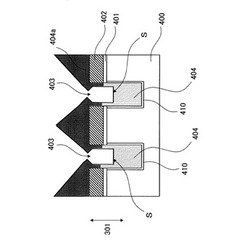

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する脱水化または脱水素化された酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成する。

(もっと読む)

半導体装置

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】ポーラスLow−k膜からなる第2ファイン層の層間絶縁膜IL2内の空孔10および空孔11の平均径を1.0nm以上1.45nm未満とすることで、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】有機シロキサン系絶縁膜を用いて電気的特性に優れた半導体装置を製造する方法を提供する。

【解決手段】下層配線の上にこの順で形成された第1〜第3の絶縁膜をドライエッチングして該下層配線に至る開口部を形成し、該開口部の内面と該第3の絶縁膜の上にバリアメタル膜を形成し、該バリアメタル膜の上に該開口部を埋める導電層を形成し、該第3の絶縁膜上の該導電層と該バリアメタル膜、及び該第2、第3の絶縁膜の一部を除去し該下層配線に電気的に接続する上層配線を形成し、露出した該第2の絶縁膜と該導電層の表面を還元性プラズマ処理し、

該第2の絶縁膜は下記式で表されるアルキルアルコキシシランと非酸化性ガスとを用い、500Pa以下でプラズマCVD法により形成する

RwSixOy(OR´)z

R及びR´はCH3、wxzは正の整数、yは0または正の整数、(w/x)=2である。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】基板の表面粗度によらず膜表面が平坦であり、信頼性が高く、製造コストを低減させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】可撓性のプラスチック基板10上に、ゲート電極11、ゲート絶縁層12、半導体活性層13、ソース電極14、及びドレイン電極15を順次形成するボトムゲート型薄膜トランジスタ1の製造方法である。ゲート絶縁層12は、プラスチック基板10上に下部層12aと該下部層12a上に積層された少なくとも一層以上の上部層12bとがこの順で形成されてなり、下部層12aは、炭素含有酸化シリコンを含む材料からなり、下部層12aの炭素濃度が、15atm%以上40atm%以下となるように真空紫外光CVD法により形成される。

(もっと読む)

成膜方法及び成膜装置

【課題】低誘電率膜への付着性が高く、低誘電率膜中への銅の拡散を効果的に防止できるバリア膜の成膜方法を提供する。

【解決手段】 成膜方法は、成膜装置100の処理容器1内に、絶縁膜が設けられたウエハWを配置する工程と、処理容器1内にTEOSなどのシリコン原子を含む化合物のガスと水蒸気などのOH基供与性ガスを供給し、絶縁膜の表面にSi−OH基を形成させる表面改質工程と、処理容器1内にマンガン含有材料を含む成膜ガスを供給し、CVD法によりSi−OH基が形成された絶縁膜の表面にマンガン含有膜を成膜する成膜工程と、を備えている。

(もっと読む)

太陽電池の製造方法

半導体装置およびその製造方法

【課題】誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の広幅の配線におけるディッシングの抑制と、抵抗の抑制と、を両立させる。

【解決手段】半導体装置100は、半導体基板1と、半導体基板1上に形成された配線層絶縁膜9と、を有している。配線層絶縁膜9には、第1配線用配線溝11と、第1配線用配線溝11よりも広幅の第2配線用配線溝12と、が形成されている。第1配線用配線溝11内には第1配線21が、第2配線用配線溝12内には第2配線22が、それぞれ形成されている。第2配線用配線溝12の底面の少なくとも一部分は、絶縁膜(例えば、絶縁膜4及びエッチングストッパー膜5)によって、第2配線用配線溝12の上端に達しない高さで第1配線用配線溝11の底面よりもかさ上げされた、かさ上げ部15となっている。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ内に確実に絶縁膜を残すことができる半導体装置およびその製造方法を提供する。

【解決手段】トレンチ内にゲート電極を形成した後、一部にリフロー性の絶縁膜を含む絶縁膜を形成して平坦化する。その後、CMP法により平坦化した表面を研磨し、トレンチ内に絶縁膜を充填する。その際、フィールド酸化膜の表面も研磨する。

(もっと読む)

低誘電率誘電体を含む超小型電子構造およびその構造内の炭素分配を制御する方法

本発明の実施形態は、超小型電子構造の形成に関する。32nmの次のテクノロジーノード向けの低誘電率誘電体材料は、約2.6未満の誘電率を呈する必要がある。本発明により、全体として超小型電子構造の曲げおよび剪断強度の完全性を向上させながら、そのような低誘電率誘電体材料を使用する半導体デバイスを形成することが可能になる。  (もっと読む)

(もっと読む)

マンガン含有低誘電率膜及びその製造方法、半導体装置の製造方法並びに成膜装置

【課題】マンガン含有材料を利用して、低誘電率膜への銅の拡散を防止する。

【解決手段】成膜装置100では、制御部70の制御に基づき、処理容器1内を真空にして、ヒーター6によりウエハWを加熱しつつ、シャワーヘッド11のガス吐出孔13a,13bからウエハWへ向けて低誘電率材料とマンガン含有材料とを含む成膜ガスを供給する。高周波電源23からシャワーヘッド11に高周波電力を供給することにより、成膜ガスを解離させ、処理容器1内に成膜ガスのプラズマを生成させる。このプラズマによって、ウエハWの表面にMnを含有するSiCOH膜を成膜する。

(もっと読む)

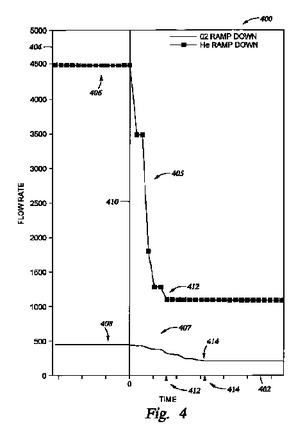

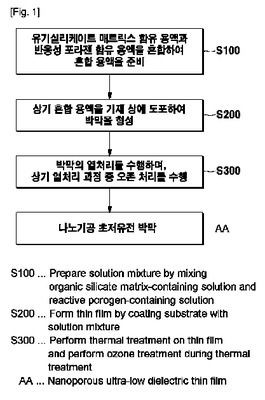

高温オゾン処理を含むナノ細孔の超低誘電薄膜の製造方法及びこれによって製造されたナノ細孔の超低誘電薄膜

高温オゾン処理を含むナノ細孔の超低誘電薄膜の製造方法及びこれによって製造されたナノ細孔の超低誘電薄膜が提供され、前記製造方法は、有機シリケートマトリックス−含有溶液と反応性ポロゲン−含有溶液とを混合して混合溶液を準備し、前記混合溶液を基材上に塗布して薄膜を形成し、前記薄膜を熱処理し、前記熱処理の過程中にオゾン処理を行うことを含み、このような製造方法によって製造されたナノ細孔の超低誘電薄膜は、高温のオゾン処理及び処理温度の最適化による薄膜内の細孔のサイズと分布度の改善を通じて、2.3以下の誘電率と10GPa以上の機械的強度とを有することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線間のリーク電流が発生することを抑制し、配線間容量の増大を抑制する。

【解決手段】半導体装置100の製造方法は、絶縁膜2にダマシン配線を形成する工程(A)を含む半導体装置100の製造方法であって、基板1上に形成された絶縁膜2の表面にプラズマ処理を行い、絶縁膜2中の水分を脱離する工程(B)と、シリル化ガスを含む雰囲気中でアニール処理を行い、絶縁膜2をシリル化する工程(C)と、を含む。

(もっと読む)

誘電体膜の製造方法

【課題】比誘電率の低下を軽減しつつリーク電流値を低減し、スパッタ率の低下による堆積速度の減少を抑制し、かつ、面内均一性に優れた誘電体膜の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る誘電体膜の製造方法は、基板上に、AlとSiとOを主成分とする金属酸化物である誘電体膜を形成する誘電体膜の製造方法であって、Al元素とSi元素のモル比率Si/(Si+Al)が0<(B/(A+B))≦0.1であり、非晶質構造を有する金属酸化物を形成する工程と、該非晶質構造を有する金属酸化物に1000℃以上のアニール処理を施し、結晶相を含む金属酸化物を形成する工程と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】キャパシタ容量の低下を抑制する半導体装置を提供する。

【解決手段】半導体装置は、上部電極膜(上部電極膜114、上部電極膜116)と下部電極膜110との間に容量絶縁膜112が設けられた容量素子を備え、下部電極膜110は、少なくとも容量絶縁膜112と接する部分に、多結晶窒化チタンを有する。

(もっと読む)

ポリシラザンを含むコーティング組成物

【課題】埋設性と塗布性とに優れ、すぐれた膜物性を有するシリカ質膜を形成することができるコーティング組成物とそれを用いたシリカ質膜の形成方法の提供。

【解決手段】ペルヒドロポリシラザンと溶媒とを含んでなるコーティング組成物であって、前記ペルヒドロポリシラザンの分子量分布曲線が、分子量800〜2,500の範囲と、分子量3,000〜8,000の範囲とにそれぞれ極大を有し、重量平均分子量Mwと数平均分子量Mnの比Mw/Mnが6〜12である、コーティング組成物。このコーティング組成物ギャップを有する基板上に塗布し、1000℃以下で加熱することにより、ギャップ深部まで埋設されたシリカ質膜を形成させることができる。

(もっと読む)

41 - 60 / 311

[ Back to top ]