Fターム[5F058BD15]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 少なくとも一層がシリコン酸化窒化物 (338)

Fターム[5F058BD15]の下位に属するFターム

添加物含有 (32)

Fターム[5F058BD15]に分類される特許

141 - 160 / 306

透過性誘電体膜の製造方法

【課題】本発明の主題は、透過性誘電体膜の製造方法である。

【解決手段】本発明は、

a)ケイ素と、炭素と、水素と、酸素と、場合により窒素及び/又はフッ素とを含む材料であり、前記材料はケイ素−炭素結合を過半数含み、ケイ素−酸素結合を前記材料中の酸素が原子数で30%を超えない程度に一部含む材料の膜を基板に堆積する段階と、

b)段階a)において堆積された膜中のケイ素−酸素結合を化学物質によって選択的に分解する段階と、

を含む透過性誘電体膜の製造方法に関する。

応用例:エアギャップの形成、特に集積回路のエアギャップ相互接続の製造のための化学物質を透過する膜を通じた化学物質の拡散による犠牲材料の分解を含む全ての製造方法におけるマイクロエレクトロニクス及びマイクロテクノロジー。

(もっと読む)

ゲート絶縁膜の形成方法

【課題】ゲート絶縁膜に用いる高誘電体金属酸化膜又は高誘電体金属シリケート膜におけるリーク電流を低減できるようにする。

【解決手段】高誘電体金属シリケートからなるゲート絶縁膜の形成において、金属等を含む前駆体の暴露時間には、表面吸着反応により成膜レートが飽和する時間を用い、酸化剤の暴露時間には、金属酸化膜の組成が化学量論値の97%以上となる時間を用いてALD堆積を行う。

(もっと読む)

絶縁膜の形成方法

【課題】高誘電率ゲート絶縁膜としての使用に適し、低EOTと低界面準位が両立できる絶縁膜を形成する。

【解決手段】Si基板101の上にスパッタによりHf−Si膜102を形成する第1工程と、Hf−Si膜を酸化してHfSiO膜103を形成する第2工程と、HfSiO膜を窒化してHfSiON膜105を形成する第3工程を含む。第2工程において、Hf−Si膜を酸化する際にHf−Si膜に近紫外光を照射し、Si基板の表層部を酸化してSiO2膜104を形成する。近紫外光の波長は220〜380nmである。近紫外光の光源として、Kr2エキシマランプ、KrFエキシマランプ、XeClエキシマランプまたはXeFエキシマランプを用いる。第2工程では、プラズマ励起、光励起またはオゾン供給を用いて活性化された酸素を用いてHf−Si膜を酸化する。

(もっと読む)

半導体装置の製造装置および半導体装置の製造方法

【課題】Si基板上のSiO2膜の窒化において、Nラジカルの生成効率が高く、かつN2+ラジカルの生成効率が低減することにより、SiO2表面を充分窒化し、かつSiO2/Si界面の窒化を防止し、トランジスタの閾値電圧のシフトを防止した半導体装置の製造装置および製造方法を提供する。

【解決手段】本発明の半導体装置の製造装置は、N2+のSi基板上SiO2膜への到達を防止し、SiO2/Si界面の窒化を防止するものであり、第1の態様として、処理室と、ラジアルラインスロットアンテナと、第1ガスを導入する第1ガス導入口と、第2ガスを導入する第2ガス導入口とを少なくとも備える半導体装置の製造装置であって、処理室に、負に帯電した金属製のイオン除去プレートを備え、第1ガス導入口と第2ガス導入口とが、処理室に設けられ、第1ガスがイオン除去プレートを通過した後、第2ガスと混合される位置に設けられる半導体装置の製造装置である。

(もっと読む)

半導体装置の製造方法

【課題】APM洗浄による側壁絶縁膜のエッチングレートを低減させることができる。

【解決手段】半導体装置の製造方法では、エッチング抑制層107を形成した後に、シリコン基板(半導体基板)104内にn型エクステンション領域(拡散層)112およびp型エクステンション領域(拡散層)115を形成した後、エッチング抑制層107を形成した状態でシリコン基板104の上面を洗浄する。

(もっと読む)

半導体装置の作製方法、半導体装置及び電子機器

【課題】高い絶縁破壊耐圧特性、低い誘電率、及び、低い吸湿性を備えた絶縁層を有する半導体装置を提供することを課題とする。また、該半導体装置を用いた高性能且つ信頼性の高い電子機器を提供することを課題とする。

【解決手段】酸化窒化珪素や窒化酸化珪素のような窒素を含有する絶縁体と、フッ素が添加された酸化窒化珪素やフッ素が添加された窒化酸化珪素のような窒素及びフッ素を含有する絶縁体とを交互に堆積させて、絶縁層を形成する。窒素及びフッ素を含有する絶縁体を、窒素を含有する絶縁体により挟み込むことで、窒素及びフッ素を含有する絶縁体の吸湿を防ぐことができ、絶縁破壊耐圧を向上することができる。また、フッ素を含有させることにより、誘電率を低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】 窒素導入量を低減させることなく、絶縁膜へのダメージの導入を抑制し、かつ絶縁膜と半導体基板との界面における窒素濃度の増大を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の表面上に、シリコンと酸素とを含む絶縁膜を形成する。(b)前記絶縁膜を活性窒素雰囲気に晒し、該絶縁膜に、その表面側から窒素を導入する。(c)前記工程(b)の後、酸素原子含有ガス中で熱処理を行う。(d)前記工程(c)の後、前記工程(b)と工程(c)とを、この順番に少なくとも1回繰り返す。

(もっと読む)

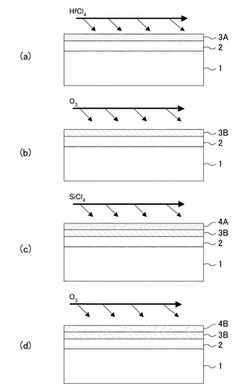

半導体素子の製造方法

【課題】 本発明は、トンネル酸化膜の形成時に酸化膜に窒素を蓄積させた後、後続で酸素を注入するための工程を行ってSi−N結合をSi−O−N結合に変更することにより、窒素プロファイル(N profile)の変化による特性劣化の防止、電気的ストレスの緩和及び酸素密度の増加などを通じてサイクリング(cycling)及び電荷保存(retention)特性などの素子特性を向上させることができる半導体素子の製造方法を提供するものである。

【解決手段】 半導体基板上に第1の絶縁膜を形成する段階と、前記半導体基板と前記第1の絶縁膜の界面に窒素を蓄積させて第2の絶縁膜を形成する段階と、前記第2の絶縁膜に酸素を注入して第3の絶縁膜に変更させる段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】SiOF膜を含む層間絶縁膜にダマシン法で埋め込み配線を形成する半導体集積回路装置において、埋め込み配線用の配線溝を形成する際に用いるエッチングストッパ層とSiOF膜との界面剥離を防止する。

【解決手段】SiOF膜26、29を含む層間絶縁膜をドライエッチングして形成した配線溝32の内部にダマシン法でCu配線33を埋め込む際、上記ドライエッチングのエッチングストッパ層を構成する窒化シリコン膜28とSiOF膜26との間に酸窒化シリコン膜27を介在させ、SiOF膜26中で発生した遊離のFを酸窒化シリコン膜27でトラップする。

(もっと読む)

膜形成方法、半導体装置およびその製造方法

【課題】Vfbシフトと移動度低下を低減し、界面特性にすぐれたゲート絶縁膜構成を有する半導体装置を提供する。

【解決手段】シリコン基板を直接窒化して、シリコン窒化膜を形成し、前記シリコン窒化膜を、N2OとH2を含む混合ガスでアニールして、シリコン酸窒化(SiON)膜を形成する。このようなシリコン酸窒化膜は、半導体装置のゲート絶縁膜に適用することができる。

(もっと読む)

環境感受性デバイス、環境感受性素子の封止方法

【課題】 環境感受性デバイスの水蒸気による劣化を防止することを目的とする。

【解決手段】基板上に、環境感受性素子と、バリア性積層体とを、該順に有し、かつ、該バリア性積層体は、少なくとも1層の水素化窒化珪素層と、少なくとも1層の他の無機層とを有する、環境感受性デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】移動度の低下を極力抑えつつゲートリーク電流が低い良好なゲート絶縁膜を有するMOSFETを含む半導体装置、及びその製造方法を提供する。

【解決手段】半導体層と、ゲート電極と、膜厚が1nm以上で少なくとも半導体層側からその厚み方向に1nmまでの領域は窒化酸化シリコン膜(SiON)から構成され、かつシリコンと酸素の原子数比(O/Si)が0.01〜0.30、シリコンと窒素の原子数比(N/Si)が0.05〜0.30であるゲート絶縁膜と、ソース/ドレイン領域と、を備えたMOSFETを有する半導体装置。

(もっと読む)

半導体集積回路装置

【課題】基板とゲート絶縁膜との界面近傍における窒素濃度を必要以上に高くすることなく、ゲート絶縁膜中の窒素濃度を高める。

【解決手段】電界効果トランジスタのゲート絶縁膜は、半導体基板に近い第1領域と、第1領域よりもゲート電極に近い第2領域とで窒素濃度のピークが異なっており、第1領域における窒素濃度のピークは、2.5atomic%〜10atomic%であり、第2領域における窒素濃度のピークは、第1領域における窒素濃度のピークよりも高い。

(もっと読む)

半導体装置の作製方法

【課題】不純物の混入を低減された膜を有する半導体素子を有する半導体装置の作製方法を提案することを課題とする。さらには、歩留まり高い半導体装置の作製方法を提案する。

【解決手段】絶縁表面を有する基板上に設けられた半導体層に接して、プラズマCVD装置を用いて絶縁膜を形成する半導体装置の作製方法において、当該絶縁膜の不純物を含まない膜でプラズマCVD装置の反応室の内壁をコーティングした後、反応室に基板を挿入し、基板上に上記絶縁膜を成膜することにより、不純物を低減した絶縁膜を基板上に形成することができる。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】表面リーク電流を低減することができる、III族窒化物半導体を用いた窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この電界効果トランジスタは、n型GaN層3、p型GaN層4およびn型GaN層5が、順に積層された窒化物半導体積層構造部2を備えている。ゲート絶縁膜9が形成されている。このゲート絶縁膜9は、窒化物半導体積層構造部2の表面全域に接して形成された窒化シリコン膜20と、この窒化シリコン膜20の上に形成された酸化シリコン10膜とを備えている。ゲート絶縁膜9の上には、ゲート絶縁膜9を挟んで領域12に対向するようにゲート電極11が形成されている。また、窒化物半導体積層構造部2の引き出し部6の表面には、ドレイン電極7が接触形成されている。一方、窒化物半導体積層構造部2のn型GaN層5の頂面には、ソース電極13が接触形成されている。

(もっと読む)

STI構造を有する半導体素子及びその製造方法

【課題】トレンチ内に不純物ドーピング酸化膜ライナが形成されているSTI構造を有する半導体素子及びその製造方法を提供する。

【解決手段】活性領域102に接するようにトレンチの内壁を覆う側壁ライナ130と、側壁ライナ130上に形成された不純物ドーピング酸化膜ライナ140aと、トレンチを埋め込むギャップフィル絶縁膜150とを備える半導体素子である。不純物ドーピング酸化膜ライナ140aを形成するために、側壁ライナ130上に酸化膜ライナを形成した後、プラズマ雰囲気下で酸化膜ライナに不純物をドーピングする。

(もっと読む)

不揮発性メモリデバイス用インターポリ誘電体を形成するための統合スキーム

【課題】 不揮発性メモリデバイスの漏れ電流を維持するか又は減少させつつ、デバイス寸法の減少を可能にする電子デバイス及び電子デバイスを形成する方法の提供。

【解決手段】 一実施形態において、不揮発性メモリデバイスを製造する方法は、基板上にフローティングゲート多結晶層を堆積させるステップと、フローティングゲート多結晶層上に酸化シリコン層を形成するステップと、酸化シリコン層上に第一酸窒化シリコン層を堆積させるステップと、第一酸窒化シリコン層上に高k誘電物質を堆積させるステップと、高k誘電物質上に第二酸窒化シリコンを堆積させるステップと、第二酸窒化シリコン層上に制御ゲート多結晶層を形成するステップとを含む。一実施形態において、高k誘電物質層は、酸窒化シリコンハフニウムを含む。

(もっと読む)

半導体素子及びその製造方法

【課題】MOSFET等のデバイスのための高誘電率膜の製造方法を提供する。

【解決手段】Si基板101上のSiO2膜(又はSiON膜)102上にHf金属膜103をスパッタし、それを熱酸化処理してHfSiO膜104を形成する。その上にTi金属膜105をスパッタし、それを熱酸化処理して、TiO2膜106を形成する。TiO2膜106上に、TiN金属膜107を堆積させる。これら一連の処理は、大気に晒すことなく真空中で一貫して行われる。形成されたTiN/TiO2/HfSiO/SiO2/Si構造は、EOT<1.0nm, 低リーク電流, ヒステリシス<20mVを満たしている。

(もっと読む)

半導体装置およびその製造方法

【課題】浮遊ゲート電極または制御ゲート電極の特性ばらつきを可及的に抑制し、トンネル絶縁膜の信頼性の低下を防止し、かつストレス誘起リーク電流を抑制することを可能にする。

【解決手段】第1導電型の半導体層を有する基板1と、半導体層に対向して設けられた一対の第2導電型のソース/ドレイン領域12と、ソース/ドレイン領域間の半導体層上に設けられた第1の絶縁膜14と、第1の絶縁膜上に設けられ、ソース/ドレイン領域が対向する方向に沿って亜粒界17が形成された単結晶の半導体を含む浮遊ゲート電極16と、浮遊ゲート電極上に設けられた第2の絶縁膜18と、第2の絶縁膜上に設けられた制御ゲート電極20と、を有するメモリセルと、を備えている。

(もっと読む)

高品質インタフェースによってゲルマニウム上に高品質シリコン誘電膜を堆積するための方法

【課題】ゲルマニウム基板上にシリコン酸化物やシリコン酸窒化物などの誘電層を堆積するための方法を提供する。

【解決手段】ゲルマニウム基板上に誘電層を形成する場合のゲルマニウム基板の酸化を防止するためにゲルマニウム基板上にバリア層を堆積するステップ130を伴う。特定の実施形態において、シリコン層がゲルマニウム基板上に堆積されてバリア層を形成する。特定の実施形態において、ゲルマニウム基板の窒化が、バリア層として機能するGexNy層を形成する。特定の実施形態において、窒化シリコン層がゲルマニウム基板上に堆積されてバリア層を形成する。

(もっと読む)

141 - 160 / 306

[ Back to top ]