Fターム[5F058BD15]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 少なくとも一層がシリコン酸化窒化物 (338)

Fターム[5F058BD15]の下位に属するFターム

添加物含有 (32)

Fターム[5F058BD15]に分類される特許

101 - 120 / 306

半導体装置の製造方法

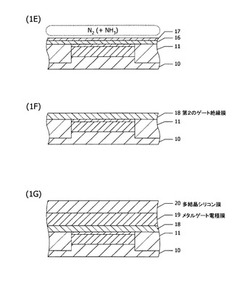

【課題】 ハフニウムシリケートからなるゲート絶縁膜に、アルミナ膜を重ねると、等価酸化膜厚を薄くすることが困難になる。また、ハフニウムシリケートからなるゲート絶縁膜内にAlが拡散すると、正孔の移動度が低下してしまう。

【解決手段】 半導体基板(10)の上に、HfとOとを含む絶縁膜(16)を形成する。この絶縁膜の上に、構成元素として酸素とチタンとを含むキャップ膜(17)を形成する。絶縁膜及びキャップ膜を、窒素ガスまたは希ガス雰囲気中で熱処理し、キャップ膜中のチタンを絶縁膜内に拡散させることにより、ゲート絶縁膜(18)を形成する。ゲート絶縁膜の上に、ゲート電極膜(19)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】半導体装置の製造方法に於いて、簡便な方法により、処理容器の内壁面をプラズマによりコーティングし、内壁面から酸素等の汚染原子が放出されることを抑止し、成膜品質を向上させる。

【解決手段】基板5を処理する処理容器1の内面を、プラズマ処理により反応ガス19でコーティング処理する工程と、前記処理容器内に基板を搬入する工程と、前記反応ガスを用いて基板をプラズマ処理する工程と、前記処理容器内から基板を搬出する工程とを有する。

(もっと読む)

膜形成方法および膜形成装置

【課題】基板を低温に維持したまま、膜の高温アニール等の熱処理をし、または熱CVD膜を基板表面に形成することができる安価な膜形成方法および膜形成装置を提供する。

【解決手段】支持台4上に支持された基板1の表面上に、複数の高温ガスビーム2b,2cを相互に所要の間隔を置いてほぼ垂直に吹き付けると基板表面1a上の膜のみをアニールできる。これと共に、これら高温ガスビーム2b,2cと前記基板1の表面とにより画成された高温空間6に、堆積性を有する膜形成用の熱分解ガス7を供給し、それを熱分解させて活性種を生成させ基板1の表面に吹き付けることにより、熱CVD膜を形成することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】本発明は、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上にフォトレジストを塗布する工程と、前記下地電極の外周部より中央側において前記フォトレジストに開口部を形成する工程と、比誘電率が10以上のhigh-k材料から構成される高誘電率膜を成膜する工程と、前記下地電極の外周部より中央側に前記高誘電率膜が残るように、リフトオフを行なう工程と、前記リフトオフにより残された前記高誘電率膜上に上地電極を形成する工程と、を備えることを特徴とするものである。

(もっと読む)

薄膜多層配線基板およびその製造方法

【課題】 剥離の発生の少ない薄膜多層配線基板とその製造方法を提案する。

【解決手段】 少なくとも一つの前記配線層が、下層の配線層上に形成された第一のSiO2薄膜と、前記第一のSiO2薄膜上に形成されたSiON薄膜と、前記SiON薄膜上に形成された第二のSiO2薄膜と、前記第二のSiO2薄膜に埋め込まれて形成された配線導体と、前記配線導体と接続しかつ前記第一のSiO2薄膜、前記SiON薄膜および前記第二のSiO2薄膜を貫通して前記下層の配線層の配線導体と電気的に接続するビア導体と、前記第二のSiO2薄膜上に形成されたSiN薄膜と、で構成されている。

(もっと読む)

SOI基板の作製方法

【課題】単結晶半導体層とベース基板との密着性を向上させ、貼り合わせ不良を低減することを目的の一とする。

【解決手段】半導体基板の表面にラジカル処理を行うことにより、半導体基板に第1の絶縁膜を形成し、第1の絶縁膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板に脆化領域を形成し、第1の絶縁膜上に第2の絶縁膜を形成し、第2の絶縁膜の表面とベース基板の表面とを接合させた後に熱処理を行い、脆化領域において分離することにより、ベース基板上に第1及び第2の絶縁膜を介して半導体層を形成し、半導体層にエッチング処理を行い、エッチング処理が行われた半導体層にレーザビームを照射する。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のエアギャップ構造より、さらに容量及び容量ばらつきを低減することができる。

【解決手段】 基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。このとき、狭い配線間スペース底部の絶縁膜17の膜厚保は、配線26上の絶縁膜31の膜厚より、薄く成膜することで細線ピッチの配線容量を効率良く低減する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

成膜方法及び成膜装置

【課題】原料ガスを間欠的に供給する際に、安全性を維持しつつ多量の原料ガスを処理容器内へ供給することができ、この結果、成膜レートを向上できるのみならず、膜中における原料ガスに含まれる元素の濃度をコントロールして、例えばこの元素濃度を高くすることが可能な成膜方法を提供する。

【解決手段】被処理体Wが収容されて真空引き可能になされた処理容器4内で被処理体Wの表面に薄膜を形成する成膜方法において、処理容器4内へ原料ガスを、間に間欠期間を挟んで複数回供給して原料ガスを被処理体Wの表面に吸着させる吸着工程と、処理容器4内へ反応ガスを供給して被処理体Wの表面に吸着している原料ガスと反応させて薄膜を形成する反応工程とを交互に複数回繰り返し行うようにする。

(もっと読む)

不揮発性半導体記憶装置のメモリセル

【課題】微細化を行っても、書き込み/消去特性、繰り返し特性、およびリテンション特性に優れたMONOS型メモリセルを提供する。

【解決手段】不揮発性半導体記憶装置のメモリセルは、MONOS型の構造をしており、電荷蓄積層が複数の絶縁物層から構成される。それらの絶縁膜の隣接する層間の伝導帯端エネルギーと価電子帯端エネルギーの関係は、トンネル絶縁膜からブロック絶縁膜に向かって、次第に大きくなるか、または、次第に小さくなるかのいずれかである。さらに、ブロック絶縁膜の比誘電率をεrとすれば、電荷蓄積層とブロック絶縁膜の間のエネルギー障壁は、電子に対して4.5εr-2/3(eV)以上、3.8eV以下、正孔に対して4.0εr-2/3(eV)以上、3.8eV以下である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】SiO2/SiC構造を備える、たとえばMOSFETなどの半導体装置は、界面準位密度の低減が不十分である。

【解決手段】SiC基板1の一方の主表面上に形成させたSiCエピタキシャル層2の一方の主表面上に、あらかじめSi薄膜3を形成させて、このSi薄膜3の内部に窒素原子を注入させる。この状態で、SiCエピタキシャル層2の一方の主表面上を酸窒化させる。

(もっと読む)

絶縁破壊寿命シミュレーション方法、シリコンウェーハ表面の品質評価方法およびプログラム

【課題】 絶縁体薄膜の信頼性評価において、絶縁破壊の確率過程にシリコンウェーハ表面の品質状態を数理統計的に組み込ませる。

【解決手段】 シリコンウェーハ上に形成した絶縁体薄膜をモンテカルロ法によりコンピュータシミュレーションする絶縁破壊寿命シミュレーション方法は、絶縁破壊の測定条件を設定するステップ、ウェーハ表面欠陥の分布および欠陥サイズを設定するステップ、絶縁体薄膜をセルにメッシュ分割し上記表面欠陥をセルにくり込むステップ、絶縁体薄膜の絶縁破壊に至る時間の基準尺度を算出するステップ、シリコンウェーハ上に設定する全キャパシタに亘りそれ等の絶縁体薄膜の絶縁破壊の確率過程をモンテカルロ法によりコンピュータシミュレーションするステップ、全キャパシタの絶縁破壊について統計処理するステップ、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留まりを向上させる。

【解決手段】

半導体基板1の主面にゲート絶縁膜用の絶縁膜を形成する。それから、プラズマ処理装置51の処理室51a内で、半導体基板1の主面のゲート絶縁膜用の絶縁膜をプラズマ窒化する。その後、プラズマ処理装置51から半導体基板1をフープ31内に移送し、フープ31をベイステーションBSに移動させてそこで待機させて半導体基板1を保管する。ベイステーションBSに待機している間、半導体基板1を保管しているフープ31内に、フープ31に設けられた第1の呼吸口から窒素ガスを供給し、フープ31に設けられた第2の呼吸口からフープ31内の窒素ガスを排出する。その後、フープ31を熱処理装置52に移動させて、半導体基板1を熱処理装置52の処理室内に搬入して熱処理する。

(もっと読む)

誘電体膜の形成方法

【課題】薄い絶縁物の分子層で覆われたSi基板表面にCVD法により誘電体膜を形成する際のインキュベーション時間をなくし、得られる誘電体膜の均一性を向上させると同時に、誘電体膜の膜厚方向の組成を制御する。

【解決手段】Si基板上への誘電体膜の形成方法は、前記Si基板上に第一の金属の気相分子化合物を実質的に一様に吸着させ、前記Si基板上を前記第一の金属の気相分子化合物により覆う第一の工程と、前記Si基板を覆う前記第一の金属の気相分子化合物を酸化雰囲気中で分解し、前記Si基板上に前記第一の金属を含む第一の誘電体分子層を形成する第二の工程と、前記Si基板上に第二の金属の気相分子化合物を実質的に一様に吸着させ、前記Si基板上を前記第二の金属の気相分子化合物により覆う第三の工程と、前記Si基板を覆う前記第二の金属の気相分子化合物を酸化雰囲気中で分解し、前記第一の誘電体分子層上に前記第二の金属を含む第二の誘電体分子層を形成する第四の工程と、を含む

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】膜中の炭素、水素、窒素、塩素等の不純物濃度が極めて低い絶縁膜を低温で形成することができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】基板を収容した処理容器内に所定元素を含む原料ガスを供給することで、基板上に所定元素含有層を形成する工程と、処理容器内に窒素を含むガスを活性化して供給することで、所定元素含有層を窒化層に改質する工程と、処理容器内に酸素を含むガスを活性化して供給することで、窒化層を酸化層または酸窒化層に改質する工程と、を1サイクルとして、このサイクルを少なくとも1回以上行う。

(もっと読む)

電子デバイス材料の製造方法

【課題】極めて薄い膜厚を有する絶縁膜としてSiO2膜およびSiON膜を用い、電極としてポリシリコン、アモルファスシリコン、SiGeを用いた良好な電気特性を有する電子デバイス(例えば高性能MOS型半導体装置)構造の製造方法を提供する。

【解決手段】酸素、および希ガスを含む処理ガスの存在下で、ウエハW上に平面アンテナ部材SPAを介してマイクロ波を照射することにより、酸素と希ガスとを含むプラズマ(ないし窒素と希ガスとを含むプラズマ、または窒素と希ガスと水素を含むプラズマ)を形成する。このプラズマを用いて前記ウエハ表面に酸化膜2(ないし酸窒化膜2a)を形成し、必要に応じてポリシリコン等の電極13を形成して電子デバイス構造を形成する。

(もっと読む)

半導体デバイスのメタライゼーションシステムにおけるキャップ層のCMP及びエッチング停止層としての使用

【解決手段】

進歩的なメタライゼーションシステムを製造する間、敏感な誘電体材質上に形成される誘電体キャップ層が、過剰な金属を除去するためのCMPプロセスの間に部分的に維持されてよく、それにより、CMPプロセスの間に誘電体キャップ材質を実質的に完全に消耗する場合に従来の手法で必要であろうような専用のエッチング停止層を堆積させる必要性が回避され得る。従って、低減されたプロセスの複雑性及び/又は高い柔軟性が低k誘電体材質の高い完全性との組み合わせにおいて達成され得る。

(もっと読む)

表示装置及び電子デバイス

【課題】反射型表示装置の製造工程を大幅に簡略化する。

【解決手段】薄膜トランジスタと、薄膜トランジスタの上方に配置された絶縁層及び画素電極を有し、画素電極は、薄膜トランジスタに電気的に接続され、表面に凹凸を有し、かつ、反射機能を有し、絶縁層は、酸化珪素、窒化珪素、酸化窒化珪素及び有機性樹脂から選ばれた材料を積層した構造を有し、絶縁層の少なくとも一層はカーボン系材料及び顔料の少なくともいずれか一を含む遮光膜である表示装置とする。

(もっと読む)

フラッシュメモリ素子のトンネル絶縁膜形成方法

【課題】800℃以上の高温のプラズマ窒化処理工程を含んでトンネル絶縁膜を形成することにより、トラップサイト(trap site)を減少させ、シリコン酸化窒化膜(SiON)の形成によってホウ素浸透を抑制して漏れ電流および絶縁破壊電圧特性などを改善することが可能なフラッシュメモリ素子のトンネル絶縁膜形成方法の提供。

【解決手段】半導体基板上に酸化膜を形成する段階と、800〜900℃のプラズマ窒化処理工程によって前記酸化膜の表面に窒素含有絶縁膜を形成する段階と、前記半導体基板と前記窒素含有絶縁膜の形成された前記酸化膜との界面に窒素蓄積層を形成する段階とを含む、フラッシュメモリ素子のトンネル絶縁膜形成方法を提供する。

(もっと読む)

101 - 120 / 306

[ Back to top ]