Fターム[5F058BD15]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 少なくとも一層がシリコン酸化窒化物 (338)

Fターム[5F058BD15]の下位に属するFターム

添加物含有 (32)

Fターム[5F058BD15]に分類される特許

41 - 60 / 306

有機アミノシラン前駆体及びこれを含む膜の堆積方法

【課題】酸化ケイ素又は窒化ケイ素をCVDやALDなどのプロセスにより、低温で堆積できる前駆体を提供する。

【解決手段】誘電体膜を形成するための前駆体及び方法である。1つの態様では、次の式Iを有するケイ素前駆体が与えられる。 (もっと読む)

(もっと読む)

半導体装置

【課題】良好な電気特性を有する半導体装置を提供することである。

【解決手段】チャネル領域を形成する酸化物半導体層と接するゲート絶縁層に、水素濃度が6×1020atoms/cm3未満であり、且つフッ素濃度が1×1020atoms/cm3以上であるゲート絶縁層を用いることで、ゲート絶縁層から放出される水素量が低減され、酸化物半導体層に水素が拡散することを防ぐことができる。さらに、フッ素により酸化物半導体層内に存在する水素を脱離させ、酸化物半導体層内の水素濃度を低減させることができるため、良好な電気特性を有する半導体装置を提供することできる。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

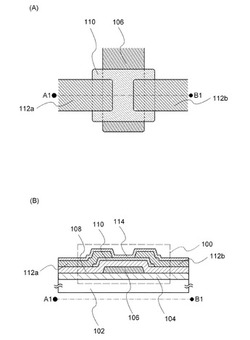

成膜方法及び薄膜トランジスタの作製方法

【課題】3層以上の膜を成膜するに際して、第1の膜の成分が第3の膜に含まれることを防ぐ成膜方法を提供する。

【解決手段】上部電極104と下部電極102が設けられた成膜装置100により3層以上の膜を成膜する多層膜の成膜に際して、下部電極102上に基板110を配して第1の膜112を成膜し、前記第1の膜112の形成時よりも上部電極104と前記基板110の間の距離を長くし、前記第1の膜112上に第2の膜114を成膜し、前記第2の膜114の形成時よりも前記上部電極104と前記基板110の間の前記距離を短くし、前記第2の膜114上に第3の膜116を成膜する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

シリコンオキシナイトライド膜の形成方法およびそれにより製造されたシリコンオキシナイトライド膜付き基板

【課題】エネルギーコストを抑制できるシリコンオキシナイトライド膜の製造方法とそれにより製造されたシリコンオキシナイトライド膜付き基板の提供。

【解決手段】基板表面にポリシラザン化合物を含む被膜形成用組成物を塗布して塗膜を形成させ、前記塗膜に含まれる過剰の溶媒を除去し、溶媒除去後の塗膜を150℃未満の温度条件下で紫外線を照射することを含むシリコンオキシナイトライド膜の形成方法。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】基板の表面粗度によらず膜表面が平坦であり、信頼性が高く、製造コストを低減させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】絶縁基板10上に、ゲート電極11、ゲート絶縁層12、半導体活性層13、ソース電極14、及びドレイン電極15を順次形成するボトムゲート型薄膜トランジスタ1の製造方法である。ゲート絶縁層12は、絶縁基板10上に下部層12aと該下部層12a上に積層された少なくとも一層以上の上部層12bとがこの順で形成されてなり、下部層12aは真空紫外光CVD法により形成される。

(もっと読む)

プラズマ窒化処理方法

【課題】 同一の処理容器内でプラズマ窒化処理の処理条件を変化させた場合でもパーティクルの発生を防止できるプラズマ窒化処理方法を提供する。

【解決手段】 第1のプラズマ窒化処理が終了し、処理容器1から1枚のウエハWを搬出した後に、処理容器1内から酸素を排出させるプラズマシーズニングを行う。プラズマシーズニングでは、ウエハWを配置せず又はダミー基板を配置し、処理容器1内に窒素ガス/希ガスの流量比0.2以上1以下で希ガスと窒素ガスの処理ガスを導入し、第2の条件で第2の窒素プラズマを生成させ、処理容器1内の酸素を除去する。

(もっと読む)

結晶性太陽電池上の機能的および光学的グレーデッドARC層のための多層SiN

太陽電池の製造方法

原子層堆積方法および原子層堆積装置

【課題】原子層堆積方法および原子層堆積装置は、従来のような防湿性を維持しつつ、内部応力の小さな薄膜を形成する。

【解決手段】基板に薄膜を形成するとき、基板が配置された、減圧した成膜空間内に、原料ガスを一定期間供給する。この後、原料ガスの前記成膜空間への供給後、原料ガスの成分を吸着した基板に向けて、前記成膜空間内に反応ガスを供給し、プラズマ生成素子を用いて反応ガスを活性化させることにより、基板に吸着された原料ガスの成分と反応ガスの成分を反応させて、基板に所定の薄膜を形成させる。上記原料ガスの供給と反応ガスの供給を繰り返し行うことにより、所定の厚さの薄膜を基板に形成する。このとき、上記原料ガスの供給と反応ガスの供給の繰り返し回数が増えるに従って、段階的にあるいは連続的にプラズマ生成素子への供給電力を増加させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の広幅の配線におけるディッシングの抑制と、抵抗の抑制と、を両立させる。

【解決手段】半導体装置100は、半導体基板1と、半導体基板1上に形成された配線層絶縁膜9と、を有している。配線層絶縁膜9には、第1配線用配線溝11と、第1配線用配線溝11よりも広幅の第2配線用配線溝12と、が形成されている。第1配線用配線溝11内には第1配線21が、第2配線用配線溝12内には第2配線22が、それぞれ形成されている。第2配線用配線溝12の底面の少なくとも一部分は、絶縁膜(例えば、絶縁膜4及びエッチングストッパー膜5)によって、第2配線用配線溝12の上端に達しない高さで第1配線用配線溝11の底面よりもかさ上げされた、かさ上げ部15となっている。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】シリコン含有膜の露出面に形成する酸化膜中や、既に基板上に成膜済みの誘電膜中等に水素が混入することを抑制させ、半導体装置の性能を向上させる。

【解決手段】 水素ガスより分子サイズの大きい還元性ガスを処理室内に供給し、処理室内に供給された還元性ガスをプラズマ放電して生成した還元性ガスプラズマを基板の表面に供給する還元工程と、酸化性ガスを処理室内に供給し、処理室内に供給された酸化性ガスをプラズマ放電して生成した酸化性ガスプラズマを基板の表面に供給する酸化工程と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧の異なるトランジスタが同一半導体基板上に混載されている場合においても、それらのトランジスタの性能が向上するようにストレスライナ膜を構成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に混載された低耐圧トランジスタおよび高耐圧トランジスタ上に形成するストレスライナ膜11、12は、互いに膜質を異ならせることができる。ここで、ストレスライナ膜11は、低耐圧トランジスタの性能が効果的に改善され、高耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。また、ストレスライナ膜11は、高耐圧トランジスタの性能が効果的に改善され、低耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。

(もっと読む)

薄膜トランジスタ基板

【課題】透明導電膜を配線電極とした場合における段差部での絶縁不良や断線を解決し、酸化物半導体膜が持つ高い移動度を生かした高速応答ディスプレイや周辺回路等を実現することができる、薄膜トランジスタ基板を提供する。

【解決手段】基材1と、基材1上に設けられた透明導電膜からなるゲート電極2と、ゲート電極2を覆って平坦化するように設けられたゲート絶縁膜3と、ゲート電極2の上方であって前記ゲート絶縁膜3上に設けられた酸化物半導体膜4と、酸化物半導体膜4上に該酸化物半導体膜4の中央部を開けて離間して設けられたソース電極5s及びドレイン電極5dとを有し、前記ゲート絶縁膜3が、塗布型材料からなる絶縁性の平坦化膜3aを有するように構成した。ゲート絶縁膜3は、平坦化膜3aからなるように構成してもよいし、平坦化膜3aと平坦化膜3a上に設けられた絶縁膜3bとからなるように構成してもよい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SiCを用いた、低オン抵抗、かつ信頼性にも優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】炭化珪素層と、炭化珪素層上に形成され、珪素、酸素、窒素を主成分とし、窒素の最低濃度が1×1020atoms/cm3以上のゲート絶縁膜と、ゲート絶縁膜上に形成されるゲート電極を有することを特徴とする半導体装置。炭化珪素層の(000−1)面または(11−20)面上に酸化物膜または酸窒化物膜を形成する工程と、酸化物膜または酸窒化物膜の形成後に、アンモニアガスを含む雰囲気中で熱処理しゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】高速処理が可能で、かつ電荷保持特性の高いチャージトラップ型フラッシュメモリを得ることができる半導体装置の製造方法を提供する。

【解決手段】基板100の表面を酸化してシリコン酸化膜140を形成するシリコン酸化膜形成工程と、プラズマ状態の窒素含有ガスをシリコン酸化膜140に供給してシリコン酸化膜140の表面近傍に窒素ピーク濃度が20原子%以上60原子%以下の窒化層141を形成する窒化層形成工程と、窒化層141が形成されたシリコン酸化膜140上に電荷保持膜150を形成する電荷保持膜形成工程と、電荷保持膜150上に、絶縁膜160と電極膜170を形成する電極膜形成工程とを有する。

(もっと読む)

成膜方法および半導体装置

【課題】スパッタ法により、酸化物半導体膜上に薄膜を成膜する際に、酸化物半導体膜のプラズマダメージを膜面内均一性良く抑制して成膜する。

【解決手段】基板B上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜1上に、基板BとターゲットTとを対向させて、プラズマを用いるスパッタ法によりターゲットTの構成元素を含む薄膜2を形成する成膜方法において、薄膜2の成膜時のプラズマ中のプラズマ電位Vs(V)と、基板Bの基板電位Vsub(V)との電位差を0V超20V以下とする。

(もっと読む)

半導体装置の製造方法

【目的】より簡易な手法で、所定の層表面に反射防止構造を形成する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、高周波電力を印加したプラズマ雰囲気中で、基板上にシリコン(Si)含有絶縁膜を形成する工程(S102)と、前記Si含有絶縁膜を形成する際に用いたガスを継続して流し続けながら前記高周波電力の出力を弱めることで、前記Si含有絶縁膜上にSiを主成分とする複数の粒子を堆積させる工程(S104)と、前記複数の粒子をマスクとして、前記Si含有絶縁膜をエッチングする工程(S106)と、を備えたことを特徴とする。

(もっと読む)

41 - 60 / 306

[ Back to top ]