Fターム[5F058BD15]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 少なくとも一層がシリコン酸化窒化物 (338)

Fターム[5F058BD15]の下位に属するFターム

添加物含有 (32)

Fターム[5F058BD15]に分類される特許

81 - 100 / 306

薄膜トランジスタの製造方法

【課題】基板との密着性が高いゲート絶縁層を設けることにより信頼性の高い電界効果トランジスタを提供することを目的とする。

【解決手段】絶縁基板上に少なくともゲート電極、ゲート絶縁層、酸化物を含む半導体層、ソース電極およびドレイン電極が設けられ、前記ゲート絶縁層は前記絶縁基板と接触する下部ゲート絶縁層と、該下部ゲート絶縁層の上に形成された一層以上の上部ゲート絶縁層を積層してなる薄膜トランジスタの製造方法であって、前記下部ゲート絶縁層がイオンビームスパッタ法により成膜されることを特徴とする薄膜トランジスタの製造方法としたものである。

(もっと読む)

誘電体膜、誘電体膜を用いた半導体装置の製造方法及び半導体製造装置

【課題】高誘電率を有する誘電体膜の製造方法を提供する。

【解決手段】薄いシリコン酸化膜を形成したSi基板上に、HfN/Hf積層膜を形成し、アニール処理によりHf、Si、O、Nの混合物からなる金属酸窒化物とする誘電体膜の製造する。(1)EOTの低減が可能であり、(2)リーク電流がJg=1.0E−1A/cm2以下に低減され、(3)固定電荷の発生によるヒステリシスが抑制され、(4)700℃以上の熱処理を行ってもEOTの増加が無く耐熱性に優れる。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】オフ電流が低く、オン電流及び電界効果移動度が高い薄膜トランジスタを提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁層として窒化シリコン層と当該窒化シリコン層が酸化された酸化シリコン層を積層して形成し、該ゲート絶縁層の酸化シリコン層との界面直上から結晶成長した微結晶半導体層を形成する。ゲート絶縁層の直上から結晶成長するため、結晶性の高いオン電流及び電界効果移動度が高い薄膜トランジスタとすることができる。また、バッファ層を設けてオフ電流を低減させる。

(もっと読む)

半導体装置の製造方法

【課題】高い比誘電率が確保されており且つ熱的に安定なゲート絶縁膜を用いた半導体装置を実現できるようにする。

【解決手段】基板20上に、水素を含むHfO2 膜22Aを形成した後、HfO2 膜22Aに対して熱処理を行なうことにより、基板20側からシリコンをHfO2 膜22A中に拡散させてシリコン含有HfO2 膜22を形成する。その後、シリコン含有HfO2 膜22の上にゲート電極となるポリシリコン膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】同一基板上に複数のゲート絶縁膜を有する半導体装置において、例えばコア部におけるHPトランジスタの高速性の確保と、例えばI/Oトランジスタ及びLPトランジスタのゲート耐圧の向上やゲートリーク電流の低減とを両立する。

【解決手段】半導体装置は、半導体基板11上に形成された複数のゲート絶縁膜を備えており、複数のゲート絶縁膜のうち、HPトランジスタ形成領域1Cにおける膜厚が最も薄いゲート絶縁膜は、シリコン酸化膜20よりなり、I/Oトランジスタ形成領域1A及びLPトランジスタ形成領域1Bにおける残りのゲート絶縁膜は、シリコン酸窒化膜16、17よりなる。

(もっと読む)

半導体装置の製造方法

【課題】

CMOSトランジスタの一方のキャップ誘電体膜に対するアニール条件を、CMOSトランジスタの他方のキャップ誘電体膜に対するアニール条件とは独立に設定する。

【解決手段】

シリコン基板に、n型ウェルおよびp型ウェルを形成し、シリコン基板上方にHfO等の第1の高誘電率絶縁膜、AlO等の第1のキャップ誘電体膜を積層し、p型ウェル上方から、少なくとも第1のキャップ誘電体膜を除去し、第1の温度で第1のアニールを行なって、第1のキャップ誘電体膜の構成元素Al等をn型ウェル上方の第1の高誘電率絶縁膜中へ拡散させ、p型ウェルおよびn型ウェル上方にHfO等の第2の高誘電率絶縁膜、LaO等の第2のキャップ誘電体膜を積層し、n型ウェル上方の第2のキャップ誘電体膜を除去し、第1の温度より低い第2の温度で、第2のアニールを行なって、第2のキャップ誘電体膜の構成元素La等をp型ウェル上方の第2の高誘電率絶縁膜中へ拡散させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】PチャネルMOSFETの閾値電圧の上昇を防ぎつつ、NチャネルMOSFETの閾値電圧の制御を確実に行う。

【解決手段】半導体装置1は、半導体基板10にゲート絶縁膜を形成し、NチャネルMOSFET形成領域に形成されたゲート絶縁膜に開口部を有し、かつゲート絶縁膜を覆うマスクを形成し、NチャネルMOSFET形成領域に位置するゲート絶縁膜上、およびPチャネルMOSFET形成領域に形成されたマスク上に第1の金属層を形成し、NチャネルMOSFET形成領域に形成されたゲート絶縁膜中に第1の金属層を形成する金属を熱処理により拡散させること、により製造される。

(もっと読む)

半導体装置の製造方法

【課題】配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑える半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上のSiOC膜11表面に配線12を形成する工程と、配線12が表面に形成されたSiOC膜11を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝してSiOC膜11表面に緻密層14を形成する工程と、緻密層14が形成された後に、配線12の表面に形成された酸化膜13を除去する工程と、酸化膜13が除去された配線12、及び緻密層14上に絶縁膜としての拡散防止膜15を形成する工程と、を含み、酸化膜13を除去する工程から拡散防止膜15を形成する工程までが、大気に暴露されることなく行われる。

(もっと読む)

半導体装置の製造方法、基板処理方法および基板処理装置

【課題】 膜中の炭素、水素、窒素、塩素等の不純物濃度が極めて低い絶縁膜を低温で形成する。

【解決手段】 基板を収容した処理容器内に所定元素を含む原料ガスを供給することで、基板上に所定元素含有層を形成する工程と、処理容器内に窒素を含むガスを活性化して供給することで、所定元素含有層を窒化層に変化させる工程と、処理容器内に原料ガスを供給することで、窒化層上に所定元素含有層を形成する工程と、処理容器内に酸素を含むガスを活性化して供給することで、窒化層上に形成された所定元素含有層および窒化層を、酸化層また酸窒化層に変化させる工程と、を1サイクルとして、このサイクルを複数回繰り返すことで、基板上に所定膜厚の酸化膜または酸窒化膜を形成する工程を有する。

(もっと読む)

MOSトランジスタ

【課題】MOSトランジスタを作成する。

【解決手段】MOSトランジスタであって、ゲート電極と、ゲート電極下地の頂部表面を有するチャンネル領域と、ゲート電極とチャンネル領域の頂部表面の間に挿入された誘電体スタックとを含み、前記誘電体スタックが、少なくとも高―k材料を含む高―k誘電体層と、少なくともケイ素および窒素を含む誘電体層と、前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含み、該中間層が、少なくとも前記高―k材料、ケイ素および窒素を含み、前記ゲート電極がポリシリコンまたはポリシリコンゲルマニウムから作製される。

(もっと読む)

プラズマ処理方法

【課題】被処理体の加熱をともなうプラズマ処理を行う際に、処理前のプリヒートを短時間で行うことができるプラズマ処理方法を提供すること。

【解決手段】チャンバー内にウエハを配置し、ウエハを加熱しながらウエハにプラズマ処理を施すにあたり、処理に先立ってウエハにプラズマを照射しつつウエハにプリヒート(予備加熱)を施し、プリヒート後にチャンバー内に処理ガスを供給してウエハに対してプラズマ処理を行う。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極が微細化されても電流コラプスを抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】表面保護膜10を形成する際に、化合物半導体積層構造上に第1の絶縁膜10aを形成し、第1の絶縁膜10aの表面に、酸素原子又は窒素原子の少なくとも一方を第1の絶縁膜10aよりも多く含む第2の絶縁膜10bを形成し、第2の絶縁膜10bの上方に、第1の絶縁膜10aよりもSi−H結合を少なく含み、第1の絶縁膜10aよりも高い絶縁性を示す第3の絶縁膜10cを形成する。

(もっと読む)

半導体装置の製造方法

【課題】high-kゲート誘電体のパターニングが不要な半導体装置の製造方法を提供する。

【解決手段】第1の領域が第1の厚さに、第2の領域が第1の膜さよりも薄い第2の厚さになるようにゲート誘電体層204を半導体基板202上に形成し、ゲート誘電体層204上にhigh-kの原子の層212を形成し、熱処理を行って、第1の領域に第1の厚さ及び第1の組成のうち少なくとも一方を有するhigh-kゲート誘電体層216を形成し、第2の領域に第1の厚さよりも薄い第2の厚さ及び第2の組成のうち少なくとも一方を有するhigh-kゲート誘電体層218を形成する。

(もっと読む)

誘電体膜形成方法

【課題】ケイ素を含む誘電体膜を形成する方法を提供すること。

【解決手段】ここに記載されるのは、低いウェットエッチ耐性、6.0以下の誘電率、及び/又は高温急速熱アニールプロセス耐性、といった特性のうちの少なくとも1つを示す、酸化ケイ素、酸炭化ケイ素、炭化ケイ素及びこれらの組み合わせなどの、とは言えこれらに限定はされない、ケイ素を含む誘電体膜を形成する方法である。同様にここに開示されるのは、例えば半導体ウェーハなどの処理すべき対象物上に誘電体膜又は被覆を形成するための方法である。

(もっと読む)

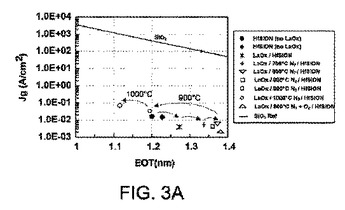

低減された等価酸化膜厚を有する高誘電率ゲートスタックの形成方法

低減された均等酸化物厚さ(EOT)を持つhigh−kゲートスタックを形成する方法を提供し、該方法は:シリコン含有基板を準備し;前記シリコン含有基板上に境界層を形成し、前記境界層が第一の等価酸化物厚さを有し;前記境界層上に第一のhigh−k膜を堆積し;前記第一のhigh−k膜及び前記境界層を、前記第一の等価酸化物厚さと等しいかそれより小さい第二の等価酸化物厚さを持つ変性境界層を形成する温度で熱処理し;及び前記変性境界層上に第二のhigh−k膜を堆積する方法である。ひとつの実施態様によると、前記第一のhigh−k膜がランタン酸化物を含み、前記第二のhigh−k膜がハフニウムシリケートを含む。  (もっと読む)

(もっと読む)

半導体素子及びその製造方法

【課題】 加熱処理により、ランタンやアルミニウムがhigh−k材料とシリコン基板との間の酸化シリコン膜まで拡散する。ランタンやアルミニウムの拡散が、チャネル移動度の低下や素子の信頼性の低下の原因になる。

【解決手段】 半導体基板の一部の領域上に、SiとOとを含む絶縁層が形成されている。絶縁層の上に、ハフニウムシリケートを含む下側高誘電率膜が形成されている。下側高誘電率膜の上に、ハフニウム酸化物、またはHfとSiとの合計の原子数に対するHfの原子数の比が、下側高誘電率膜のそれよりも大きいハフニウムシリケートを含む上側高誘電率膜が形成されている。上側高誘電率膜の上にゲート電極が形成されている。ゲート電極の両側にソース及びドレインが配置されている。

(もっと読む)

多層膜の形成方法及び表示パネルの製造方法

【課題】予め定めた形状にパターニングされた導電層の上下に配置されている絶縁層のそれぞれにコンタクトホールを形成し、これらコンタクトホールを介して互いに異なる層として形成された2つの導電層を互いに電気的に接続する場合であっても、導電不良が生じ難い多層膜の形成方法及び表示パネルの製造方法を提供する。

【解決手段】基板2上に成膜された第1導電層40上に第1絶縁層20を成膜し、前記第1絶縁層20上に第2導電層41を成膜し、前記成膜した第2導電層41をパターニングし、パターニングされた前記第2導電層41を覆うように前記基板2上に第2絶縁層25を成膜し、前記第2絶縁層25上に該第2絶縁層25よりもエッチング速度が速い第3絶縁層26を成膜し、前記第1絶縁層20、前記第2絶縁層25及び前記第3絶縁層26に対して前記第1導電層40の少なくとも一部を露出させるコンタクトホールを一括形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】シリコン基板の表面温度を低下させつつ、リーク電流が少ないゲート絶縁膜を形成する。

【解決手段】 上記課題を解決するために、酸素原子及び窒素原子を含むガスを処理室内に供給し、酸素原子及び窒素原子を含むガスをプラズマによって活性化し、シリコン基板を前記プラズマにより処理を行い窒素が含有された二酸化シリコン膜を形成する半導体装置の製造方法を提供する。

(もっと読む)

81 - 100 / 306

[ Back to top ]