Fターム[5F064CC12]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | トランジスタ (1,639) | FET (1,516) | MOS−FET(MISも含む) (1,456) | CMOS (629)

Fターム[5F064CC12]に分類される特許

41 - 60 / 629

半導体装置

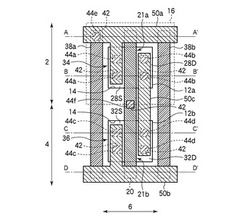

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、半導体基板の上方に形成された半導体素子と、半導体素子の上方に形成された第1絶縁膜と、第1絶縁膜上に形成されたアルミニウム(Al)を含有する第1導電性膜よりなるヒューズ素子Fと、を有する。さらに、第1絶縁膜上に形成され、第1導電性膜よりなる第1配線と、第1配線上に形成された第2絶縁膜と、を有し、ヒューズ素子Fのプログラム領域は、第2絶縁膜に設けられた開口部OA1から露出している。また、ヒューズ素子Fのプログラム期間およびヒューズ素子にプログラムされたデータの読み出し期間以外の期間において、ヒューズ素子Fの両端を接地電位に維持する。例えば、ヒューズ素子Fの一端は、接地電位に接続され、他端は、スイッチング素子を介して接地電位に接続されている。

(もっと読む)

ヒューズ回路

【課題】ヒューズ回路の2つの出力側にそれぞれ所期の論理値に設定された論理信号出力する。

【解決手段】ヒューズ回路10は、電圧源VDDと、第1主電極、第2主電極、及び制御電極を有する第1及び第2のトランジスタQ11,Q12と、電圧源と第1のトランジスタのソースSとの間に直列に配置される第1の電気ヒューズRf1と、電圧源と第2のトランジスタのソースとの間に直列に配置される第2の電気ヒューズRf2を備える。さらに、第1,第2の電力供給回路Q13,Q14と、第1及び第2のトランジスタのドレインD側から論理値出力を取り出す第1及び第2の出力X,Yを備える。

(もっと読む)

半導体装置

【課題】複数の電圧レベルの電源電圧が供給される入出力バッファ回路に対して、従来よりも少ない電源配線スペースで十分な電源供給を可能にする。

【解決手段】半導体装置3において、入出力バッファ回路BFは電圧レベルの変換を行なう。第1の電源配線HVLは、入出力バッファ回路BFの第1の回路部分HCと接続され、第1の回路部分HCに第1の電源電圧VCC1を供給する。第2の電源配線LVLは、入出力バッファ回路BFの第2の回路部分LCと接続され、第2の回路部分LCに第2の電源電圧VCC2を供給する。複数のスイッチ部SWは、第3の電源配線SVLに沿った複数箇所にそれぞれ設けられる。複数のスイッチ部SWの各々は、内部回路10から出力された制御信号に応じて、第1および第2の電源配線HVL,LVLのうち選択された一方の電源配線と第3の電源配線SVLとを接続する。

(もっと読む)

集積回路デバイス

【課題】プロセス寸法の縮小に伴う光相互作用の予測品質の低下を抑止する。

【解決手段】ゲートレベル仮想格子の、連続的に隣接して配置された少なくとも3本の仮想ラインのそれぞれは、その上に定義された少なくとも1つの線形導電体形状を有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第1の仮想ラインは、その上に定義され、第1の終端−終端間スペーシングで分離された2つの線形導電体セグメントを有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第2の仮想ラインは、その上に定義され、第2の終端−終端間スペーシングで分離された他の2つの線形導電体セグメントを有し、第1の仮想ラインに沿って測定された第1の終端−終端間スペーシングの寸法は、第2の仮想ラインに沿って測定された第2の終端−終端間スペーシングの寸法に等しく、ゲートレベル仮想格子の仮想ラインは、いかなる導電体形状によっても占有されない。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

半導体装置

【課題】電源分離領域内の配線密度を低下させる。

【解決手段】動作モードに応じて電源電圧が供給される電源線VVDDと、常に電源電圧が供給される電源線VDDと、通常モードで電源線VVDDを電源線VDDに接続するか、またはスリープモードで電源線VVDDを接地電位とするか、を切り替える電源切替回路(104、111、110が相当)と、電源線VVDDから電源供給されスリープモードでは動作を停止する第1回路ブロック101と、電源線VDDからの電源供給によって常に動作可能とする第2回路ブロック103と、電源線VVDDの電位が接地電位近傍にあるか否かにそれぞれ応じて、第2回路ブロック103の入力端をハイレベルにするか、第1回路ブロック101の出力信号を第2回路ブロック103に伝達可能とするか、を制御する入力制御回路(114、118が相当)と、を備える。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

半導体装置

【課題】チップ面積を拡大することなく信頼性の高い配線レイアウトを実現する。

【解決手段】信号線S1〜S3と電源線VDD1,VSS1がY方向に延在する下層配線層と、信号線S4〜S6と電源線VDD2,VSS2がX方向に延在する上層配線層と、対応する信号線が重なり合うオーバーラップ領域OL1に設けられたビア導体VE1と、対応する電源線が重なり合うオーバーラップ領域OL2,OL3に設けられたビア導体VE2,VE3とを備える。領域OL1のX方向における幅は、領域OL2,OL3のX方向における幅よりも広く、これにより、領域OL1には複数のビア導体VE1a,VE1bが設けられる。また、電源線VDD1,VSS1は、領域OL1との干渉を避けるようY方向に分断されている。複数の下層配線は、一つのビアを含むミニマムピッチで2つのビアを配置している。

(もっと読む)

回路レイアウト設計システム、リーク対策セル、回路レイアウト設計方法及びプログラム

【課題】正規回路のタイミングを変えずに、未使用セル群の全てのセルのダイナミック電流及びチャンネルリーク電流を削減することができる回路レイアウト設計システムを提供する。

【解決手段】本発明の回路レイアウト設計システムは、レイアウトデータから、出力端子がオープン状態の未使用インバーターセルを検出する出力オープンセル検出部と、オープンセル検出部が検出した未使用インバーターセルの出力オープンセル情報を、出力オープンセル情報ファイルに格納する出力オープンセル情報抽出部と、レイアウトデータから、未使用インバーターセルを削除する出力オープンセル削除部と、出力オープンセル情報のセル名を、リーク対策セルに対応するセル名に変換した置換情報ファイルに格納するセル名変換部と、置換情報ファイルを参照して、レイアウトデータの未使用インバーターセルをリーク対策セルに置換する出力オープンセル置換部とを備える。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

未知の半導体装置の機能の非破壊的な決定

【課題】外部放射線に対して応答する接合を分析することを通して機能を推測することによる、集積回路の非破壊的なリバースエンジニアリングのためのシステム及び技術を提供する。

【解決手段】少なくとも1つの電源と電気的に導通している複数の半導体接合を含む半導体装置の機能を決定するための以下を含む方法。

・半導体装置の表面を照射すること;

・照射に応答する複数の半導体接合のうち少なくとも幾つかのレイアウトを決定すること;

・決定されたレイアウト内で、複数の半導体接合の少なくとも幾つかのグルーピングを同定し、各ブルーピングはそれぞれの機能セルを表すこと;

・複数の外部アクセス可能な接点のうち少なくとも1つへの刺激を変化させること;及び

・前記変化した刺激に応答して複数の相互接続された機能セルの1つ以上の接続を推測すること。

(もっと読む)

半導体集積回路のレイアウト検証装置及びレイアウト検証方法

【課題】設計段階でインプラチェックを自動的に行う。

【解決手段】実施形態に係わるレイアウト検証装置は、半導体集積回路のレイアウトから抽出した素子が回路図と一致しているか否かを検証する第1の検証部60と、半導体集積回路のレイアウトが仕様情報から抽出したデザインルールに違反しているか否かを検証する第2の検証部70とを備える。第1及び第2の検証部60,70のうちの1つ内のフィルター処理部は、被検証素子と、被検証素子を形成するために必要なマスクデータと、被検証素子を形成するために不要なマスクデータの反転データとのアンドロジックを実行し、被検証素子に対してインプラが適切に行われているか否かを判断する。

(もっと読む)

電圧降下解析装置、および、電圧降下解析方法

【課題】電圧降下解析の実行時間を短縮することが可能な電圧降下解析装置を提供する。

【解決手段】電圧降下解析装置の電流解析部は、素子に流れる電流を解析し、素子に流れる電流の電流情報を出力する。電圧降下解析部は、素子の接続、素子の配置、および素子に接続された電源配線の情報を含む回路配置情報と、電流情報と、に基づいて、素子の電圧降下を解析し、素子の電圧降下の電圧降下情報を出力する。コーナ選択部は、複数のコーナ情報を含むコーナ情報リストから素子のコーナ情報を選択する。電圧降下補正部は、電圧降下情報と、選択されたコーナ情報と、コーナ情報と電圧降下情報の補正量との関係を規定する電圧降下補正情報と、に基づいて、電圧降下情報を補正した補正後電圧降下情報を出力する。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

半導体装置

【課題】ヒューズの切断状態または非切断状態を正しく判定する半導体装置を提供する。

【解決手段】半導体装置は、ヒューズと当該ヒューズに直列に接続された所定抵抗素子とを含むヒューズ抵抗回路と、ヒューズが非切断状態であるときのヒューズ抵抗回路の抵抗値よりも所定の抵抗値だけ大きな抵抗値を有する特定抵抗素子を含む基準抵抗回路と、ヒューズ抵抗回路の抵抗値が、基準抵抗回路の抵抗値よりも大きい場合には、ヒューズの切断を示す切断信号を出力し、ヒューズ抵抗回路の抵抗値が、基準抵抗回路の抵抗値よりも小さい場合には、ヒューズの非切断を示す非切断信号を出力する判定回路と、を含む。

(もっと読む)

電力最適化のための粒状チャネル幅

【課題】集積回路の設計において電力を最適化する為に、コンピュータによって読取可能であり、コンピュータによって用いられる1つ以上のセルを有するセルライブラリを記録する記憶媒体の提供。

【解決手段】1つ以上のセルは、フィジカルディメンションパラメータとチャネル幅パラメータとを有する。フィジカルディメンションパラメータは、1つ以上のセルのフットプリントである。チャネル幅パラメータは、最小ドライバサイズと最大ドライバサイズとを有する。チャネル幅パラメータは、1つ以上の電力基準に基づいて集積回路の設計フロー中に、フットプリントを変更せずに、ツールが最大ドライバサイズと最小ドライバサイズとの間でチャネル幅を変更する範囲を定義する。

(もっと読む)

41 - 60 / 629

[ Back to top ]