Fターム[5F092AB01]の内容

Fターム[5F092AB01]に分類される特許

61 - 80 / 645

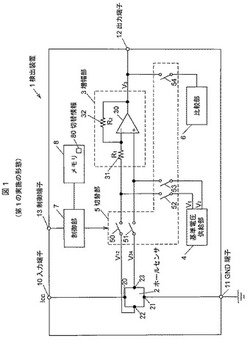

検出装置および電流センサ

【課題】増幅率が予め定められた増幅率であるかを判定することができる検出装置および電流センサを提供する。

【解決手段】実施の形態に係る検出装置1は、主に、検出対象の変化を検出して検出信号を出力するホールセンサ2と、ホールセンサ2から出力された検出信号を増幅して第1の増幅信号を出力する増幅部3と、増幅部3に入力して第2の増幅信号として出力される基準電圧を増幅部3に供給する基準電圧供給部4と、入力する制御信号に基づいてホールセンサ2と増幅部3との接続、または増幅部3と基準電圧供給部4との接続を切り替える切替部5と、増幅部3に予め定められた増幅率と、第2の増幅信号から得られる増幅率と、を比較した結果を比較信号として出力する比較部6と、を備える。

(もっと読む)

3軸センサ・チップパッケージに関するシステムと方法

【課題】3軸センサ・チップパッケージためのシステムと方法を提供する。

【解決手段】センサパッケージは、ベース105と、第1のセンサダイ110が、第1のアクティブセンサ回路112および、第1のアクティブセンサ回路に電気的に結合された複数の金属パッド114とを備え、ベースに取り付けられた第2のセンサダイ120が、第1の表面128の上に配置された第2のアクティブセンサ回路122と、第2の表面の上に配置された第2のアクティブセンサ回路に電気的に結合された第2の複数の金属パッド122とを備え、第2のアクティブセンサ回路は、第1のアクティブセンサ回路に対して直交に方位付けされ、ベースに垂直であるように、第2のセンサダイが配置される。第2の表面は、第1の表面に隣接し、第1の表面の面に対して角度がつけられている。

(もっと読む)

電子機器

【課題】一対の部材間において非接触で信号を送受信でき、しかも小型化可能な電子機器を提供すること。

【解決手段】本発明の電子機器(1)は、ヒンジ部(13)を介して相対的に回動可能に連結された本体部(11)及び表示部(12)を備えた電子機器(1)であって、本体部(11)に設けられ表示部(12)に向けた信号を出力する信号回路(16)と、ヒンジ部(13)に設けられ信号回路(16)に電気的に接続される少なくとも1つの導電路(20)と、導電路(20)に対向して表示部(12)に配設され信号回路(16)から出力され導電路(20)に印加された信号からの誘導磁界により出力信号を出力する少なくとも一つのGMR素子(18)と、を具備することを特徴とする。

(もっと読む)

磁気センサ及び回転角度検出装置

【課題】 検出感度の異方性を抑えるため、磁気的等方性を有し且つ小型である磁気センサを提供する。

【解決手段】 本発明の磁気センサは、非磁性の中間層を介して2つの強磁性膜が積層されたスピンバルブ型の磁気抵抗効果素子を用いた磁気センサにおいて、前記磁気抵抗効果素子の形状は複数のリングが連なった形状であり、各々のリングが電気的に接続されている状態で通電され、前記磁気抵抗効果素子の電気抵抗が外部磁場に対して変化することを特徴とする。前記検出素子が少なくとも2つ含まれるブリッジ回路で回転角度検出装置を構成する。

(もっと読む)

電流センサおよび電流センサの製造方法

【課題】製造上の手間・コスト削減を図りつつ、感度向上を図る。

【解決手段】アイランド部12と一次導体13とセンサリード端子14とを同一の平板から打ち出してリードフレームを形成し且つ、一次導体13をアイランド部12と電気的に切り離すとともに、前記アイランド部12の、平面視方形のICチップ11と同等形状を有するアイランド本体21を取り囲む略コの字状を有するコの字部31を備えて形成する。アイランド本体21にICチップ11を載置し、ICチップ11とセンサリード端子14とをボンディングワイヤ15により接続する。このときICチップ11の角部11a、11bの仮想的な面取り曲線上に、コの字部31のコーナー部31a、31bと対向するように磁場変換素子41を1以上配置する。そして、各磁場変換素子41の検出信号の総和を演算し、これを電流センサ10の検出信号として出力する。

(もっと読む)

スピン伝導素子

【課題】出力を向上可能なスピン伝導素子を提供する。

【解決手段】 このスピン伝導素子は、半導体層3と、半導体層3上に第1トンネル障壁層5Aを介して設けられた第1強磁性層1と、半導体層3上に、第1強磁性層1から離間し、且つ、第2トンネル障壁層5Bを介して設けられた第2強磁性層2と、を備え、半導体層3は、第1強磁性層1からその厚み方向に垂直な方向に沿って、第1強磁性層1から離れる方向へ広がる第1領域R1と、第1強磁性層1からその厚み方向に垂直な方向に沿って、第2強磁性層2に向かう方向に延びており、第1領域R1の不純物濃度よりも相対的に高い不純物濃度を有する第2領域R12と、を備えている。

(もっと読む)

磁気抵抗素子の製造方法及び製造装置

【課題】エッチングに用いられるハロゲン系成分による素子の腐食を防止することが可能な磁気抵抗素子の製造装置及び製造方法を提供すること

【解決手段】本発明の磁気抵抗素子10の製造方法は、基板上に強磁性材料からなる第1の強磁性層13を形成する。酸化マグネシウムからなる絶縁層14は、第1の強磁性層13上に形成される。Fe及びCoの少なくとも一方を含有する第2の強磁性層15は、絶縁層14上に形成される。ハロゲン系元素を含むプラズマによるエッチングは、基板11上に第1の強磁性層13、絶縁層14及び第2の強磁性層15が積層された積層体に対して施される。積層体は、H2Oを含むプラズマであるH2Oプラズマに曝露される。

(もっと読む)

オフセットキャンセル機能を有するホールセンサ及びこれのオフセットキャンセル方法

【課題】本発明は、ホール電圧に含まれたオフセットを取り除くオフセットキャンセル機能を有するホールセンサ及びこれのオフセットキャンセル方法に関する。

【解決手段】事前に設定された複数の検出方向に応じて磁界を電圧として検出するホール(Hall)デバイスにより、上記複数の検出方向別に検出された第1及び第2の検出電圧間のレベル差を幅として有するパルスに変換する変換部と、上記第1及び第2の検出電圧を比較し、その比較結果に応じて上記パルスの+符号又は−符号を決定する符号決定部と、上記変換部からのパルスの幅を事前に設定された基準時間の単位でカウントするカウンター、及び上記符号決定部により決定された符号に応じて、上記カウンターによりカウントされた数のマイナス演算を行い、上記第1及び第2の検出電圧に含まれたオフセット電圧を取り除く演算部を含む。

(もっと読む)

磁気センサ及びその感度測定方法

【課題】外部の感度測定用磁界発生源を用いることなく磁気センサの各軸方向の感度を測定する機能を有する磁気センサ及びその感度測定方法を提供すること。

【解決手段】感度測定装置では、感磁部(31)による検出された磁束密度は、切換部(32)によって各軸の磁界強度情報が抽出され、増幅部(33)を介して、感度演算部(34)に入力される。感度演算部(34)は、感磁部(31)からの各軸に関する磁界強度情報に基づいて感度を演算する。感度演算部は、感磁部(31)からの磁束密度を各軸の磁気成分に分解する軸成分分解部(34a)と、軸成分分解部(34a)からの磁界強度の各軸成分を基準値と比較して感度を判定する感度判定部(34b)と、感度判定部(34b)からの感度情報に基づいて感度補正を行う感度補正部(34c)とを備えている。センサ診断部(39)は、感度情報に基づいて磁気センサの感度良否を自己診断し、自己感度補正(調整)をする。

(もっと読む)

磁気センサ装置

【課題】磁気抵抗効果素子を飽和させることなく、被検知物へ掛かる磁界強度が強化され、検知感度を向上させる磁気センサ装置を得る。

【解決手段】筐体の中空部を搬送される被検知物の一方の面に搬送方向に沿って磁極が反転するように配置した第1の磁石と、前記被検知物の他方の面に前記第1の磁石の磁極と異なる磁極を対向して配置し前記第1の磁石との間で搬送方向に連続的な勾配磁界を形成する第2の磁石と、前記第1の磁石の磁極の反転部に第1の間隙を備えた第1のヨークと、前記第2の磁石の磁極の反転部に前記第1の間隙より長い第2の間隙を備えた第2のヨークと、前記被検知物と前記第1のヨークとの間の前記勾配磁界の弱磁界強度領域に設けられ、前記勾配磁界の強磁界強度領域を搬送される前記被検知物による磁界変化を検知する磁気抵抗効果素子とを備えた。

(もっと読む)

磁気センサ

【課題】ホール素子を有する磁気センサにおいて、簡易な回路構成である信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを除去することのできる磁気センサを提供する。

【解決手段】ホールプレートHは、ホールプレートHを流れる電流のキャリアの種類を、ゲート電極Gの電位Vgにより、電子または正孔のいずれか一方にすることが可能な両極性材料から形成される。さらに、入出力端子TA,TA’,TB,TB’が、ホールプレートHの面内で対向する電流入力端子対と電圧出力端子対とになり、その際に電流入出力端子対と電圧出力端子対とが互いに直交するような位置に形成される。

(もっと読む)

ホール素子及びホール素子を備えた半導体装置

【課題】ウェル層と基板の間の空乏層幅を抑制し、かつCMOSトランジスタとの混載が可能なホール素子を含む半導体装置を提供することを目的とする。

【解決手段】P型基板101に設けられたNウェル層103と、Nウェル層103の上面においてX方向に沿った電流を流す電流入力端子110、111と、前Nウェル層103の上面においてX方向と直交するY方向に沿った磁界を発生する電圧出力端子112、113と、を備える半導体装置において、Nウェル層103の底面とP型基板101との間に、導電型がN型であって、かつNウェル層103よりも不純物濃度の高い空乏層幅抑制用N+層120を設ける。

(もっと読む)

ホール素子及びその製造方法、半導体装置

【課題】コストの増大を抑えつつ、ホール素子のオフセット電圧Voを低減することができるようにしたホール素子及びその製造方法と、半導体装置を提供する。

【解決手段】半導体基板1に設けられた第1のN型拡散領域10と、半導体基板1に設けられ、第1のN型拡散領域10に電気的に接合された複数の第2のN型拡散領域20と、半導体基板1に設けられ、複数の第2のN型拡散領域20の各々の間を電気的に分離するSTI領域30と、を有する。第1のN型拡散領域10は感磁部であり、複数の第2のN型拡散領域20の各々は感磁部に対する入出力端子部である。複数の第2のN型拡散領域20の各々におけるN型の不純物濃度は、STI領域30の底部30bを基点に深さ方向で0μm以上、0.2μm以下の範囲内で、5×1017個/cm3以上、3×1019個/cm3以下である。

(もっと読む)

磁気抵抗効果素子、磁気ヘッドジンバルアッセンブリ、磁気記録再生装置、歪みセンサ、圧力センサ、血圧センサ及び構造物ヘルスモニタセンサ

【課題】高密度化対応の磁気抵抗効果素子、磁気ヘッドアッセンブリ、磁気記録再生装置、歪みセンサ、圧力センサ、血圧センサ及び構造物ヘルスモニタセンサを提供する。

【解決手段】基板上に積層された、第1の磁性層12と、第1の磁性層12に積層され、第1の磁性層の組成とは異なる第2の磁性層11と、第1の磁性層12と第2の磁性層11との間に配置されたスペーサ層13と、を有する積層体10と、積層体10に電流を流す1対の第1の電極と、積層体10の近傍に設けられ、積層体に歪みが印加されることで、第1の磁性層12及び第2の磁性層11の磁化方向がそれぞれ異なる方向にバイアスされるよう積層体10に歪みを印加する歪み導入部材と、歪み導入部材に電圧を印加するための第2の電極と、を備える。外部磁界が印加されることで、第1の磁性層12及び第2の磁性層11の磁化方向がともに変化し、磁化方向の変化により、外部磁界を検出する。

(もっと読む)

磁気センサ並びにそれを用いた電流センサ

【課題】 小型で微小な磁極間の磁界評価や、評価対象近傍領域の磁界評価ができる磁気センサを提供すること

【解決手段】 磁気センサ10は、外径125μmの光ファイバークラッドからなる円柱状のベース部材11の外周面に磁気抵抗薄膜12を被膜すると共に、その磁気抵抗効果膜12の軸方向両端に導体膜13を成膜して形成される。導体膜が電極部となる。導体膜間にセンス電流を流すことで、このセンス電流ベクトルと外部磁界による円柱周囲の確気抵抗薄膜の磁化ベクトルとの成す角度に応じて、磁気抵抗薄膜の抵抗変化が生じ、端子間の電圧変化として検出可能となる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】モールド成型によりパッケージ化されてなる半導体装置において、パッケージからのストレスに起因する半導体デバイスの特性変化のさらなる抑制を図る。

【解決手段】Si−LSI202a、202b全体をSiO2膜205とSiN膜206とで覆い、2つのSi−LSI202a、202b間のSi基板201表面に、化合物半導体デバイスからなるホール素子208の感磁部を形成する。ホール素子208とSi−LSI202a、202bとを金属配線210で接続した後、SiN膜211、SiO2膜212を形成して平坦化し、その上にAl配線213を形成する。基板上面からみて、Al配線213の、ホール素子208と重なる領域にエッチング溶液注入穴214を形成しここからエッチング溶液を注入してAl配線213の下部のSiO2膜212を除去し中空部215を形成する。

(もっと読む)

磁気抵抗素子

【課題】磁気抵抗素子の出力を低下させずに耐環境性の向上を図る。

【解決手段】GaAs単結晶基板(11)上に、SnドープInSb薄膜(12a)をエピタキシャル成長させ(図2(a))、InSb薄膜(12a)をメサエッチングして感磁部12を形成し、さらに、感磁部12の上に、保護膜16として窒化シリコン薄膜を形成する(図2(b))。短絡電極13、取り出し電極14および接続電極15を形成する部分の窒化シリコン薄膜(12a)を除去し(図2(c))、真空蒸着法により、各電極13〜15を蒸着し、リフトオフ法で短絡電極13、取り出し電極14および接続電極15を形成した。これら電極は、Ti/Pt/Auの積層構造とし、Ti/Pt/Au=100nm/20nm/450nmとした。そして、感磁部(12)および短絡電極13を含む全面に軟樹脂層17としてゴム系樹脂を形成した(図2(d))。

(もっと読む)

スピン伝導素子及び磁気ヘッド

【課題】 トンネル層における面抵抗の低減が図られたスピン伝導素子及び磁気ヘッドを提供する。

【解決手段】

本発明に係るスピン伝導素子(磁気センサー1)は、半導体で構成されるチャンネル層10と、チャンネル層10上に形成された強磁性層20A、20Bと、チャンネル層10と強磁性層20A、20Bとの間に介在するように形成されたトンネル層22A、22Bとを備え、トンネル層22A、22Bが、MgOのMgの一部がZnで置換された材料で構成されている。発明者らの研究によれば、MgOのMgの一部をZnで置換したトンネル材料において、面積抵抗の低下が観測された。そのため、トンネル層22A、22Bを、MgOのMgの一部がZnで置換された材料で構成することにより、トンネル層22A、22Bの面積抵抗の低減が図られる。

(もっと読む)

垂直ホールセンサおよび垂直ホールセンサを製造するための方法

【課題】 本発明は、半導体チップ(1)内に集積化される垂直ホールセンサおよびそれの製造のための方法に関する。

【解決手段】 垂直ホールセンサは、第2の導電型の導電性領域(3)内に埋め込まれる、第1の導電型の導電性ウェル(2)を有する。電気的接点(4)が、導電性ウェル(2)の平坦面(5)上で直線(6)に沿って配置される。導電性ウェル(2)は、それが導電性ウェル(2)の平坦面(5)から深さT1に位置する最大値を有するか、または深さT2まで本質的に一定であるかのどちらかのドーピング分布を有するように、高エネルギーイオン注入法およびその後の加熱によって生成される。

(もっと読む)

スピン伝導素子及び磁気ヘッド

【課題】高温域におけるスピン注入効率の低下が抑制されたスピン伝導素子及び磁気ヘッドを提供する。

【解決手段】Siで構成されるチャンネル層10と、チャンネル層10上に形成された強磁性層20A、20Bと、チャンネル層10と強磁性層20A、20Bとの間に介在するように形成され、BaOで構成されるトンネル層22A、22Bとを備える構造のスピン伝導素子。シリコンの格子定数は5.4309Åであり、BaOの格子定数は5.5263Åである。シリコンの格子定数に対して、BaOの格子定数は1.8%の差(不整合率)があり、この値は、シリコンとMgOの格子定数の差と比較して1/5程度である。トンネル材料としてBaOを採用し、シリコンとトンネル材料との間の格子定数の差を従来材料に比べて低減することで、高温域におけるスピン注入効率の低下が抑制される。

(もっと読む)

61 - 80 / 645

[ Back to top ]