Fターム[5F101BA12]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG形状構造 (858)

Fターム[5F101BA12]の下位に属するFターム

埋め込みFG、溝 (45)

CG側壁 (37)

FGの突起 (84)

複数FG(単一メモリセル内) (90)

FG接続 (271)

PN接合(FG内の) (5)

Fターム[5F101BA12]に分類される特許

41 - 60 / 326

半導体装置及び半導体装置の駆動方法

【課題】専有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、該記憶ゲートを絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1及び第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された読み出し信号線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

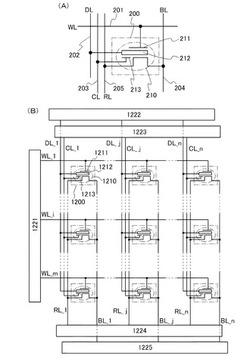

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、且つ書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば酸化物半導体材料を用いて半導体装置を構成する。また半導体装置の各メモリセルの酸化物半導体材料を用いたトランジスタを直列に接続する。更に、第j(jは2以上m以下の自然数)のメモリセルの容量素子の端子の一方に電気的に接続される配線と、第(j−1)のメモリセルのチャネルが酸化物半導体層に形成されたトランジスタのゲート端子に電気的に接続される配線と、を同じ配線(第jのワード線)とする。これによってメモリセルあたりの配線の数を減らし、メモリセルあたりの占有面積を低減する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路の抵抗素子の抵抗部の厚さに依らずにメモリセルトランジスタの浮遊ゲートの厚さを自由に設定することのできる半導体装置、およびその製造方法を提供すること。

【解決手段】基板上の抵抗素子およびスタックド・ゲート型のメモリセルトランジスタを含む半導体装置を提供する。前記抵抗素子は、抵抗として機能しない非導通層、および前記非導通層上に第1の絶縁膜を介して形成された抵抗として機能する導通層を含む。前記メモリセルトランジスタは、第1の浮遊ゲートを含む浮遊ゲートを有する。前記非導通層と前記第1の浮遊ゲートは、同じ材料からなる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

不揮発性半導体メモリトランジスタ、および、不揮発性半導体メモリの製造方法

【課題】浮遊・制御ゲート間の容量を増大できる、島状半導体を用いた不揮発性半導体メモリトランジスタを提供する。

【解決手段】不揮発性半導体メモリトランジスタは、Si基板側からソース領域303、チャネル領域304及びドレイン領域302がこの順に形成された島状半導体301と、前記チャネル領域の外周を囲むように、トンネル絶縁膜305を間に介在させて配置された浮遊ゲート306と、浮遊ゲートの外周を囲むように、インターポリ絶縁膜307を間に介在させて配置された制御ゲート308aと、制御ゲートに接続され、所定方向に延びる制御ゲート線308と、を備える。浮遊ゲートは制御ゲートの下方及び上方領域、並びに、制御ゲート線の下方領域まで夫々延在され、浮遊ゲートと、制御ゲートの上面、下面及び内側面との間、及び、浮遊ゲートの、制御ゲート線の下方領域まで延在した部分と、制御ゲート線との間には、夫々インターポリ絶縁膜が介在配置される。

(もっと読む)

不揮発性記憶装置

【課題】基板の活性領域と制御ゲート電極との間の高い耐電圧特性を有する不揮発性記憶装置を提供する。

【解決手段】素子分離絶縁溝を有する基板と、前記基板上の前記素子分離溝の両側に形成された第1および第2のトンネル絶縁膜、第1および第2の浮遊ゲート電極と、前記第1および第2の浮遊ゲート電極の上面を覆い、かつ前記第1の浮遊ゲート電極と第2の浮遊ゲート電極との間、前記第1のトンネル絶縁膜と第2のトンネル絶縁膜との間、および前記素子分離絶縁溝の少なくとも上部を埋めるように形成されたゲート間絶縁膜と、前記ゲート間絶縁膜上に形成された制御ゲート電極と、を有する不揮発性記憶装置を提供する。前記ゲート間絶縁膜は、電子トラップ性を有する第1の絶縁材料からなる電子トラップ層と、前記第1の材料よりも電子トラップ性が低い第2の絶縁材料からなり、前記電子トラップ層を挟む第1および第2の絶縁層とを含む。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

不揮発性半導体メモリトランジスタ、不揮発性半導体メモリ、および、不揮発性半導体メモリの製造方法

【課題】浮遊ゲートと制御ゲート間の容量を大きくすることができるとともに、かつ制御ゲートと島状半導体間の寄生容量を低減する、島状半導体を用いた構造を持つ不揮発性半導体メモリ、およびその製造方法を提供する。

【解決手段】不揮発性半導体メモリを構成する不揮発性半導体メモリトランジスタは、基板側からソース領域303、チャネル領域304及びドレイン領域302がこの順に形成された島状半導体301と、チャネル領域の外周を囲むように、トンネル絶縁膜305を間に介在させて配置された中空柱状の浮遊ゲート306と、当該浮遊ゲートの外周を囲むように、インターポリ絶縁膜307を間に介在させて配置された中空柱状の制御ゲート308と、を備えている。浮遊ゲートと、制御ゲートの上面、下面および内側面との間には、インターポリ絶縁膜が介在配置されている。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

不揮発メモリ装置及び不揮発メモリ装置の製造方法

【課題】不揮発メモリ装置のメモリセルを小型化する。

【解決手段】フローティングゲート電極120は、トンネル絶縁膜110の上に形成されている。コントロールゲート電極140は、第1絶縁膜130を介してフローティングゲート電極120の上に形成されている。セレクトゲート絶縁膜150は、基板10の上に形成されており、トンネル絶縁膜110の横に位置している。セレクトゲート電極170はセレクトゲート絶縁膜150上に位置している。またセレクトゲート電極170は、第2絶縁膜160を介してフローティングゲート電極120の横に位置している。そしてセレクトゲート電極170のうちフローティングゲート電極120に面する側面は、下端174が第2絶縁膜160の下に入り込んでいる。

(もっと読む)

半導体装置

【課題】不揮発性メモリセルのデータ書き込みおよび消去用の素子において、チャネル全面のFNトンネル電流によりデータを書き換える。

【解決手段】フラッシュメモリの形成領域の半導体基板1Sのn型の埋込ウエルDNW内にp型のウエルHPW1〜HPW3を互いに分離した状態で設け、そのウエルHPW1〜HPW3にそれぞれ容量部C、データ書き込み・消去用の容量部CWEおよびデータ読み出し用のMIS・FETQRを配置した。データ書き込み・消去用の容量部CWEでは、チャネル全面のFNトンネル電流によりデータの書き換え(書き込みおよび消去)を行う。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】デバイス特性の劣化を抑制した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】第1ダミーセル領域121に設けられた素子分離絶縁層33と、第2ダミーセル領域122に設けられた素子分離絶縁層43と、第1ダミーセル領域121と第2ダミーセル領域122との間の境界に位置する素子分離絶縁層51とを備える。素子分離絶縁層33の上面は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層43の上面は、浮遊電極層42の上面と同じ高さに位置する。浮遊電極層32に隣接する素子分離絶縁層51の上面の端部は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層51の上面は、浮遊電極層32の側面から浮遊電極層42の側面へ向かって上昇する傾斜TLを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去特性の変動が小さく、特性の安定した不揮発性半導体記憶装置を実現する。

【解決手段】不揮発性半導体記憶装置50は、第1導電型の半導体基板1上にゲート電極6bを有し第2導電型のMISFET5と、半導体基板1上の第2導電型第1ウェル3に設けられ、第1容量電極6cを有する第1MISキャパシタ15と、半導体基板1上の第2導電型第2ウェル4に設けられ、第2容量電極6aを有する第2MISキャパシタ21とを備える。ゲート電極6b、第1容量電極6c、第2容量電極6aが電気的に接続されてフローティングゲート6を構成する。第2MISキャパシタ21にて、第2ウェル4と、第2ウェル4上の部分の第2容量電極6aとがキャパシタ領域を構成する。第2容量電極6aは、キャパシタ領域が複数の分割キャパシタ領域に分割され、各分割キャパシタ領域の面積が変動してもその総面積は略一定となる平面形状及び配置を有する。

(もっと読む)

半導体装置

【課題】バーズビーク酸化に関する問題を効果的に解決することが可能な半導体装置を提供する。

【解決手段】半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜上に形成された浮遊ゲート電極3と、浮遊ゲート電極上に形成された電極間絶縁膜6と、電極間絶縁膜上に形成された制御ゲート電極7と、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ浮遊ゲート電極のチャネル長方向に平行な一対の側面の下端近傍に形成された一対の酸化膜4aと、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ一対の酸化膜の間に形成された窒化膜2cとを備え、一対の酸化膜はそれぞれ、チャネル幅方向に平行な断面において上から下に向かってしだいに幅が広くなっている楔状の形状を有している。

(もっと読む)

半導体記憶装置

【課題】書込み特性及びデータ保持特性に優れた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、基板101と、基板上に順に形成された、FN(Fowler-Nordheim)トンネル膜として機能するゲート絶縁膜111と、浮遊ゲート112と、電荷ブロック膜として機能するゲート間絶縁膜113と、制御ゲート114とを含むメモリセルトランジスタ201とを備え、メモリセルトランジスタは更に、浮遊ゲートに上下を挟まれるよう形成され、電荷をトラップする機能を有する電荷トラップ層121を含み、浮遊ゲート112は、電荷トラップ層121の上面と、下面と、互いに対向する1組の側面とを覆っている。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の特性の低下を抑制しつつ、メモリセルの微細化をはかった半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、基板101と、基板上に形成され、FN(Fowler-Nordheim)トンネル膜として機能するゲート絶縁膜111と、ゲート絶縁膜上に形成された第1の浮遊ゲート112と、第1の浮遊ゲート上に形成され、FNトンネル膜として機能する第1のゲート間絶縁膜113と、第1のゲート間絶縁膜上に形成された第2の浮遊ゲート114と、第2の浮遊ゲート上に形成され、電荷ブロック膜として機能する第2のゲート間絶縁膜115と、第2のゲート間絶縁膜上に形成された制御ゲート116とを備える。

(もっと読む)

Fin−FET型不揮発性メモリ・セル及びアレイ並びにその製造方法

不揮発性メモリ・セルが、基板層を有し、第1の導電型のフィン形状半導体部材が基板層上にある。フィン形状部材は、第2の導電型の第1の領域と、第1の領域から離間配置された第2の導電型の第2の領域とを有し、チャネル領域が第1の領域と第2の領域との間に延びている。フィン形状部材は、第1の領域と第2の領域との間に上面及び2つの側面を有する。ワード線が、第1の領域に隣接し、チャネル領域の第1の部分の上面及び2つの側面に容量結合される。浮遊ゲートが、ワード線に隣接し、上面から絶縁され、チャネル領域の第2の部分の2つの側面に容量結合される。 (もっと読む)

41 - 60 / 326

[ Back to top ]