Fターム[5F110DD06]の内容

Fターム[5F110DD06]の下位に属するFターム

Fターム[5F110DD06]に分類される特許

21 - 40 / 298

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

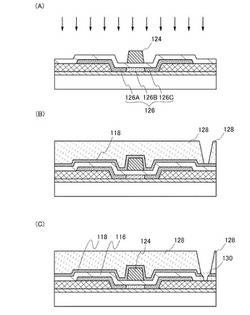

薄膜トランジスタ、これを備えた表示装置、およびその製造方法

【課題】薄膜トランジスタ、これを備えた表示装置、およびその製造方法に関する。

【解決手段】本発明に係る薄膜トランジスタは、基板上に形成され、金属触媒の作用による結晶の成長によって結晶化したアクティブ層と、アクティブ層の一部領域上に形成されたゲート絶縁膜パターンと、ゲート絶縁膜パターンの一部領域上に形成されたゲート電極と、ゲート絶縁膜パターン上にゲート絶縁膜パターンと同じパターンで形成され、ゲート電極を覆うエッチング防止膜パターンと、アクティブ層およびエッチング防止膜パターン上に形成されたソース電極およびドレイン電極と、アクティブ層およびエッチング防止膜パターンとソース電極およびドレイン電極の間にソース電極およびドレイン電極と同じパターンで形成され、アクティブ層の結晶化に用いられた金属触媒を除去するゲッタリング層パターンとを含む。

(もっと読む)

半導体装置の作製方法

【課題】 大面積のガラス基板上に薄膜からなる集積回路を形成し、他の基体に転写して分断を行い、接触、好ましくは非接触でデータの受信または送信が可能な微細なデバイスを大量に効率よく作製する方法を提供することを課題とする。特に薄膜からなる集積回路は、非常に薄いため移動時に飛んでしまう恐れがあり、取り扱いが難しかった。

【解決手段】 本発明は、剥離層に達する多数の穴または多数の溝を設け、穴(または溝)およびデバイス部に重ならない領域にパターン形状を有する材料体を設けた後、ハロゲン化フッ素を含む気体又は液体を導入して、前記剥離層を選択的に除去する。

(もっと読む)

半導体装置

【課題】高い開口率を有し、安定した電気特性を有する薄膜トランジスタを有する、信頼

性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動

回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物

半導体によって構成された駆動回路用薄膜トランジスタと、金属によって構成された駆動

回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体に

よって構成され且つ半導体層が酸化物半導体によって構成された画素用薄膜トランジスタ

と、酸化物導電体によって構成された表示部用配線とを有する。

(もっと読む)

半導体装置

【課題】Inversion型トランジスタやIntrinsic型トランジスタ、及び半導体層の蓄積層電流制御型Accumulation型トランジスタでは不純物原子濃度の統計的ばらつきによってしきい値電圧のばらつきが微細化世代で大きくなってしまい、LSIの信頼性を保つことが困難であった。

【解決手段】空乏層の厚さが半導体層の膜厚よりも大きくなるように、半導体層の膜厚と不純物原子濃度を制御することによって形成されたバルク電流制御型Accumulation型トランジスタが得られる。例えば、半導体層の膜厚を100nmにすると共に不純物濃度2×1017[cm−3]より高くすることによって、しきい値のばらつきの標準偏差が電源電圧のばらつきよりも小さくすることができる。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

導電性酸化物およびその製造方法、ならびに酸化物半導体膜

【課題】スパッタリング用ターゲットとして好ましく使用され得る導電性酸化物およびその製造方法を提供する。

【解決手段】結晶質InGa(1-m)Zn(1-q)O(4-p)(0<m<1、0<q<1、0≦p≦3m/2+q)と、結晶質Ga2ZnO4とを含む、導電性酸化物である。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

導電性酸化物およびその製造方法、ならびに酸化物半導体膜

【課題】スパッタリング用ターゲットとして好ましく使用され得る導電性酸化物およびその製造方法を提供する。

【解決手段】結晶質In2O3と、結晶質Ga2ZnO4とを含む導電性酸化物であって、導電性酸化物において、Znの原子濃度比を1とした場合に、Inの原子濃度比が0.4以上1.8以下であり、かつ、Gaの原子濃度比が0.4以上1.8以下の導電性酸化物とし、In−Ga−Zn−O酸化物のスパッタリング用のターゲットとして用いること。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用いたnチャネルTFTのみを用いてバッファ回路やインバータ回路などを構成することを課題の一つとする。

【解決手段】ソース電極及びドレイン電極の両方がゲート電極に重なる第1のトランジスタと、ソース電極はゲート電極と重ね、且つ、ドレイン電極はゲート電極と重ならない第2のトランジスタとを組み合わせてバッファ回路やインバータ回路などを構成する。第2のトランジスタをこのような構造とすることによって、容量Cpを小さくし、電位差VDD−VSSが小さい場合でもVA’が大きくとれるようになる。

(もっと読む)

半導体装置、半導体ウエハ、及びこれらの製造方法

【課題】トランジスタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】SOI基板101は、P型半導体層102の上にN型半導体層104が形成された半導体基板12、その上に形成されたBOX層106、及びBOX層上に形成されたSOI層108を有する。第1素子分離絶縁層110bは、SOI基板101に埋め込まれ、下端16がP型半導体層102に達し、第1素子領域(NFET領域30)と第2素子領域(PFET領域40)とを分離する。P型トランジスタ130bは、第1素子領域40に位置し、チャネル領域120bを有し、N型トランジスタ130aは、NFET領域30に位置し、チャネル領域120aを有する。第1バックゲートコンタクト134bは、第1素子領域40に位置する第2導電型層層104に、第2バックゲートコンタクト134aは、第2素子領域30に位置する第2導電型層104に接続される。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。

【解決手段】デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成する。伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを形成する。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】少なくとも微結晶半導体領域及び非晶質半導体領域が積層する半導体膜を有する逆スタガ型の薄膜トランジスタにおいて、半導体膜上に導電膜及びエッチング保護膜を積層形成し、エッチング保護膜上にマスクを形成し、エッチング保護膜、導電膜及び非晶質半導体領域の一部をエッチングする第1のエッチング処理の後、マスクを除去する。次に、上記エッチングされたエッチング保護膜をマスクとして、露出した非晶質半導体領域及び微結晶半導体領域の一部をドライエッチングする第2のエッチング処理により、微結晶半導体領域の一部を露出させ、バックチャネル領域を形成する。

(もっと読む)

液晶表示装置、及び液晶表示装置の駆動方法

【課題】動画と静止画を表示可能な液晶表示装置において、誤動作を低減し、低消費電力化が可能な液晶表示装置を提供する。

【解決手段】端子部、スイッチングトランジスタ、駆動回路部、並びに画素トランジスタ及び複数の画素を有する画素回路部、が形成された第1の基板と、スイッチングトランジスタを介して端子部と電気的に接続される共通電極が形成された第2の基板と、画素電極と共通電極との間には液晶が挟持されており、静止画を表示する期間において、スイッチングトランジスタの第1の端子と第2の端子とを非導通状態とし、共通電極を電気的に浮遊状態とし、静止画から動画に切り替わる期間において、共通電極に共通電位を供給する第1のステップ、駆動回路部に電源電圧を供給する第2のステップ、駆動回路部にクロック信号を供給する第3のステップ、駆動回路部にスタートパルス信号を供給する第4のステップ、の順に行う。

(もっと読む)

半導体装置

【課題】ラッチ型メモリが搭載されたCPUを動作させるに際して、処理内容に応じて常時記憶方式と終了時記憶方式のいずれかを選択し、ラッチ型メモリが搭載されたCPUの消費電力を低減する。

【解決手段】ラッチ型メモリが搭載されたCPUを動作させるに際して、電源のオンオフの繰り返し動作が多い場合には常時記憶方式とし、電源のオンオフの繰り返し動作が少ない場合には終了時記憶方式とする。常時記憶方式と終了時記憶方式のどちらを選択するかは、消費電力に応じて決定したしきい値をもとにして決定する。

(もっと読む)

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

低温ポリシリコンTFTのための多層高品質ゲート誘電体

【課題】TFTデバイスにおける高品質ゲート誘電体層を形成するのに有用な方法及び装置を提供する。

【解決手段】高密度プラズマ酸化(HDPO)処理層がチャネル、ソース、及びドレイン領域上に形成されて誘電体インターフェースを構成し、次に、1つ以上の誘電体層をHDPO層上に堆積して高品質ゲート誘電体層を形成する。HDPO処理は、一般的に、誘導及び/又は容量結合RF伝達デバイスを用いてプラズマを発生し、基板上で発生したプラズマを制御し、また酸化源を含有するガスを注入して界面層を成長させる。次に、第2誘電体層をCVD又はPECVD堆積処理を用いて基板上に堆積する。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

21 - 40 / 298

[ Back to top ]