Fターム[5F140BF21]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層 (490)

Fターム[5F140BF21]に分類される特許

61 - 80 / 490

半導体装置及びその製造方法

【課題】調整用金属を含む高誘電率膜を有するゲート絶縁膜を備えたMISトランジスタを有する半導体装置において、MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、MISトランジスタnTrを備えている。MISトランジスタは、半導体基板10における素子分離領域11に囲まれた活性領域10aと、活性領域及び素子分離領域上に形成され、高誘電率膜15aを有するゲート絶縁膜16aと、ゲート絶縁膜上に形成されたゲート電極19aとを備えている。ゲート絶縁膜における素子分離領域上に位置する部分のうち、少なくとも一部分には、窒化領域20x,20yが設けられている。窒化領域20x,20yに含まれる窒素の窒素濃度をn1,n2とし、ゲート絶縁膜における活性領域上に位置する部分に含まれる窒素の窒素濃度をnとしたとき、n1>n、且つ、n2>nの関係式が成り立っている。

(もっと読む)

半導体装置の製造方法

【課題】希土類金属を含有するHigh-k膜のエッチング残渣を抑制するための半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に絶縁膜4を形成する工程と、絶縁膜4の上に希土類元素含有酸化膜7、12を形成する工程と、フッ酸、塩酸、硫酸を含む薬液により希土類元素含有酸化膜7、12をエッチングする工程とを有し、これにより希土類元素含有酸化膜7、12のエッチングを良好に行う。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極と半導体基板との間のショートの発生を抑制した上で、厚さが厚く、かつ均一な厚さとされたシリサイド層を形成可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜27を介して、ピラー26の側面26a,26bに設けられたゲート電極61,62と、ピラー26の上端26−1に形成されたシリサイド層38と、ゲート電極61,62を覆うと共に、ピラー26の側面を囲むように配置され、かつシリサイド層38の側面を露出する絶縁膜と、シリサイド層38の側面を覆うように設けられ、かつピラー26の上端26−1に含まれるシリコンをシリサイド化させる金属膜39と、シリサイド層38の下面38bと接触するように、ピラー26に形成された上部不純物拡散領域36と、シリサイド層38の上面38aに設けられたキャパシタ52と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性に優れた半導体装置が得られる製造方法を提供する。

【解決手段】半導体装置の製造方法は、p型電界効果トランジスタおよびn型電界効果トランジスタを備える半導体装置の製造方法であって、基板上に、界面絶縁層および高誘電率層をこの順で形成する工程と、高誘電率層上に、犠牲層のパターンを形成する工程と、犠牲層が形成されている第1の領域の高誘電率層上および犠牲層が形成されていない第2の領域の高誘電率層上に、金属元素を含む金属含有膜を形成する工程と、熱処理を行うことにより、第2の領域における界面絶縁層と高誘電率層との界面に金属元素を導入する工程と、犠牲層をウエットエッチングにより除去する工程と、を含み、除去する工程において、犠牲層は、高誘電率層よりもエッチングされやすい。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にHK絶縁膜を用いたMIS構造の半導体装置において、HK絶縁膜端部近傍における酸素過剰領域の発生に起因するトランジスタ特性の劣化を防止する。

【解決手段】半導体基板100上にゲート絶縁膜108a、108bを介してゲート電極109a、109bが形成されている。ゲート電極109a、109bの側面上に導電性酸化物からなるサイドウォールスペーサ111a、111bが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加するシリコン混晶層を活性領域に設けた半導体装置において、電流駆動能力の向上とリーク電流の低下と図れるようにする。

【解決手段】半導体装置は、シリコンからなる半導体基板10に形成され、周囲を素子分離領域11により囲まれてなる第2の活性領域10bと、該第2の活性領域10b及び素子分離領域11の上に、ゲート絶縁膜13を介在させて形成されたゲート電極14とを有している。第2の活性領域10bには、ゲート電極14の両側方の領域が掘り込まれてなるリセス領域19cにp型シリコン混晶層21が形成されており、該p型シリコン混晶層21における素子分離領域11と接触する接触位置の上端21bは、第2の活性領域10bの上面におけるゲート絶縁膜13の下側部分よりも低い。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、AlN−Al2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】ノーマリーオフ半導体素子のための高品質の酸化物からなる絶縁膜を提供する。

【解決手段】半導体積層構造を有する基板3の上に、酸化物を含む絶縁膜を形成する工程において、酸化物を構成する元素単体ないしは元素の化合物を半導体積層構造を有する基板3の上に付着させる際に、水素ガス中に高純度水を加熱ないしは冷却することにより水蒸気圧を精密制御して混入させることにより、元素単体ないしは元素の化合物を酸化させる酸素分圧を精密に制御して、酸化物の組成を精密制御し、もって半導体積層構造を有する基板3と物理化学的に整合する絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体素子

【課題】選択的酸化工程を含む金属ゲートパターンを有する半導体素子を提供する。

【解決手段】半導体素子は、半導体基板、半導体基板上に形成されたポリシリコン層、ポリシリコン層上に形成されたバリヤ金属層、及びバリヤ金属層上に形成されたタングステン層を含み、側壁を有する金属ゲートパターンと、金属ゲートパターンの側壁上に形成されたシリコンオキサイド層と、金属ゲートパターンの側壁のシリコンオキサイド層上に形成されたシリコンナイトライド層と、を含む半導体素子であって、金属ゲートパターンは、90nm未満のゲート長を有し、シリコンオキサイド層は、ポリシリコン層の側壁に接触し、シリコンオキサイド層は、第1部分及び第2部分を含むが、第1部分は、ポリシリコン層の側壁の直接上に位置し、第2部分は、タングステン層の側壁上に位置し、第1部分は、第2部分よりさらに厚いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】工程を増加することなく、エクステンション領域をゲート端から遠ざけ、実効ゲート長の拡大を図ると同時に、狭ピッチ化に対応する。

【解決手段】裾引き状のオフセットサイドウォール6aをマスクにエクステンション注入を行い、エクステンション領域7を形成し、オフセットサイドウォール6a上にソース・ドレイン注入用のサイドウォール9を形成し、ソース・ドレイン領域10を形成する。

(もっと読む)

半導体装置及びその製造方法

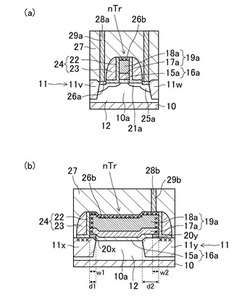

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】キャップ材料を使用した半導体装置のウェハ面内における閾値電圧Vtのバラツキを抑制することを目的とする。

【解決手段】まず、半導体基板1001の上に、高誘電率ゲート絶縁膜1006及び第1のキャップ膜1008を順に形成する。次に、熱処理を行って、第1のキャップ膜1008中の第1の金属を高誘電体膜1006に拡散させる。その後、高誘電体膜1006に拡散せずに高誘電体膜1006の上に残存した第1のキャップ膜1008を除去して、第1の金属が拡散した高誘電率ゲート絶縁膜1006Aの上に金属電極1010を形成する。

(もっと読む)

半導体装置

【課題】本発明は、不純物拡散層と半導体基板との間に形成される空乏層中におけるGIDLを抑制することのできる半導体装置を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成された第2の溝32と、少なくとも第2の溝32の側面32aを覆うゲート絶縁膜38と、ゲート絶縁膜38を介して、第2の溝32の側面32aに形成され、その上端面45aが半導体基板11の表面11aより低い位置にあってゲート電極39となる第1の導電膜45と、第1の導電膜45に形成され、その上端面46aが第1の導電膜45の上端面45bよりも高く、かつ半導体基板11の表面11aより低い位置にあってゲート電極39となる第2の導電膜46と、第1の導電膜45の上端面45b、及び第1の導電膜45の上端面45bから突出した第2の導電膜46を覆うように、第2の溝32内に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜20と、ゲート絶縁膜上に形成されたキャップ膜22と、キャップ膜上に形成されたシリコン酸化膜23と、シリコン酸化膜上に形成された金属ゲート電極24と、金属ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層48とを有している。

(もっと読む)

61 - 80 / 490

[ Back to top ]