Fターム[5F140BF21]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層 (490)

Fターム[5F140BF21]に分類される特許

141 - 160 / 490

半導体装置およびその製造方法

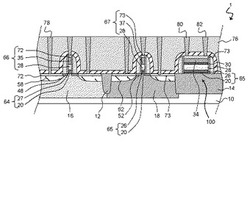

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】特性の劣化を効果的に抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaNを含む半導体層1と、電極とを備えている。電極は、電極本体6と、半導体層1から見て電極本体6よりも離れた位置に形成され、かつAlを含む接続用電極8と、電極本体6と接続用電極8との間に形成されたW、TiW、WN、TiN、Ta、およびTaNよりなる群から選ばれる少なくとも1種を含むバリア層7とを含んでいる。バリア層7の表面粗さRMSが3.0nm以下である。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法

【課題】低いオン抵抗と高い耐圧性とを有する電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法を提供する。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板101と、前記基板上に形成された高抵抗層103と、前記高抵抗層上に形成された、炭素濃度が1×1018cm−3以下であり層厚が10nmより厚く、100nm以下であるチャネル層104を含む半導体動作層106と、前記半導体動作層に前記チャネル層の内部に到る深さまで形成されたリセス部107と、前記半導体動作層上に前記リセス部を挟んで形成されたソース電極108およびドレイン電極109と、前記半導体動作層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜110と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極111と、を備える。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

半導体装置

【課題】寿命を可及的に長くすることの可能なMISFETを備えた半導体装置を提供する。

【解決手段】半導体領域2が形成された半導体基板1と、半導体領域に離間して形成されたソース領域5aおよびドレイン領域5bと、ソース領域とドレイン領域との間の半導体領域3上に形成され金属および酸素を含む金属酸化層12を有するゲート絶縁膜10と、ゲート絶縁膜上に形成されたゲート電極16と、を有するMISFETを備え、金属酸化層に含まれる金属はHf、Zrのうちから選択された少なくとも1つであり、金属酸化層は、更にRu、Cr、Os、V、Fe、Tc、Nb、Taのうちから選択された少なくとも1つの元素が添加され、金属酸化層は元素が添加されたことにより形成される電荷を捕獲または放出する電荷トラップを有し、金属酸化層中における元素の密度は、1×1015cm−3以上、2.96×1020cm−3以下の範囲にあり、電荷トラップは、金属酸化層の中央より半導体領域側にピークを有するように分布することを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置の製造方法

【課題】 閾値電圧の低い金属ゲート電極においてPMISFETの製造方法を提供する。

【解決手段】 半導体基板10上にPMISFETを作製する方法であって、半導体基板10上に絶縁膜20を形成する工程と、半導体基板10及び絶縁膜20をハロゲン化合物を含むガスにさらして、絶縁膜20上に吸着層110を形成する工程と、吸着層110上に金属を含むゲート電極40を形成して、吸着層110とゲート電極40を反応させて、吸着層110をハロゲン含有金属層にする工程とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できようにする。

【解決手段】半導体装置は、素子分離領域102により分離された活性領域103を有する半導体基板101と、活性領域103の上に形成されたゲート絶縁膜111と、ゲート絶縁膜111の上に形成されたゲート電極121とを備えている。ゲート絶縁膜111は、シリコン及び酸素を除く第1の元素が拡散している。素子分離領域102は、第1の素子分離膜102Aと、第1の素子分離膜102Aよりもゲート絶縁膜111側に形成され且つ第1の素子分離膜102Aと比べて第1の元素が拡散しにくい第2の素子分離膜102Bとを有している。

(もっと読む)

半導体素子及びその製造方法

【課題】 加熱処理により、ランタンやアルミニウムがhigh−k材料とシリコン基板との間の酸化シリコン膜まで拡散する。ランタンやアルミニウムの拡散が、チャネル移動度の低下や素子の信頼性の低下の原因になる。

【解決手段】 半導体基板の一部の領域上に、SiとOとを含む絶縁層が形成されている。絶縁層の上に、ハフニウムシリケートを含む下側高誘電率膜が形成されている。下側高誘電率膜の上に、ハフニウム酸化物、またはHfとSiとの合計の原子数に対するHfの原子数の比が、下側高誘電率膜のそれよりも大きいハフニウムシリケートを含む上側高誘電率膜が形成されている。上側高誘電率膜の上にゲート電極が形成されている。ゲート電極の両側にソース及びドレインが配置されている。

(もっと読む)

選択的酸化プロセス

【課題】部分的なシリコンの選択酸化を行う際、集積回路の露出した金属含有材料が酸化されることを防ぐ製造方法を提供する。

【解決手段】シリコンおよび金属含有材料は、部分的に製造された集積回路の露出された部分であり、例えばトランジスタの一部を形成してもよい。このシリコンおよび金属含有材料は、酸化剤および還元剤を含む雰囲気中で酸化される。いくつかの実施形態では、この還元剤は約10体積%以下の濃度で存在する。

(もっと読む)

半導体装置の製造方法

【課題】実効酸化膜厚の極めて薄いゲート絶縁膜を有し、且つ、消費電力の少ない半導体装置を、高い歩留まりで製造することができる半導体装置の製造方法をする。

【解決手段】液体の酸化剤を用いてシリコン基板1の表面を雰囲気に露出させることなく酸化することにより、シリコン基板1の表面にシリコン酸化膜6を形成し、

シリコン酸化膜6の上にアルミニウム酸化膜7を形成し、

アルミニウム酸化膜7の上にランタン酸化膜8を形成し、

ランタン酸化膜8の上にハフニウムシリケイト膜9Aを形成し、

その後、窒素を導入して熱処理を行うことにより、ハフニウムシリケイト膜9Aを窒化させて窒化ハフニウムシリケイト膜9を形成し、

前記熱処理により、シリコン酸化膜6ないしランタン酸化膜8を、ランタンアルミニウムシリケイトとする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】デュアルゲート電極構造のMOSトランジスタにおいて、閾値電圧シフト及びばらつきを抑えることができる半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板上にP型MOSトランジスタ及びN型MOSトランジスタを備える半導体装置において、P型MOSトランジスタ及びN型MOSトランジスタは、それぞれチャネル極性と同極のポリゲート電極を備えたデュアルゲート構造のMOSトランジスタであって、デュアルゲート型MOSトランジスタのポリゲート電極が、ゲルマニウムからなる第1のポリゲート電極層と、ゲルマニウムとシリコンとが混在した第2のポリゲート電極層と、シリコンからなる第3のポリゲート電極層と、を順次備えた積層構造を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】N型トランジスタ、P型トランジスタともに低い閾値電圧が得られる半導体装置及びその製造方法を提供する。

【解決手段】基板上の第1領域201にN型トランジスタが形成され、前記基板上の第2領域202にP型トランジスタが形成された半導体装置101であって、前記基板111と、シリコンを含有する第1のゲート絶縁膜121と、第1の金属と酸素とを含有する第2のゲート絶縁膜122と、前記第1の金属と異なる第2の金属と酸素とを含有する第3のゲート絶縁膜123と、ハフニウムを含有する第4のゲート絶縁膜124と、金属と窒素とを含有するゲート電極層131とを備え、前記第2領域に形成された前記ゲート電極層の厚さは、前記第1領域に形成された前記ゲート電極層の厚さよりも厚くなっている。

(もっと読む)

スタティック・ランダム・アクセス・メモリ

【課題】スタティックノイズマージンの低下を抑制できるスタティック・ランダム・アクセス・メモリを得ること。

【解決手段】スタティック・ランダム・アクセス・メモリのメモリセルにおける一対のロードトランジスタは、それぞれ、第1のSiGe膜がシリコン基板のソース領域と第1のシリサイド膜との間に存在し、第2のSiGe膜がシリコン基板のドレイン領域と第2のシリサイド膜との間に存在し、前記第1のSiGe膜ならびに前記第2のSiGe膜は、前記前記ソース領域と前記ドレイン領域の間のチャネル領域のシリコン基板の表面よりも低い位置に存在することを特徴とする。

(もっと読む)

141 - 160 / 490

[ Back to top ]