Fターム[5F140BG14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁構造及び配置 (6,762) | ゲート側壁材料 (3,458) | SiN (1,528)

Fターム[5F140BG14]に分類される特許

201 - 220 / 1,528

半導体装置の製造方法

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

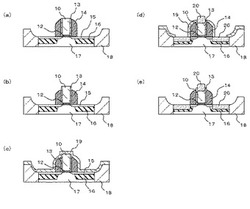

半導体装置の製造方法

【課題】ソース/ドレイン領域と基板との間の容量の低下を防止でき、パンチスルー現象を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極の上面及び側面を覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をマスクとして前記半導体基板の表面に溝部を形成する工程と、前記溝部の底面上に、該溝部の側壁の上部の露出を残す厚さで第3絶縁膜を形成する工程と、前記露出された溝部の側壁の上部を起点としたエピタキシャル成長により、前記第3絶縁膜上に前記半導体のエピタキシャル層を形成する工程と、前記エピタキシャル層に不純物を導入してソース/ドレイン領域を形成する工程と、を有することを特徴とする

(もっと読む)

半導体装置の製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを半導体基板上に集積する場合に製造コストを低減できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、ディプレッション型電界効果トランジスタの形成予定領域12Daでゲート電極12に開口部32,33を形成する工程と、ゲート電極12をマスクとして、アクティブ領域21に不純物を斜めイオン注入することにより、開口部32,33の下方にゲート電極12の両側の一方から他方にかけて連続的に分布する不純物拡散領域を形成すると同時に、ゲート電極12の両側にそれぞれ不純物拡散領域を形成する工程とを含む。

(もっと読む)

MISFET及びその製造方法

【課題】 LDD領域の長さを精度良く調整可能で、高周波動作に適用できる非対称な横方向二重拡散型MISFETを提供する。

【解決手段】 第1導電型のウェル1の上方にゲート絶縁膜3を介してゲート電極5を形成する工程、ウェル1に第2導電型の不純物イオン注入によりドレイン領域7を形成する工程、ウェル1の上方にゲート電極5が形成されるゲート電極領域とドレイン領域7を少なくとも覆い、ゲート電極領域とドレイン領域の間が開口したマスクパターン層を形成する工程、マスクパターン層をマスクとして自己整合的に、マスクパターン層で覆われていない領域に第2導電型の不純物イオン注入によりドレイン領域より低濃度のLDD拡散領域6を形成する工程、及び、ウェル1のゲート電極5を挟んでドレイン領域7の反対側の領域に第2導電型の不純物イオン注入によりLDD拡散領域より高濃度のソース領域を形成する工程を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体装置

【課題】トランジスタ特性に優れ、ゲート絶縁膜のゲート電極の近傍の領域中で電荷や電界の集中が起こらない半導体装置を提供する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタのゲート絶縁膜は窒素原子及び酸素原子を含有する。ゲート絶縁膜は、半導体層に接する第1の面及びゲート電極に接する第2の面において窒素原子を含有せず、第1の面と第2の面の間に窒素原子濃度のピークを有する。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタに適当なしきい値電圧が与えられる一方、抵抗素子はシリコン膜からなる抵抗体層の異常成長を抑制して、シリコン膜の膜厚を安定化する。

【解決手段】半導体装置は、半導体基板10の上部に形成された素子分離領域12によって囲まれた第1の活性領域10a、第1の活性領域の上に形成された第1の高誘電体膜14aを有する第1のゲート絶縁膜27a、及び第1のゲート絶縁膜の上に形成された第1のゲート電極28aとを有する第1導電型の第1のMISトランジスタ1aと、素子分離領域の上に形成された第2の高誘電体膜14x、及び該第2の高誘電体膜の上に形成されたシリコンからなる抵抗体層20xを有する抵抗素子1xとを備えている。第1の高誘電体膜と第2の高誘電体膜とは、互いに同一の高誘電体材料からなり、第1の高誘電体膜は第1の調整用金属を含み、第2の高誘電体膜は第1の調整用金属を含まない。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加しつつ、基板やソース/ドレイン領域においてリーク電流の発生が効果的に抑制された半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の不純物を含み、素子形成領域170を有する半導体基板101と、素子形成領域170上にゲート絶縁膜132を挟んで形成されたゲート電極125と、ゲート電極125の両側方に形成され、第2導電型の不純物を含むソース/ドレイン領域150とを備える。素子形成領域170のうちゲート電極の両側方に位置する領域には、半導体基板101の主面に対して傾いた半導体単結晶のファセット面を露出させる側壁を有し、コーナー部が丸められたリセス130が形成されており、ソース/ドレイン領域150は、リセス130に埋め込まれたシリコン混晶で構成されている。

(もっと読む)

半導体装置の製造方法

【課題】 置換ゲート工程で発生する不良を防止できる半導体装置の製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体基板上にゲート絶縁膜および犠牲ゲート電極を含むゲートパターンを形成する段階、前記半導体基板および前記ゲートパターン上にエッチング停止層および絶縁層を形成する段階、前記エッチング停止層が露出するまで前記絶縁層を除去する段階、前記犠牲ゲート電極が露出するまで前記エッチング停止層をエッチバックする段階、前記犠牲ゲート電極を除去し、結果物の全体構造の上面に金属層を形成する段階、前記絶縁層が露出するまで前記金属層を除去する段階、および前記金属層を所定の深さでエッチバックする段階を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

201 - 220 / 1,528

[ Back to top ]