Fターム[5F140BG14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁構造及び配置 (6,762) | ゲート側壁材料 (3,458) | SiN (1,528)

Fターム[5F140BG14]に分類される特許

141 - 160 / 1,528

半導体装置およびその製造方法

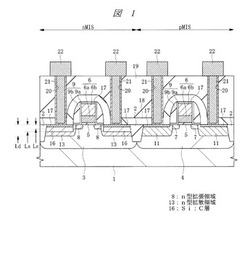

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの新規な閾値電圧制御技術を提供する。

【解決手段】半導体装置の製造方法は、半導体基板のp型領域上に、ゲート絶縁膜を形成する工程と、ゲート絶縁膜上に、化学量論組成よりも酸素量の少ない酸化アルミニウム膜を形成する工程と、酸化アルミニウム膜上に、タンタルと窒素とを含むタンタル窒素含有膜を形成する工程と、タンタル窒素含有膜上に、導電膜を形成する工程と、導電膜をパターニングして、ゲート電極を形成する工程と、ゲート電極をマスクとして、p型領域にn型不純物を注入する工程と、タンタル窒素含有膜の形成後に、熱処理を行う工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】イオン注入により半導体基板1にエクステンション領域EXを形成してから、ゲート電極GEの側壁上にサイドウォールスペーサSWを形成し、その後、イオン注入により半導体基板1にソース・ドレイン領域SDを形成する。サイドウォールスペーサSWを形成するには、半導体基板1上にゲート電極GEを覆うように絶縁膜6を形成してから、この絶縁膜6を異方性エッチングし、その後、半導体基板1上にゲート電極GEを覆うように絶縁膜7を形成してから、この絶縁膜7を異方性エッチングすることで、ゲート電極GEの側壁上に残存する絶縁膜6,7からなるサイドウォールスペーサSWを形成する。絶縁膜6のエッチング工程では、絶縁膜6をアンダーエッチングまたはジャストエッチングし、絶縁膜7のエッチング工程では、絶縁膜7をオーバーエッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

ポータブル電気素子およびデータ処理センタのための低電圧MOSFETを形成する半導体素子および方法

【課題】半導体素子を提供すること。

【解決手段】半導体素子であって、基板と、該基板内に形成された井戸領域と、該基板の表面の上方に形成されたゲート構造と、該ゲート構造に隣接して基板内に形成されたソース領域と、該ソース領域の反対側に該ゲート構造に隣接して該基板内に形成されたドレイン領域と、該ソース領域を通して形成されたトレンチと、該トレンチを通して形成されたプラグと、該トレンチを通して該プラグの上方に形成されたソースタイと、該ソース領域、該ドレイン領域、および該ゲート構造の上方に形成された相互接続構造とを備える、半導体素子。

(もっと読む)

拡散防止膜の形成方法及び半導体装置の製造方法

【課題】 拡散防止膜の形成方法及び半導体装置の製造方法に関し、閾値調整元素の拡散等による閾値電圧の変動の防止と製造工程の簡素化を両立する。

【解決手段】 Siを含有しない高誘電率酸化膜に窒素を導入したのち第1加熱処理を行う工程と、前記窒素を導入したSiを含有しない高誘電率酸化膜の上にSi含有半導体層を堆積させる工程と、第2加熱処理によって前記Si含有半導体層中のSiを前記窒素を導入したSiを含有しない高誘電率酸化膜中に拡散する工程とを設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電材料のゲートトレンチへの埋め込みが容易な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上の絶縁膜と、絶縁膜に設けられた凹部と、凹部の底部であって半導体基板上に設けられたゲート絶縁膜とを形成する工程と、凹部の内壁面上と絶縁膜の上面上に、第1金属を含む導電材料で第1ゲート電極膜を形成する工程と、第1ゲート電極膜上に、凹部の側面部分の一部は覆わないように、導電材料の融点よりも高い融点を持つ材料でカバー膜を形成する工程と、カバー膜が形成された状態で、熱処理を行って、第1ゲート電極膜をリフローさせる工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】調整用金属を含む高誘電率膜を有するゲート絶縁膜を備えたMISトランジスタを有する半導体装置において、MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、MISトランジスタnTrを備えている。MISトランジスタは、半導体基板10における素子分離領域11に囲まれた活性領域10aと、活性領域及び素子分離領域上に形成され、高誘電率膜15aを有するゲート絶縁膜16aと、ゲート絶縁膜上に形成されたゲート電極19aとを備えている。ゲート絶縁膜における素子分離領域上に位置する部分のうち、少なくとも一部分には、窒化領域20x,20yが設けられている。窒化領域20x,20yに含まれる窒素の窒素濃度をn1,n2とし、ゲート絶縁膜における活性領域上に位置する部分に含まれる窒素の窒素濃度をnとしたとき、n1>n、且つ、n2>nの関係式が成り立っている。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置の製造方法

【課題】希土類金属を含有するHigh-k膜のエッチング残渣を抑制するための半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に絶縁膜4を形成する工程と、絶縁膜4の上に希土類元素含有酸化膜7、12を形成する工程と、フッ酸、塩酸、硫酸を含む薬液により希土類元素含有酸化膜7、12をエッチングする工程とを有し、これにより希土類元素含有酸化膜7、12のエッチングを良好に行う。

(もっと読む)

半導体装置およびその製造方法

【課題】MOSトランジスタのソース及びドレイン電極に生じる寄生容量を低減する。高速動作が可能な半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタを備える。MOSトランジスタは、1対の第1、第2及び第3の不純物拡散領域を有する。第2の不純物拡散領域は、第1の不純物拡散領域を挟むように半導体基板内に設けられた第1導電型の不純物拡散領域であり、第1の不純物拡散領域よりも第1導電型の不純物濃度が高くなる。第3の不純物拡散領域は、1対の第1の不純物拡散領域に接すると共に第2の不純物拡散領域に接しないように、半導体基板内に設けられた第2導電型の不純物拡散領域である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】金属酸化膜または金属シリケート膜を含む薄膜ゲート絶縁膜を有する半導体装置の製造方法において、VFBを十分に制御し、Vthを十分に制御すること。

【解決手段】基板1上に、第1の金属の酸化膜、または、第1の金属のシリケート膜からなる第1高誘電率ゲート絶縁膜5を形成する第1工程と、第1高誘電率ゲート絶縁膜5上に、第2の金属の酸化膜からなる第2高誘電率ゲート絶縁膜6を形成する第2工程と、第2高誘電率ゲート絶縁膜6上に、ゲート電極膜7を形成する第3工程と、を有し、前記第2工程では、第2の金属元素および炭化水素基からなる主原料と、溶媒材料と、を混合した混合材料を用いて、原子層蒸着法により第2高誘電率ゲート絶縁膜6を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性に優れた半導体装置が得られる製造方法を提供する。

【解決手段】半導体装置の製造方法は、p型電界効果トランジスタおよびn型電界効果トランジスタを備える半導体装置の製造方法であって、基板上に、界面絶縁層および高誘電率層をこの順で形成する工程と、高誘電率層上に、犠牲層のパターンを形成する工程と、犠牲層が形成されている第1の領域の高誘電率層上および犠牲層が形成されていない第2の領域の高誘電率層上に、金属元素を含む金属含有膜を形成する工程と、熱処理を行うことにより、第2の領域における界面絶縁層と高誘電率層との界面に金属元素を導入する工程と、犠牲層をウエットエッチングにより除去する工程と、を含み、除去する工程において、犠牲層は、高誘電率層よりもエッチングされやすい。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にHK絶縁膜を用いたMIS構造の半導体装置において、HK絶縁膜端部近傍における酸素過剰領域の発生に起因するトランジスタ特性の劣化を防止する。

【解決手段】半導体基板100上にゲート絶縁膜108a、108bを介してゲート電極109a、109bが形成されている。ゲート電極109a、109bの側面上に導電性酸化物からなるサイドウォールスペーサ111a、111bが形成されている。

(もっと読む)

半導体装置の製造方法

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加するシリコン混晶層を活性領域に設けた半導体装置において、電流駆動能力の向上とリーク電流の低下と図れるようにする。

【解決手段】半導体装置は、シリコンからなる半導体基板10に形成され、周囲を素子分離領域11により囲まれてなる第2の活性領域10bと、該第2の活性領域10b及び素子分離領域11の上に、ゲート絶縁膜13を介在させて形成されたゲート電極14とを有している。第2の活性領域10bには、ゲート電極14の両側方の領域が掘り込まれてなるリセス領域19cにp型シリコン混晶層21が形成されており、該p型シリコン混晶層21における素子分離領域11と接触する接触位置の上端21bは、第2の活性領域10bの上面におけるゲート絶縁膜13の下側部分よりも低い。

(もっと読む)

141 - 160 / 1,528

[ Back to top ]