Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

121 - 140 / 722

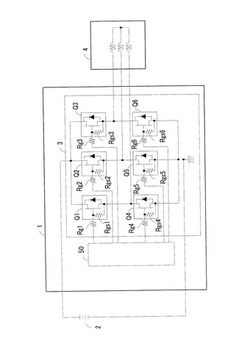

モータ駆動装置

【課題】モータ駆動装置内で駆動信号経路のオープン故障が発生した場合にも、モータ駆動回路のトランジスタを安全、確実にオフ状態とする。

【解決手段】モータ駆動回路3のトランジスタQ1〜Q6に駆動信号を供給してトランジスタをオン・オフ制御するトランジスタ駆動回路5を備えたモータ駆動装置において、トランジスタQ1〜Q6のゲート・ソース間(またはベース・エミッタ間)に、トランジスタ駆動回路5からトランジスタQ1〜Q6への駆動信号経路上にオープン故障が発生した場合に、トランジスタQ1〜Q6をオフさせるための抵抗体Rgs及び/又はコンデンサCgsを接続すると共に、抵抗体、コンデンサをトランジスタの内部に配置したもの。

(もっと読む)

フィルタ回路およびそれを用いた照明装置

【課題】コンバータで発生するスイッチングノイズが伝導および輻射するのを抑制可能なフィルタ回路およびそれを用いた照明装置を提供する。

【解決手段】コンバータ44とコンバータ44の入力側の電源あるいは出力側の負荷42との間に設けられるフィルタ回路43であって、高電位側のラインに第1のインダクタL9が設けられるとともに、低電位側のラインに第2のインダクタL10が設けられ、第1のインダクタL9と第2のインダクタL10とのインダクタンス値がそれぞれ異なる。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流が検出された場合に、ハイサイドスイッチだけでなくハイサイドスイッチに接続される回路を保護することが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ゲート電圧降圧部31は、過電流検出部20からの電流制限信号に応じて、MOSトランジスタ15のゲート電圧を第1の電圧から、第1の電圧と第2の電圧との間の第3の電圧まで、第1の時間変化率で低下させる。これによりMOSトランジスタ15のオン抵抗がMOSトランジスタ15の完全オン時のオン抵抗より高くなる。ゲート電圧降圧部32は、ゲート電圧が第3の電圧に達した後に、ゲート電圧を第3の電圧から第2の電圧まで第2の時間変化率で低下させる。第1の時間変化率は、第2の時間変化率よりも大きい。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流の検出精度を高めることが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ハイサイドスイッチ回路10は、入力端子11と出力端子12との間に電気的に接続されるスイッチ(MOSトランジスタ15)と、ゲート制御部16と、過電流検出部20とを備える。過電流検出部20は、抵抗素子21と、比較器22とを含む。比較器22は、抵抗素子21の電圧V1がしきい電圧を超える場合に、過電流を検出する。比較器22は、過電流時の検出電圧V1がしきい電圧を上回るように、予め調整される。抵抗素子21の抵抗値の精度が高くない場合にも、比較器22の調整によって、過電流の検出精度が高められる。

(もっと読む)

電子装置

【課題】駆動信号がスイッチング素子のオフを指示しているにもかかわらず、制御端子の電圧が低下せず、スイッチング素子をオフできない場合であっても、スイッチング素子の熱破壊を防止できる電子装置を提供する。

【解決手段】制御回路は、正常時に、オン駆動用FET121aがオフするタイミング(t6)、オフ駆動用FET122aがオンするタイミング(t7)、及び、オン保持用FET123aがオンするタイミング(t9)の後であって、駆動信号がIGBT110dのオン指示からオフ指示に切替わるタイミング(t5)から一定の時間Toffの経過後に、オン保持用FET123aをオンする(t10)。そのため、オン駆動用FET121aがオン故障し、駆動信号がIGBT110dのオフを指示しているにもかかわらずIGBT110dをオフできない異常状態であっても、IGBT110dを確実にオフできる。従って、IGBT110dの熱破壊を防止できる。

(もっと読む)

射出成形機及び電力用半導体素子消耗度監視システム

【課題】電力変換装置における電力用半導体素子の消耗度をより正確に且つより低い演算負荷で監視する電力用半導体素子消耗度監視システムを備える射出成形機を提供すること。

【解決手段】電力変換装置10における電力用半導体素子の消耗度を監視する電力用半導体素子消耗度監視システム100を備える射出成形機は、電力変換装置10の運転状態が予め設定された複数の運転パターンの何れに該当するかを判定する運転状態判定部451と、それら複数の運転パターンのそれぞれが実行された場合のその電力用半導体素子の消耗度を予め記憶する消耗度参照テーブル460と、消耗度参照テーブル460を参照して、運転状態判定部451が判定した運転パターンが実行された場合のその電力用半導体素子の消耗度を取得して積算する消耗度積算部452と、を備える。

(もっと読む)

保護回路

【課題】より効果的に逆起電圧の発生を抑え、過電圧による素子の破壊を防ぐことが可能な保護回路を提供する。

【解決手段】第1の実施形態の保護回路2は、抵抗値可変スイッチ10,過電流検出部20,制御電圧印加部30,容量部40,制御端子電圧変更部50および外部端子11を備える。抵抗値可変スイッチ10は、制御端子10a,第1端子10bおよび第2端子10cを有する。制御端子電圧変更部50は、抵抗値可変スイッチ10の制御端子10aと基準電位端子との間に直列的に設けられたスイッチ51および抵抗器52を含む。

(もっと読む)

プリドライバ回路、および、駆動回路

【課題】回生電流がモータ等の負荷から駆動回路を構成するプリドライバ回路側に流れても、駆動回路の制御に影響を与えないようにすること。

【解決手段】第1の電源電圧(VM)に接続された第1の駆動トランジスタと、接地に接続された第2の駆動トランジスタとの間の負荷に接続される接続ノード(N1)を出力端子とするブリッジ回路に接続されたプリドライバ回路において、接続ノード(N1)である出力端子に接続された出力モニタ回路を有し、該出力モニタ回路を用いて、出力端子に現れる電圧(Vout)に基づいて電圧のみをフィードバックさせる第1のフィードバック信号(S1)を生成し、第1のフィードバック信号(S1)に基づいて第2のフィードバック信号(S2)を生成して、出力端子に現れる電圧(Vout)が第1の電源電圧(VM)に近づくように、第1の駆動トランジスタを駆動制御する。

(もっと読む)

誘導性負荷駆動装置

【課題】電源回路における回路素子の破壊を防止することが可能な誘導性負荷駆動装置を提供する。

【解決手段】誘導性負荷駆動装置の構成として、電源回路の出力端子と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源回路の出力端子に回生させる逆起電流回生回路と、前記電源回路の出力電圧が予め設定された閾値以上となった場合に、前記第2のスイッチング素子をオンにする回路素子保護回路と、を備えた構成を採用する。

(もっと読む)

電子装置

【課題】スイッチング素子をオフするように制御しているにもかかわらず、オフできない異常状態を検出することができる電子装置を提供する。

【解決手段】IGBT110dに流れる電流が電流閾値より大きくなると、電流検出回路125は、IGBT110dに電流が流れていると判断する。制御回路128は、駆動信号がIGBT110dのオフを指示しているにもかかわらず、電流検出回路125がIGBT110dに電流が流れていると判断すると、IGBT110dをオフできない異常状態にあると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、駆動信号がIGBT110dのオフを指示しているにもかかわらず、IGBT110dをオフできない異常状態を検出することができ、IGBT110dの熱破壊を防止できる。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子がオン故障等した場合であっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】オン駆動用抵抗121bとオフ駆動用抵抗122bの抵抗値は、オン駆動用FET121aとオフ駆動用FET122aがともにオンした場合に、IGBT110dのゲート電圧が、オン電圧が増加するオン、オフの閾値電圧付近の所定範囲外であって、オン、オフの閾値電圧より低くなるように設定されている。そのため、オン駆動用FET121aがオン故障等したときにオフ駆動用FET122aがオンしても、オン電圧が増加してIGBT110dの発熱が増大することなく、IGBT110dをオフすることができる。従って、IGBT110dの熱破壊を防止することができる。

(もっと読む)

レベルシフト回路及びそれを用いたスイッチングレギュレータ

【課題】電源電圧を高くしてもトランジスタのゲート耐圧を上げる必要がなく、低電源電圧から高電源電圧まで広範囲に使用できるレベルシフト回路を提供する。

【解決手段】レベルシフトトランジスタ105は、入力トランジスタ101と負荷トランジスタ103との間に、レベルシフトトランジスタ106は、入力トランジスタ102と負荷トランジスタ104との間にそれぞれ接続される。レベルシフトトランジスタ105,106の各ゲートGは共通接続され、その共通接続点にはレベルシフト電圧生成回路120で生成されたレベルシフト電圧Vscが電圧源V1の大きさに応動して印加される。負荷トランジスタ103,104のソース−ゲート間に印加される電圧VSGは、レベルシフト電圧Vscによって、電圧源V1が増減してもほぼ一定になるように設定される。これにより、負荷トランジスタ103,104を低耐圧のトランジスタで構成することができる。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子がオン故障してスイッチング素子をオフできない異常状態になっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】制御回路128は、オン駆動用FET121aのゲート電圧がオンしない電圧であるにもかかわらず、ドレイン−ソース間電圧がオンした際の電圧であるとき、オン駆動用FET121aがオン故障していると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、オン駆動用FET121aがオン故障してIGBT110dをオフできない異常状態になっても、IGBT110dの熱破壊を防止できる。

(もっと読む)

駆動装置

【課題】消費電力を低減した駆動装置を提供する。

【解決手段】コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備えた駆動装置である。

(もっと読む)

ゲート駆動回路及びゲート駆動方法

【課題】トランジスタの駆動電力の損失を防ぎ且つスイッチング時間の高速化を図る。

【解決手段】接合型トランジスタ2の駆動に必要な基準駆動能力レベル電圧からなる基準波形Sg′及び駆動能力のより高い高駆動能力レベル電圧からなる重畳パルスSpを生成し、重畳パルスSpのパルス幅を、接合型トランジスタ2のスイッチング時間に、若しくはドレイン電位VDの遷移収束タイミングを表す閾値により設定する。基準波形Sg′と重畳パルスSpとを重畳しこれを、接合型トランジスタ2のゲート駆動信号Sgとする。ゲート駆動信号Sgは、接合型トランジスタ2の遷移終了とみなすことの可能なタイミングで基準駆動能力レベル電圧に切り換わることになるため、遷移終了後も高駆動能力レベル電圧で駆動されることにより、接合型トランジスタ2に形成されるダイオードに順方向電流が流れることに伴う電力損失の発生を回避することができる。

(もっと読む)

双方向スイッチおよびそれを用いたスイッチ回路

【課題】高耐圧の双方向スイッチを小型化する技術を提供する。

【解決手段】MOSFETを用いた双方向スイッチにおいて、MOSFETのソース端子とバックゲート端子間を、トランスファゲートTGを介して接続する。MOSFETのバッグゲート端子とトランスファゲートTG間の接続点と、グラウンド電位(上記MOSFETがnチャネルの場合)または電源電位(上記MOSFETがpチャネルの場合)との間にスイッチを用いてもよい。

(もっと読む)

電圧駆動型素子を駆動する駆動装置

【課題】出力電圧の異なる複数の電源を備えた、電圧駆動型素子を駆動する駆動装置で、駆動電源と電圧駆動型素子との接続部の電圧降下を抑制する。

【解決手段】 駆動装置の駆動電源は、複数の直流電源を備えており、複数の直流電源のうち、最も出力電圧の絶対値が大きい第1直流電源は、第1スイッチング素子を介して接続部と接続しており、複数の直流電源のうち、第1直流電源よりも出力電圧の絶対値が小さい1つ以上の第2直流電源の各々は、第2スイッチング素子および電流低減素子を介して接続部と接続している。第1スイッチング素子および第2スイッチング素子のそれぞれは、対応する直流電源と接続部とを導通状態と非導通状態とに切替えると共に、導通状態としたときに流れる電流と逆方向の電流の向きを順方向とする寄生ダイオードを有する半導体素子である。

(もっと読む)

ドライブ回路

【課題】1個のデッドタイム生成回路を用いて、直列に接続されている2つのスイッチング素子を駆動する2系統の信号のそれぞれ対してデッドタイムを設けることができ、IC化した場合に外付けコンデンサを1個にすることができるドライブ回路を提供する。

【解決手段】

コンデンサ13aを用いて信号Va0をデッドタイムよりも短い時間遅延させる遅延回路2aと、コンデンサ13bを用いて信号Vb0をデッドタイムよりも短い時間遅延させる遅延回路2bと、コンデンサ23を用い、信号Va0および信号Vb0の立ち上がりのタイミングからデットタイム分遅延させたタイミングで立ち上がる周期T/2のデッドタイム生成用信号V6を生成するデッドタイム生成回路3と、デッドタイム生成用信号V6に基づいてデッドタイムが設けられた信号Va7および信号Vb7とを生成するAND回路17a、17bとを設ける。

(もっと読む)

半導体素子の駆動回路

【課題】負電位の印加により導通状態となるノーマリーオン型の半導体素子の駆動に適した駆動回路を、専用の電源を用いずに実現すること。

【解決手段】給電ラインA上のpチャネル型FETによる高速スイッチング素子Sのソース電位Vsを降圧用抵抗R1により降圧させた駆動信号VGoを、降圧用抵抗R1と接地電位ラインBとの間に接続したnMOSFET5のオン時に、高速スイッチング素子SのゲートGに出力する。nMOSFET5は、給電ラインAの電圧(高速スイッチング素子Sよりも交流成分を含む直流電圧Viの入力側の電位)を用いて補助駆動回路7のマイクロコンピュータが生成したスイッチング用の駆動信号VGiによりオンオフされる。マイクロコンピュータは、給電ラインAの交流成分を含む直流電圧Viから生成した定電圧により作動する。したがって、高速スイッチング素子Sのスイッチングに専用の電源が不要となる。

(もっと読む)

絶縁ゲート型デバイスの駆動回路

【課題】通常動作への影響(消費電流やRon)を低減しつつ、デバイスの誤オンの防止と高速ターンオフとを実現することができる絶縁ゲート型デバイスの駆動回路を提供する。

【解決手段】パワーMOSFET8のゲート−ソース間にパワーMOSFET8のゲート電圧を下げるためのゲート電圧制御用MOSFET14を設け、ゲート電圧制御用MOSFET14のゲート−ドレイン間にプルアップ素子としてN型デプレッションMOSFET25を設ける。そして、N型デプレッションMOSFET25を、パワーMOSFET8のドレイン電圧Vdが急激に持ち上げられたときに発生する、パワーMOSFET8のゲート−ドレイン間の寄生容量Cgdの充電電流Irによって駆動されるように構成する。

(もっと読む)

121 - 140 / 722

[ Back to top ]