Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

101 - 120 / 722

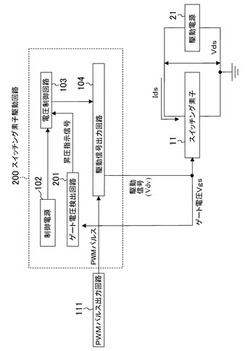

スイッチング素子駆動回路

【課題】スイッチング素子駆動回路において、スイッチング素子のスイッチング損失を抑制する。

【解決手段】 ゲート電圧検出回路201は、スイッチング素子11のゲート電圧Vgsを検出し、このゲート電圧がスイッチング素子11の閾値電圧未満に設定された所定電圧未満のとき、Hレベルの昇圧指示信号を出力する。電圧制御回路103は、前記昇圧指示信号がLレベルの間は、制御電源102の所定電圧V1をそのまま出力し、前記昇圧指示信号がHレベルの間は、前記所定電圧V1を昇圧した電圧V2を出力する。駆動信号出力回路104は、PWMパルス出力回路111から出力されるPWMパルスの電圧を電圧制御回路103から出力される電圧に増幅する。従って、駆動信号出力回路104からスイッチング素子11への駆動信号は、前記PWMパルスがHレベルになった時に、先ず昇圧された電圧V2となり、スイッチング素子11のゲート電圧Vgsが所定電圧にまで上昇すると、所定電圧V1となる。

(もっと読む)

負荷制御装置

【課題】駆動回路の消費電力を小さく抑えることが可能な負荷制御装置を提供する。

【解決手段】駆動回路20は、双方向スイッチ10にゲート電圧Vg1,Vg2を印加するゲート駆動部21と、ゲート駆動部21の動作を制御する制御部22とを有している。さらに駆動回路20は、双方向スイッチ10にゲート端子から流れ込むゲート電流Ig1,Ig2を検出する電流検出部40を有しており、電流検出部40の検出値が制御部22へ入力される。制御部22は、外部から入力されるオンオフ信号と、電流検出部40から入力される検出値との両方に基づいて、ゲート駆動部21に与える駆動信号を決定する。ここで、制御部22は、オンオフ信号が「H」の期間において、低電位側のゲート電流Ig1,Ig2が小さくなるほどゲート電圧Vg1,Vg2が大きくなるように、ゲート駆動部21に与える駆動信号を調節する。

(もっと読む)

駆動回路

【課題】電圧駆動型素子のスイッチング特性におけるトレードオフ関係を改善する駆動回路を提供すること。

【解決手段】駆動回路1は、ゲート抵抗R1とそのゲート抵抗R1に対して並列に接続されている分岐回路部23を備えている。分岐回路部23は、分岐ゲート抵抗R3とツェナーダイオードZD1を有するとともに、分岐ゲート抵抗R3とツェナーダイオードZD1が直列に接続されている。ツェナーダイオードZD1のカソードが駆動電源V1の正極端子14側に接続されており、ツェナーダイオードZD1のアノードがトランジスタTr1の制御端子12側に接続されている。

(もっと読む)

電圧駆動型スイッチングデバイスの駆動回路

【課題】ターンオン時のゲート電流を所望の電流値に高精度に設定でき、スイッチング損失の低減が可能な電圧駆動型スイッチングデバイスの駆動回路を得る。

【解決手段】IGBT1のゲート端子に接続され、駆動用パルス信号2のオン/オフゲート制御信号に基づき、IGBT1をターンオン/ターンオフさせるゲート信号を前記ゲート端子に出力するゲート駆動定電流回路が示されている。このゲート駆動定電流回路は、正電源3とGND電位4間に直列に接続された第1の抵抗5と第1のトランジスタ15と第2の抵抗6と制御信号伝達トランジスタ7、および正電源3とIGBT1のゲート端子間に直列に接続されたゲートオン抵抗8と定電流出力トランジスタ9を備え、第1のトランジスタ15のベース端子は第1のトランジスタ15のコレクタ端子と短絡接続されている。

(もっと読む)

負荷駆動回路

【課題】ブリッジ回路を構成する一対のMOSFETの内蔵ダイオードに流れる負荷電流の逆回復を速くする。

【解決手段】ブリッジ回路3は内蔵ダイオード4a、5aを内蔵したMOSFET4、5により構成される。MOSFET4、5はスイッチング制御回路6によりゲート駆動回路7、8を介して駆動制御される。負荷電流ILがコイル1からブリッジ回路に向けて流れる状態であって、例えば内蔵ダイオード4aを介して環流電流を流す状態からMOSFET5を介して負荷電流を流す状態への移行期間の終盤にMOSFET4をオンして内蔵ダイオード4aをオフさせ、電流I1がゼロ相当になったらMOSFET4をオフ、MOSFET5をクランプ状態で一定時間オンする。その後、MOSFET5を通常のオン状態に移行させる。

(もっと読む)

レベルシフト回路およびスイッチング電源装置

【課題】 高耐圧プロセスを使用することなく、回路的に高耐圧化したレベルシフト回路を実現できるようにする。

【解決手段】 一対のCMOSインバータを有し一方のインバータの出力ノードを他方のインバータのPチャネル型MOSトランジスタのゲート端子に交差結合してなるラッチ回路(22)と、該ラッチ回路のいずれか一方の出力ノードに接続されたCMOSインバータからなる出力段(23)とを有するレベルシフト回路において、ラッチ回路を構成する一対のCMOSインバータの各Pチャネル型のMOSトランジスタ(Mp1,Mp2)とNチャネル型のMOSトランジスタ(Mn1,Mn2)との間に、ゲート端子が電源電圧と接地電位の中間の電位が印加される第3電圧端子(FGND)に接続されたPチャネル型のMOSトランジスタ(Mp4,Mp5)をそれぞれ直列形態で設けた。

(もっと読む)

スイッチングトランジスタ駆動回路

【課題】スイッチング制御回路から出力される制御信号のハイレベル電圧が電界効果トランジスタをスイッチング駆動するのに十分なレベルに満たない場合でも、少ない部品の簡単な回路で駆動できるスイッチングトランジスタ駆動回路を提供する。

【解決手段】電圧Vin1(=V1+Vα)が印加された入力端子にソース端子が接続されたPチャネル型FET12と、一端がFET12のソース端子に接続され且つ他端がFET12のゲート端子に接続された抵抗器14と、ツェナー電圧Vzが電圧Vα以上であるツェナーダイオード15とを備え、ツェナーダイオード15のアノード端子をスイッチング制御IC11の制御信号出力端子(Drive)に接続し、ツェナーダイオード15のカソード端子をPチャネル型FET12のゲート端子に接続する。

(もっと読む)

負荷制御装置

【課題】過電流を検出する機能や過電流から出力スイッチング素子を保護する機能を備えた負荷制御装置を提供する。

【解決手段】スイッチングレギュレータ60から電力が供給されて少なくとも一つの負荷71、72に供給する出力電流I1、I2を制御する負荷制御装置1で、負荷に接続されて出力制御信号に応じて負荷に出力電流を供給するときに導通する出力スイッチング素子21、22と、出力電流が過電流であることに起因してスイッチングレギュレータの出力電圧値が所定電圧値を下回ったことを検出したとき、所定時間に亘り出力スイッチング素子を非通電状態に制御する出力スイッチング素子制御手段11、12、40とを備える。

(もっと読む)

負荷駆動装置

【課題】スイッチング素子の立ち上がりの速度を高速に維持しつつ、スイッチング素子を駆動するドライバ回路の消費電流を削減することができる負荷駆動装置を提供する。

【解決手段】負荷10に接続されるスイッチング素子50と、定電流を生成する定電流生成部30と、定電流生成部30から流れ込む定電流の大きさに応じたオン時間でスイッチング素子50をオンするドライバ回路40と、を備えた構成とする。そして、定電流生成部30は、スイッチング素子50がオンするオン時間に達するまではドライバ回路40に第1電流量の大きさの定電流を流すことでスイッチング素子50の立ち上がりの速度を高速に維持する。また、定電流生成部30は、スイッチング素子50がオンするオン時間が経過した後はドライバ回路40に第1電流量よりも小さい第2電流量の定電流を流すことでドライバ回路40の消費電流を削減する。

(もっと読む)

ゲート駆動回路

【課題】ゲート駆動信号を電源用トランスによって適切に伝達することができるゲート駆動回路を提供する。

【解決手段】ゲート駆動信号を電源用トランス2により絶縁伝達するゲート駆動回路1であって、一次側電圧の駆動タイミングを生成するタイミング生成部4と、駆動タイミングに基づいて一次側電圧を出力するトランス駆動回路部3と、二次側電圧に含まれるパターン信号でゲート駆動信号を検出するパターン検出部6及びフリップフロップ回路部8とを備え、タイミング生成部4は、ゲート駆動信号を時間T1だけ遅延させ、ゲート駆動信号の極性反転タイミングから時間T1経過までの期間は一次側電圧VT1の極性反転を禁止し、時間T1経過直後にゲート駆動信号に応じて時間T1よりも短い時間幅T2,T3をもつパルス状極性反転を有するパターン信号が一次側電圧VT1に含まれるように駆動タイミングを生成する。

(もっと読む)

負荷駆動装置

【課題】 負荷への通電を妨げることなく、昇圧した電圧が低下することを防止することができる負荷駆動装置を提供する。

【解決手段】 複数相の駆動回路のうちの少なくとも2相間において昇圧用コンデンサ47,67と第3の電源45,65との接続部に設けられ、昇圧された電圧が出力される昇圧電源端子10,13同士の電気的な接続または遮断を選択する少なくとも1つのスイッチ回路102と、少なくとも1つのスイッチ回路102を制御する少なくとも1つのスイッチ制御回路110とを備えている。

(もっと読む)

ゲート駆動回路

【課題】ゲート駆動信号の伝達遅延時間のばらつきを低減することができるゲート駆動回路を提供する。

【解決手段】ゲート駆動回路1は、トランス2を駆動するトランス駆動回路部3と、トランス2の一次側の駆動タイミングを生成すると共に、入力ゲート駆動信号のON状態時とOFF状態時とでトランス2の一次側駆動電圧変化率を異なるように設定するタイミング生成部4と、トランス2の二次側電圧を微分することで、トランス2の二次側電圧変化率を検出する微分回路部5と、入力ゲート駆動信号のOFF状態時の微分値レベルを検出するレベル検出回路部6と、入力ゲート駆動信号のON状態時の微分値レベルを検出するレベル検出回路部7と、検出レベル検出回路部6,7と接続されたR端子及びS端子を有し、出力ゲート駆動信号を生成・保持するフリップフロップ回路部8とを有している。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

ゲート駆動用電源装置およびインバータ制御回路

【課題】個別の電源回路の出力毎にトランスを配置するとともに、それぞれの制御回路を一つにまとめることで部品点数を少なくしたゲート駆動用電源装置を提供する。

【解決手段】各ゲート駆動回路21〜26には、いずれも電源端子101,102から、それぞれ個別のトランスT1〜T6を介して1次電源入力が供給されている。また、トランスT1〜T6の1次巻線の1端は、いずれも電源ライン31,32により電源端子101と接続される。さらに、1次巻線の他端は、共通する渡り線33,34によって互いに結線され、その巻線電流を制御するためのMOSFET27のドレイン端子に接続されている。トランスT2の補助巻線によって検出された出力電圧がフィードバックされるゲート電源制御回路28が、MOSFET27をオンオフ制御するデューティ比を制御している。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線Npと第1の二次巻線S1と第1の二次巻線の極性とは逆極性を持つ第2の二次巻線を有する2以上の二次巻線とを有し一次巻線に駆動信号が印加されるトランスDT1、第1の二次巻線からの信号によりオンオフ制御される第1スイッチング素子Qh、第2の二次巻線からの信号によりオンオフ制御される第2スイッチング素子Ql、第1の二次巻線の一端と第1スイッチング素子の制御端子との間に接続され第1スイッチング素子を駆動する第1駆動部Q11,Q12、第2の二次巻線の一端と第2スイッチング素子の制御端子との間に接続され第2スイッチング素子を駆動する第2駆動部Q21,Q22、第1の二次巻線電圧を倍電圧整流平滑して第1駆動部に供給する倍電圧整流平滑回路D11,D12,C11,C12、第2の二次巻線電圧を倍電圧整流平滑して第2駆動部に供給する倍電圧整流平滑回路D21,D22,C21,C22を有する。

(もっと読む)

スイッチング回路、ハーフブリッジ回路および三相インバータ回路

【課題】リカバリサージ電圧の発生を抑制することにより素子破壊を防ぐ、スイッチング回路、ハーフブリッジ回路および三相インバータ回路提供すること。

【解決手段】回路開閉端子と制御信号用端子とボディダイオードとを有する第1および第2のスイッチング素子が逆直列に接続された直列回路と、直列回路に第1のスイッチング素子のボディダイオードと同じ導通方向で並列に接続された外付けダイオードと、第1のスイッチング素子に流れる電流方向を検出する電流検出回路と、電流検出回路で検出した電流方向が第1のスイッチング素子のボディダイオードに対して順方向に流れる場合には第1および第2のスイッチング素子を閉制御し、電流検出回路で検出した電流方向が第1のスイッチング素子のボディダイオードに対して逆方向に流れる場合には第1および第2のスイッチング素子をゲート信号に基づいて開閉制御する制御手段とを備える。

(もっと読む)

電力用半導体装置及びその動作方法

【課題】電力用半導体装置がOFF状態の時に電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止する。

【解決手段】本発明の電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

(もっと読む)

ドライバ回路

【課題】 絶縁電源を別に設けることなくハイサイド側の回路に負のゲート電圧を供給することが可能なゲートドライバ回路を実現する。

【解決手段】

第1トランジスタ21と第2トランジスタが直列に接続されたハーフブリッジ回路において、ハイサイド側の第1トランジスタ21に負のゲート電圧を第1の制御回路11を介して供給するためのコンデンサ13、及び、ローサイド側の第2トランジスタ22に負のゲート電圧を第2の制御回路12を介して供給するための制御回路電源14を備え、コンデンサ13の一端をスイッチ素子30を介して制御回路電源14の−端子側の負電圧VEEと接続し、他端を出力端子4の電圧と接続するように構成したドライバ回路1であって、スイッチ素子30は、第2トランジスタ22がオン状態となるタイミングでオンされるように制御される。

(もっと読む)

情報処理装置、これを用いたモータ駆動装置、及び、情報処理方法

【課題】 上下アームのスイッチング素子を駆動するとともに、上下アームの異常を検出して異常信号を出力するゲート駆動回路を備える情報処理装置において、異常信号の通知機能が正常であるか否かを判定する。

【解決手段】 情報処理装置(ECU)において、ブートストラップ式のゲート駆動回路は、ゲート駆動の開始前に、通常駆動時ならば先に下アーム駆動信号を出力すべきところ先に上アーム駆動信号D1を出力し(S10)、ダミー異常信号Edを意図的に発生させる(S20)。ここで異常信号通知機能が正常であれば、ダミー異常信号Edは、異常信号出力部から出力され、異常信号線を経由して伝達され、異常信号受信部に受信される。そこで、異常信号受信部がダミー異常信号Edを受信したか否かを確認することで、異常信号通知機能が正常であるか否かを判定する(S30)ことができる。

(もっと読む)

ドライバ回路、及び、インバータ回路

【課題】 ノーマリーオン型のスイッチング素子を用いてハーフブリッジ回路を構成し、ドライバ回路もしくはインバータ回路として使用する場合のアーム短絡を防止し、安全な回路を提供する。

【解決手段】

入出力端子対の一端が高圧側の第1の電源電圧V1に接続する第1のスイッチング素子14と第2のスイッチング素子15とが直列に接続されたハーフブリッジ回路において、第2のスイッチング素子15と低圧側の第2の電源電圧V2の間にノーマリーオフ型の第3のスイッチング素子16を挿入したドライバ回路であり、第3のスイッチング素子16は、制御回路用電源13a,13bにより供給される動作電圧VH又はVLが制御回路11の動作に不十分な場合にオフされる。

(もっと読む)

101 - 120 / 722

[ Back to top ]