Fターム[5H740LL03]の内容

Fターム[5H740LL03]に分類される特許

1 - 20 / 27

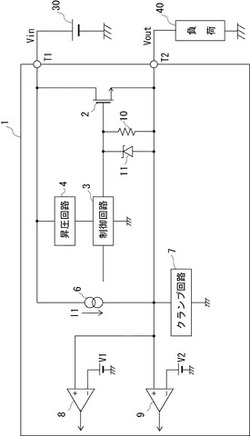

負荷駆動回路

【課題】簡単な構成で負荷オープン状態を検出することができる負荷駆動回路を提供する。

【解決手段】電源端子T1に入力される入力電圧Vinよりも低い基準電圧V1と出力端子T2の電圧Voutとを比較する第1のコンパレータ8と、スイッチング素子2がオフ状態で、且つ負荷オープン状態である場合に、出力端子T2の電圧Voutを基準電圧V1よりも高く、且つ入力電圧Vinよりも低いclamp電圧にクランプするクランプ回路7とを備えることにより、第1のコンパレータの出力によって、負荷オープン状態を検出する。また、入力電圧Vinよりも低く且つclamp電圧よりも高い基準電圧V2と出力端子T2の電圧Voutとを比較する第2のコンパレータ9を備えることにより、第1のコンパレータ及び第2のコンパレータ9の出力によって、負荷オープン状態と出力天絡状態とを検出する。

(もっと読む)

スイッチング素子の駆動回路

【課題】スイッチング素子S*#のオン状態への切り替えによってこれを流れる電流が急激に大きくなると、ツェナーダイオード40およびクランプ用スイッチング素子42を備えて構成されるクランプ回路による対処が間に合わなくなるおそれがあること。

【解決手段】ドライブIC20に端子T6を介して入力される操作信号g*#がオン操作指令に切り替わることで、定電流用スイッチング素子22をオン操作して、スイッチング素子S*#のゲートを充電する。スイッチング素子S*#のゲートの充電期間の初期において、クランプ用スイッチング素子42をオン状態としておく。

(もっと読む)

半導体スイッチング素子駆動用電源回路

【課題】従来の自給型ゲート駆動用電源回路では、RCDスナバ回路を充放電動作で使用するため、スナバ抵抗における充放電損失が大きくなり高周波動作では変換効率が低下し、装置が大型になる。さらに駆動用の電源として単一電源しか作れないため、IGBTのゲートに逆バイアスをかけることができずターンオフ損失が大きい。

【解決手段】上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、上アーム側スイッチング素子駆動回路と、下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、バイパスコンデンサの充放電電流を上アーム側スイッチング素子駆動回路と下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、記整流回路の出力を各々のスイッチング素子駆動回路用電源とする。

(もっと読む)

駆動装置

【課題】消費電力を低減した駆動装置を提供する。

【解決手段】コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備えた駆動装置である。

(もっと読む)

電力供給制御回路

【課題】従来技術の電力供給制御回路は、出力電圧にノイズが発生するという問題があった。

【解決手段】本発明にかかる電力供給制御回路は、負荷に対する電力の供給を制御する出力トランジスタ32と、外部入力信号に基づいて出力トランジスタ32のオンオフを制御するための制御信号a,bを生成するゲート駆動回路31と、出力トランジスタ32をオフする場合、制御信号a,bに基づいて出力トランジスタ32のゲート電荷を放電するためのトランジスタ37と、トランジスタ37よりも緩やかに放電するためのトランジスタ39と、トランジスタ37に直列に接続され、出力トランジスタ32をオフする場合において、出力トランジスタ32のゲート電圧が電源電圧Vccと出力トランジスタ32のしきい値電圧との和よりも大きい電圧レベルに低下した場合、出力トランジスタ32のゲート電荷の放電を遮断するダイオード40aと、を備える。

(もっと読む)

電力供給制御回路

【課題】従来技術の電力供給制御回路は、回路規模が増大するという問題があった。

【解決手段】本発明にかかる電力供給制御回路は、負荷に対する電力の供給を制御する出力トランジスタ32と、外部入力信号に基づいて出力トランジスタ32のオンオフを制御するための制御信号a,bを生成するゲート駆動回路31と、出力トランジスタ32のゲート−ソース間に設けられ、出力トランジスタ32をオフする場合、制御信号a,bに基づいて出力トランジスタ32のゲート電荷を放電するためのトランジスタ37と、トランジスタ37よりも緩やかに放電するためのトランジスタ39と、トランジスタ37に直列に接続され、出力トランジスタ32をオフする場合において、出力トランジスタ32のゲート電圧が所定の電圧レベルに低下したことを検出し、出力トランジスタ32のゲート電荷の放電を遮断するダイオード40aと、を備える。

(もっと読む)

半導体駆動回路、及びそれを用いた半導体装置

【課題】ノーマリオフの接合型FETは閾値が低いため、ノーマリオフの接合型FETを用いた半導体駆動回路では高精度な電圧制御,高速な入力容量の充電,誤動作等の課題を有していた。

【解決手段】ツェナーダイオードによる高精度なゲート電圧生成方式やスピードアップコンデンサによるターンオン損失の低減,ゲート・ソース間のコンデンサの接続やソース端子の最適実装方式による誤動作の防止回路を適用することで、ノーマリオフの接合型FETに最良な半導体駆動回路を提案する。

(もっと読む)

パワーコンバータの入力端子電圧放電回路を実現する方法および装置

【課題】パワーシステムの入力端子間のキャパシタンスを放電するための回路を開示する。

【解決手段】例示的な回路は、パワーシステムの入力に結合された制御回路を含む。制御回路は、電気エネルギ源がパワーシステムの入力に結合されたかどうかを検出するために結合される。スイッチも含まれており、スイッチは、制御回路およびパワーシステムの入力に結合される。制御回路は、電気エネルギ源がパワーシステムの入力に結合される第1の動作モードにおいてスイッチを駆動するように結合される。制御回路は、電気エネルギ源がパワーシステムの入力から分離される第2の動作モードにおいてスイッチを駆動するように結合される。パワーシステムの入力の入力端子間に結合されたキャパシタンスは、電気エネルギ源がパワーシステムの入力端子から分離されたときから最大期間未満の期間のうちに、スイッチによってしきい電圧に放電される。

(もっと読む)

ゲート駆動回路、電力変換回路及びゲート駆動方法

【課題】本発明は、トランスへの入力電圧のデューティ比が略50%でなくても不具合が生じず、また小規模で小型な構成で実現できるゲート駆動回路、電力変換回路及びゲート駆動方法を提供することを課題とする。

【解決手段】トランス2の二次側に前記スイッチング素子と直列にコンデンサ13を設ける。またトランス2の二次側に並列にスイッチング素子4に印加される電圧がトランス2の二次側の電圧よりも低い値になるよう電圧を制限するツェナーダイオード16を設ける。そしてまたトランス2の二次側の電圧が0Vになる、若しくはスイッチング素子4が逆極性となったとき、PNPトランジスタ7によってコンデンサ13を短絡する。

(もっと読む)

電力変換装置

【課題】逆回復電流に起因するスイッチング損失ならびに発熱損失を減少することができる電力変換装置を提供する。

【解決手段】電力変換装置において、ノーマリーオン型スイッチング素子4とノーマリーオフ型スイッチング素子5とを、電気的に直列接続し、カスコード接続用ダイオード7を介して、ノーマリーオン型スイッチング素子4のゲート端子とノーマリーオフ型スイッチング素子5のソース端子を接続したカスコード素子21と、このカスコード素子21と電気的に並列接続され、正極端子にカソード領域が接続され、負極端子にアノード領域が接続された高速ダイオード6とを備える。

(もっと読む)

半導体装置

【課題】ESD耐性に優れ、保護素子の新たな作製を要さない半導体装置を提供する。

【解決手段】この発明にかかる半導体装置は、主電流を制御するゲート端子22に接続されたゲート電極と、主電流を流すドレイン端子21に接続されたドレイン電極と、主電流を流すソース端子23に接続されたソース電極とを有する主MOSFET素子31と、ゲート端子22に接続されたゲート電極と、ドレイン端子21に接続されたドレイン電極と、電流検出用のセンスソース端子24に接続されたソース電極とを有するセンスMOSFET素子32と、ソース端子23に接続されたゲート電極と、ドレイン端子21に接続されたドレイン電極と、センスソース端子24に接続されたソース電極およびボディ電極とを有するESD保護素子A33と、ゲート端子22に接続されたカソード電極と、センスソース端子24に接続されたアノード電極とを有するESD保護素子D41とを備える。

(もっと読む)

モータ駆動回路及びモータ駆動回路の検査方法

【課題】複数のFETのゲートリーク電流をまとめて測定することができる。

【解決手段】電流計38の他端を、モータ駆動回路10の端子28及び30と接続した状態で、検査用探針40の他端を検査用パッド42に接触させると、検査用パッド42を介して、P−MOSFET24A及び24B、並びにN−MOSFET26A及び26Bのゲート端子に電圧が印加される。P−MOSFET24A及び24B、並びにN−MOSFET26A及び26Bのゲート端子に電圧が印加されると、ゲートリーク電流が、P−MOSFET24A及び24B、並びにN−MOSFET26A及び26Bの各々のゲート・ソース間を流れ、端子28及び30を介して電流計へ流れ、電流計によってゲートリーク電流が検出され、ゲートリーク電流の大きさが正常時のゲートリーク電流値より大きいか否かを判断することにより、モータ駆動回路を検査することができる。

(もっと読む)

半導体スイッチング装置

【課題】ノーマリオン型の半導体素子を用いて、より安全なノーマリオフ的な動作となる簡単な構成の半導体スイッチング装置を提供する。

【解決手段】市販のゲートドライバ11を用いて、ノーマリオン型のJFET10を駆動する。このとき、NチャネルのJFET10のソースSをゲートドライバ11の高圧側の電源ノード12に接続し、ゲートGをゲートドライバ11の出力ノード15に接続する。入力された制御信号VsigがLレベルの場合、出力ノード15の電位Vgは低圧側の電源ノード13の電位Vnに等しくなる。したがって、Lレベルの制御信号Vsig入力に対して、ゲート・ソース間に負の閾値電圧以下の電圧が印加されてJFET10がターンオフするというノーマリオフ的な動作が実現している。

(もっと読む)

電力変換回路の駆動回路

【課題】電圧制御形のパワースイッチング素子Sに過度の電流が流れることを回避する処理を行う場合、サージが大きくなるおそれがあること。

【解決手段】パワースイッチング素子Sのセンス端子STから出力される電流による抵抗体52での電圧降下量は、コンパレータ54によって、閾値電圧Vrefと大小関係が比較される。これにより、パワースイッチング素子Sを流れる電流(コレクタ電流)が閾値を超えるか否かを判断する。そして、閾値を超えると判断される場合、スイッチング素子56をオンすることで、パワースイッチング素子Sのゲートの電圧をツェナーダイオード58のブレークダウン電圧程度に制限する。ツェナーダイオード58のカソード及びパワースイッチング素子Sのゲート間には、放電用抵抗体42が接続されている。

(もっと読む)

スイッチング駆動回路とスイッチング回路

【課題】 高調波ノイズを低減するとともにスイッチング損失の増大も抑制する技術を提供すること。

【解決手段】 スイッチング駆動回路11は、トランジスタTr10のゲート電圧Vgを切り換えることによってトランジスタTr10のドレイン電極とソース電極間を導通状態と非導通状態の間で時間的に切り換える。スイッチング駆動回路11は、トランジスタTr10のドレイン電極Dとゲート電極Gの間に接続される可変容量素子14を備えている。その可変容量素子14の容量は、トランジスタTr10のドレイン電極Dとゲート電極Gの間の電位差が増加すると低下することを特徴としている。

(もっと読む)

スイッチング回路、及びトランジスタの駆動回路

【課題】トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制すること等。

【解決手段】電圧制御される主トランジスタと、グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、スイッチング回路。

(もっと読む)

トランジスタ駆動装置

【課題】負荷を駆動するブリッジ回路のローサイド側のトランジスタを駆動するのに好適なトランジスタ駆動装置を提供する。

【解決手段】トランジスタ駆動装置100を、駆動制御部10と、駆動電力供給部11と、電流レベル検出部12とを含んだ構成とし、駆動電力供給部11は、Hブリッジ回路のローサイド側のDMOSFETであるQ2又はQ4を、最初はPTr2のみで駆動し、Hブリッジ回路の電流検出抵抗の電圧レベルと、そのハーフ・オン状態時の電圧レベルとを比較する電流レベル検出部12からの比較信号から、Q2又はQ4がハーフ・オン状態になったと判別したときに、PTr2に加えてPTr3をオンにし、これら2つのトランジスタを介してQ2又はQ4のゲート端子に駆動電流を供給する。

(もっと読む)

電力変換装置

【課題】ダイオードリカバリによるサージ電圧を抑制すると共に、半導体スイッチング素子のターンオン時の損失増加を抑えることにより、電力変換効率の低下を抑えることが可能な電力変換装置を提供する。

【解決手段】ゲート抵抗で第1半導体スイッチング素子のスイッチング速度を決定し、第1半導体スイッチング素子を駆動する第1のゲート駆動回路7と、前記半導体スイッチング素子に制御パルスを供給する制御パルス発生回路12の出力端に、第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子であるPチャネル型のMOS-FET15とツェナーダイオード16との並列回路を直列に接続し、更に並列回路の出力端をゲート抵抗17を介して第2半導体スイッチング素子のゲート端子に接続し、第2半導体スイッチング素子を駆動する第2のゲート駆動回路8とを備える。

(もっと読む)

制御モータ駆動装置

【課題】本発明は上記課題に鑑み、インバータ回路におけるスイッチング素子の出力電流に発生するノイズを同期的に低減させ、インバータ回路によって駆動される制御モータの誤作動を有効に防止し得る制御モータ駆動装置の提供を目的とする。

【解決手段】制御モータ駆動装置100を構成するインバータ回路240は、ドライブ回路141と複数のスイッチ回路242a〜242fと電流検出回路143とを備えている。そして、インバータ回路240に配備されるそれぞれのスイッチ回路242a〜242fは、ゲートGに接続される調整抵抗Rga〜Rgfと、エミッタE−コレクタC間に接続される帰還ダイオードD1a〜D1fと、ゲートG−エミッタE間に接続される吸収ダイオードD2a〜D2fとを備えるスイッチング素子Tra〜Trfから構成されている。

(もっと読む)

負荷駆動回路およびそれを用いた点火装置

【課題】トランジスタのベースの電位が不安定になることで、寄生動作により保護回路が誤作動することを防止する。

【解決手段】保護回路7を逆トランジスタ方式で構成すると共に、各トランジスタ10〜12のベースをコレクタに接続することで、ベースの電位がコレクタの電位に固定できるようにする。これにより、従来のようにベースを開放した場合と比べて、ベースの電位を安定させられ、寄生ベースに対してノイズ的に電位が印加されても、寄生動作によりトランジスタがONしてしまう等の誤動作を防止することが可能となる。また、ベースの電位を安定させられることにより、サージ電流が発生したときに確実に保護回路7のトランジスタ10〜12をONさせられるため、保護回路7にてサージ電流を吸収してGNDに流れさせることが可能となる。

(もっと読む)

1 - 20 / 27

[ Back to top ]