Fターム[5J081BB10]の内容

LC分布定数、CR発振器 (9,854) | 用途 (545) | 同期・PLL・AFC用 (139)

Fターム[5J081BB10]に分類される特許

1 - 20 / 139

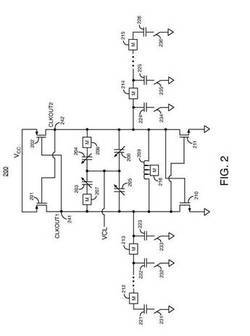

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

電圧制御発振器および関連システム

【課題】位相雑音および出力が改善された電圧制御発振器および関連システムを提供する。

【解決手段】電圧制御発振器は、第1の可変静電容量素子(120)と、第2の可変静電容量素子(122)と、可変静電容量素子(120、122)間に結合され、出力ノード(104)において、発振信号の振動周波数において可変静電容量素子(120、122)の間にインダクタンスを提供する誘導素子(132)とを含む。第1の可変静電容量素子(120)は第1の制御電圧ノード(110)および出力ノード(104)の間に結合され、第2の可変静電容量素子(122)は第1の制御電圧ノード(110)に結合され、第2の誘導素子(134)は第2の可変静電容量素子(122)および第2の制御電圧ノード(112)の間に結合される。

(もっと読む)

カスケード接続されたエミッタフォロワバッファ段を有する電圧制御発振器

【課題】負荷条件の変化に対しても安定に動作するVCOを提供する。

【解決手段】第1のトランジスタ40aを含む第1のバッファ段と、第2のトランジスタ40bを含む第2のバッファ段とを備え、カスケード接続されたエミッタフォロワバッファ回路として配置されている。トランジスタ40aおよび40bは、VCOコア21を出力から隔離する共通のエミッタ/ソースフォロワ回路に設けられている。したがって結合バッファ段42の両方のバッファ段すなわちトランジスタ40aおよび40bは、同一の電流を分担する。また、これらバッファ段はVCOコア21にACカップリング、逆隔離は直列結合された2つの固有のベース/エミッタ接合キャパシタンスによって決定されるため、キャパシタンスが半分に減少し、これによって、トランジスタ40aおよび40bのサイズが等しければ、2倍の逆隔離が得られる。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

電子機器

【課題】機器の大型化やコストアップを招くことなく、同一の構成で様々な動作温度範囲の仕様を満足し得る電子機器を提供する。

【解決手段】発振器2と、発振器2の周囲の温度を計測する温度計測部と、発振器2が実装された基板1上で、該発振器2の近辺に実装された抵抗器3〜6と、温度計測部により計測された温度に応じて、抵抗器3〜6への通電を制御する制御部と、を備える。

(もっと読む)

静磁波発振装置の固定構造

【課題】信号線や電源線を経由して伝わる振動を除去するための静磁波発振装置の固定構造を提供する。

【解決手段】永久磁石もしくは電磁石等により加えられた磁界の強さに依存して共振周波数が変化する静磁波素子を用いて所望の発振周波数を得る静磁波発振装置であって、外部と接続する信号線と、前記外部と接続する電源線と、前記静磁波発振装置を実装するための筐体に固定された支持材と、該支持材に固定され前記信号線または前記電源線を固定する緩衝材とを有し、前記信号線や前記電源線を経由して前記静磁波発振装置に伝達される振動を吸収する。

(もっと読む)

発振器

【課題】簡単な構成で高速立ち上げが可能であり、さらに従来のリング型電圧制御発振器に比べて安定な周波数の信号を生成することができる発振器を提供する。

【解決手段】制御電圧入力端子に印加された制御電圧に従って発振周波数が変化するリング型電圧制御発振器10と、リング型電圧制御発振器10の出力信号を一定時間幅のパルス信号に変換して出力するパルス整形回路20と、参照電圧からパルス整形回路20が出力する周波数が変化するパルス信号の平均電圧を差し引いた電圧を積分してリング型電圧制御発振器10の制御電圧入力端子に出力する積分回路30とを備える。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【課題】電圧制御発振器の制御利得を発振周波数に対して比較的一定に維持し、位相ノイズを低減したプログラマブルバラクタ装置を提供する。

【解決手段】プログラマブルバラクタ装置100は、複数のデジタルバラクタビットB0、B1、B2によって制御される複数のバイナリ重み付けバラクタ104,106,108を含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。

(もっと読む)

発振周波数補正信号発生回路

【課題】発振周波数とは別の周波数を生成するための回路を別途設けることなく、発振周波数を補正することができるようにする発振周波数補正信号発生回路を提供する。

【解決手段】発振信号を互いに異なる遅延時間にて遅延させて複数の遅延信号を生成し、当該遅延信号の各々に基づくタイミングにて当該発振信号を1周期単位でサンプリングして周期毎のサンプル値群を生成し、互いに異なる時点の2つの測定対象周期における当該サンプル値群の一連のサンプル値を比較してその比較結果に応じて前記補正信号を生成する。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

発振装置および角速度検出装置

【課題】振動子の起動を確実にし、安定して振動を維持する装置を提供する。

【解決手段】振動子12と、振動状態を検出する検出アンプ13と、振動情報を2値化してコンパレータ出力信号を出力する振幅比較器14と、制御発振器入力信号に応じて周波数が変化する電圧制御発振器151と、コンパレータ出力信号と比較信号との位相差信号を出力する位相比較器153と、位相差信号の低域成分を出力するループフィルタ154と、比較信号に対して予め定める位相差を有する位相シフト信号を出力する位相シフト器22と、位相シフト信号を入力する駆動アンプ11と、操作信号を出力する操作信号発生器21と、制御発振器入力信号として操作信号を選択し、制御発振器出力信号の周波数がキャプチャレンジの範囲となったときに、制御発振器入力信号として位相差情報信号を選択する操作切換器20と、を備える。

(もっと読む)

発振回路

【課題】

発振周波数を切り替えたときの発振停止を抑制した発振回路を提供する。

【解決手段】

発振回路は,第1の基準電圧側に設けられた第1,第2のインダクタL,Lxと,第2の基準電圧と第1,第2のインダクタとの間にそれぞれ設けられゲートとドレインが交差接続された第1,第2のトランジスタP1,Px1と,第1,第2のインダクタンスそれぞれに接続され複数の周波数制御用キャパシタC0〜Cn,Cx0〜Cxnを並列に有する第1,第2のキャパシタ群と,第1,第2のキャパシタ群の対応する周波数制御用キャパシタ間に設けられ発振周波数制御信号に基づいて導通または非導通に制御される複数の第1のスイッチSW0〜SWnと,第1のスイッチの両端子と所定電圧との間にそれぞれ設けられた複数の第2のスイッチSWp,SWxpとを有し,発振周波数制御信号の切り替わり時に,導通から非導通に切り替えられる第1のスイッチの両端子に設けられた第2のスイッチが一時的に導通する。

(もっと読む)

電圧制御発振回路及びPLL回路

【課題】制御電圧に対する周波数の変化量を自由に調整できる電圧制御発振回路及びPLL回路を提供する。

【解決手段】制御電圧に応じて容量成分が制御される可変容量素子Cv1、Cv2と、可変容量素子に直列に接続された直列容量素子Cs1、Cs2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続された並列容量素子Cp1,Cp2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続され、誘導成分を構成する誘導素子Lとを有する電圧制御発振回路100において、直列容量素子及び並列容量素子は、各々その容量成分を切り換え可能な構成されており、直列容量素子の容量成分及び並列容量素子の容量成分を切り換えることにより、制御電圧に対する発振周波数の変化量が調整されている。

(もっと読む)

広帯域発振回路

【課題】LC型VCOの出力する発振信号の周波数帯域が比較的狭くても、連続した周波数の発振信号(分周信号)の出力が可能な広帯域発振回路の実現。

【解決手段】発振信号を出力する発振器11と、発振器の出力する発振信号を受け、フィルタリングして注入同期信号NINJを出力するフィルタ14と、自己発振動作を行い、注入同期信号により発振動作が規制されて発振信号の分周信号を出力し、制御信号VbDに応じて分周比が変化する注入同期型周波数分周器12と、を備え、フィルタ14は、分周信号に同期したフィルタ制御信号に応じて、発振信号を通過させる通過特性を時間的に制御して注入同期信号NINJを発生する。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

通信ネットワークにおける使用のための発振器、周波数シンセサイザ及びネットワークノード

本開示は、周波数シンセサイザ内での周波数の生成における使用のための発振器であって、少なくとも1つの巻きを伴って金属線ループを形成する第1の誘導素子と、前記第1の誘導素子との間で第1の共振回路を形成するように構成され、少なくとも1つの第1の接続端子を通じて前記第1の誘導素子と接続される第1の容量回路と、を備え、前記第1の容量回路は、少なくとも1つの容量素子、並びに、発振を確立し及び維持するように構成される電子コンポーネント配置を含む、発振器に関する。当該発振器は、少なくとも1つの容量素子と電子コンポーネントの配置とを含む第2の容量回路が、前記第1の誘導素子との間で第2の共振回路を形成するように構成され、前記第1の容量回路の前記第1の接続端子に対して前記第1の誘導素子の反対側に位置する少なくとも1つの第2の接続端子を通じて前記第1の誘導素子と接続されることと、前記第1及び第2の共振回路が実質的に同等の周波数にチューニングされることと、を特徴とする。本発明は、周波数シンセサイザ及び通信ネットワーク内での使用のためのネットワークノードにも関する。 (もっと読む)

切り替え可能インダクタネットワーク

制御信号に応じて設定可能インダクタンスを有する切換可能インダクタネットワークを提供するための技術。前記切り替え可能インダクタネットワークは、差動モード動作の寄生素子の影響を低減するために完全に対称的なアーキテクチャを採用することができる。前記切り替え可能インダクタネットワークは、特に、マルチモード通信回路への用途、例えば、電圧制御発振器(VCO)またはそのような回路におけるアンプもしくはバッファに適している。 (もっと読む)

1 - 20 / 139

[ Back to top ]