Fターム[5J081EE03]の内容

LC分布定数、CR発振器 (9,854) | 周波数決定素子 (1,325) | 集中定数 (802) | C (374)

Fターム[5J081EE03]に分類される特許

41 - 60 / 374

発振回路及び電子機器

【課題】発振周波数が安定するまでに要する時間の短い発振回路及び電子機器を提供する。

【解決手段】周波数補正回路を有する共振回路と、前記共振回路の両端の間に接続された増幅回路とを備えた発振回路が提供される。前記周波数補正回路は、第1のコンデンサと、両端の電位が変動可能に前記第1のコンデンサと直列的に接続された第1のトランジスタと、を有することを特徴とする。

(もっと読む)

弾性表面波発振器

【課題】設計段階で所望の微小な差周波を得られるようにすることと、2つの弾性表面波素子の共振周波数を同程度に近づけることとの両立を図る。

【解決手段】第1、第2SAW共振子2、4の両者における櫛歯電極12、13および反射器14、15を構成する各電極のピッチp1、p2を同一としつつ、両者における各電極の交差指幅L1、L2を異ならせる。第1、第2SAW共振子2、4をこのような構造とすることで、第1SAW共振子2を有する第1発振回路の発振周波数と、第2SAW共振子4を有する第2発振回路の発振周波数とを異ならせることができ、両方の発振周波数の差である差周波を微小な周波数に設定することが可能となる。

(もっと読む)

発振回路

【課題】小型かつノイズ抑制に優れる発振回路を提供すること。

【解決手段】本発明にかかる発振回路100は、インバータ1及び2、タンク回路3を有する。タンク回路3は、出力ノードOUTTと出力ノードOUTBとの間に並列に接続される。インバータ1は、ドレインが出力ノードOUTBに接続されたn型MISトランジスタM1及びp型MISトランジスタM3を有する。インバータ2は、ドレインが出力ノードOUTTに接続されたn型MISトランジスタM2及びp型MISトランジスタM4を有する。p型MISトランジスタM3及びM4のゲート端子は、それぞれ出力ノードOUTT及びOUTBと直接的に接続される。n型MISトランジスタM1及びM2のゲート端子は、それぞれ結合容量CG1及びCG2を介して出力ノードOUTT及びOUTBと接続され、抵抗CG1及びCG2を介してバイアス電圧VBIASが印加される。

(もっと読む)

半導体装置

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

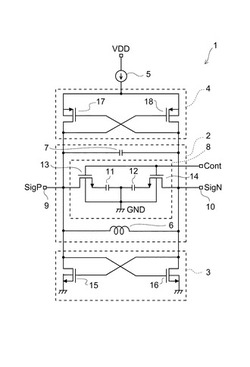

二重正帰還電圧制御発振器

【課題】低供給電圧の性能でのマイクロ波帯域における電圧制御発振器の効率を向上させるための二重正帰還電圧制御発振器を提供する。

【解決手段】2つのコルピッツ回路20、21は第1正帰還ループを提供し、第1負抵抗と等価である。NMOS交差結合ペア回路30は、第2正帰還ループを提供し第2負抵抗と等価である。2つのコルピッツ回路20、21及びNMOS交差結合ペア回路30によって生成される2つの各負抵抗は、LCタンクの寄生抵抗に対して並列に接続されている。この為2つの各負抵抗は、LCタンクの寄生抵抗をオフセットする。2つの各負抵抗が生成されるので、低電圧の稼動時において、及び、直流電流の共有において、高い負抵抗が二重正帰還電圧制御発振器10によって生成される。この為、二重正帰還電圧制御発振器10は、より低い電力下で発振可能である。

(もっと読む)

発振器

【課題】後段にフィルタを挿入しなくても、低歪みの発振波形を得ることが可能な発振器を提供する。

【解決手段】発振器100は、MOSFETである第1トランジスタM1および第2トランジスタM2を有するクロスカップルドインバータ10を備える。この発振器100は、発振動作中に、第1トランジスタM1、第2トランジスタM2それぞれのゲートソース間電圧Vgs1、Vgs2、ドレインソース間電圧Vds1、Vds2、ゲートソース間しきい値電圧Vth1、Vth2の間に、

Vds1≧Vgs1−Vth1

Vds2≧Vgs2−Vth2

なる関係が成り立つよう構成される。

(もっと読む)

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

通信装置

【課題】情報通信の安定化を図りうる通信装置を提供する。

【解決手段】通信装置は、送信機1と受信機2を含む。送信機1は、送信すべき情報INを変調して出力する変調回路3と、この変調回路3からの送信出力信号を放射する送信アンテナ電極4と、を有する。受信機2は 送信アンテナ電極4と対をなし、送信アンテナ電極4から放射された送信出力を受信する受信アンテナ電極5と、この受信アンテナ電極5と送信アンテナ電極4との間に存在する準静電界の静電容量Cを回路要素として発振動作を行う発振回路6と、この発振回路6からの出力信号を復調する復調回路7と、を有する。

(もっと読む)

発振回路

【課題】

発振周波数を切り替えたときの発振停止を抑制した発振回路を提供する。

【解決手段】

発振回路は,第1の基準電圧側に設けられた第1,第2のインダクタL,Lxと,第2の基準電圧と第1,第2のインダクタとの間にそれぞれ設けられゲートとドレインが交差接続された第1,第2のトランジスタP1,Px1と,第1,第2のインダクタンスそれぞれに接続され複数の周波数制御用キャパシタC0〜Cn,Cx0〜Cxnを並列に有する第1,第2のキャパシタ群と,第1,第2のキャパシタ群の対応する周波数制御用キャパシタ間に設けられ発振周波数制御信号に基づいて導通または非導通に制御される複数の第1のスイッチSW0〜SWnと,第1のスイッチの両端子と所定電圧との間にそれぞれ設けられた複数の第2のスイッチSWp,SWxpとを有し,発振周波数制御信号の切り替わり時に,導通から非導通に切り替えられる第1のスイッチの両端子に設けられた第2のスイッチが一時的に導通する。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

電圧制御発振回路及びPLL回路

【課題】制御電圧に対する周波数の変化量を自由に調整できる電圧制御発振回路及びPLL回路を提供する。

【解決手段】制御電圧に応じて容量成分が制御される可変容量素子Cv1、Cv2と、可変容量素子に直列に接続された直列容量素子Cs1、Cs2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続された並列容量素子Cp1,Cp2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続され、誘導成分を構成する誘導素子Lとを有する電圧制御発振回路100において、直列容量素子及び並列容量素子は、各々その容量成分を切り換え可能な構成されており、直列容量素子の容量成分及び並列容量素子の容量成分を切り換えることにより、制御電圧に対する発振周波数の変化量が調整されている。

(もっと読む)

周波数逓倍器装置及びその操作方法

【課題】本発明は、従来の周波数逓倍器による悪い高調波抑圧比を改善し、又、周波数逓倍器からの発振周波数は、他の高調波に妨害されにくいため、周波数逓倍器装置及びその操作方法を提供することを目的とする。

【解決手段】本発明の周波数逓倍器装置は、高調波発生器、高調波抑制器及び特定高調波応用装置を含んでいる。前記高調波発生器は、基本周波数を有する入力信号を受信して、第一高調波信号成分及び第二高調波信号成分を含む高調波信号を発生させる。前記高調波抑制器は、前記高調波信号を受信して、前記第一高調波信号成分を抑制し、前記第二高調波信号成分を高める。前記周波数逓倍器装置は、高められた前記第二高調波信号成分を受信する。

(もっと読む)

広帯域発振回路

【課題】LC型VCOの出力する発振信号の周波数帯域が比較的狭くても、連続した周波数の発振信号(分周信号)の出力が可能な広帯域発振回路の実現。

【解決手段】発振信号を出力する発振器11と、発振器の出力する発振信号を受け、フィルタリングして注入同期信号NINJを出力するフィルタ14と、自己発振動作を行い、注入同期信号により発振動作が規制されて発振信号の分周信号を出力し、制御信号VbDに応じて分周比が変化する注入同期型周波数分周器12と、を備え、フィルタ14は、分周信号に同期したフィルタ制御信号に応じて、発振信号を通過させる通過特性を時間的に制御して注入同期信号NINJを発生する。

(もっと読む)

半導体集積回路装置および発振周波数較正方法

【課題】発振器の発振周波数の較正作業を短縮することができる半導体集積回路装置および発振周波数較正方法を提供する。

【解決手段】DCO50と、温度に対して単調な特性を持って変化する電圧源20から得られる電位に応じたDCO50に設定すべき発振周波数の温度係数および発振周波数の絶対値を記憶する記憶部42と、を備えたことを特徴とする半導体集積回路装置。

(もっと読む)

高周波二倍波発振器

【課題】本発明は、位相雑音の劣化原因によらず位相雑音を低減できる高周波二倍波発振器を提供することを目的とする。

【解決手段】トランジスタと、該トランジスタのベース側に接続された第一電気信号線路と、該第一電気信号線路に接続され他の端は接地された第一シャントキャパシタと、該トランジスタのコレクタ側に接続された第二電気信号線路と、該第二電気信号線路に接続され他の端は接地された第二シャントキャパシタと、該第一電気信号線路と該第二電気信号線路を接続する大容量キャパシタとを備える。該第一電気信号線路の線路長は、基本波信号の波長の1/4の値を奇数倍した長さから基本波信号の波長の1/16の長さを減算した長さと、基本波信号の波長の1/4の値を奇数倍した長さに基本波信号の波長の1/16の長さを加算した長さとの間の値である。

(もっと読む)

半導体装置

【課題】同相信号除去比を高めた発振信号を得ることができる半導体装置を提供する。

【解決手段】半導体基板と、前記半導体基板上に第1の絶縁膜を介して設けられた第1の電極4と、前記第1の電極上に第2の絶縁膜を介して設けられ前記第1の電極との間に第1のキャパシタを形成する第2の電極6と、前記第1の電極上に前記第2の絶縁膜を介して設けられ前記第1の電極との間に第2のキャパシタを形成する第3の電極7と、前記半導体基板に設けられ、前記第2の電極と前記第3の電極との間に接続されたインダクタ19と、前記半導体基板に設けられ、前記第2の電極と前記第3の電極との間に接続された増幅回路20と、を備えたことを特徴とする半導体装置。

(もっと読む)

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

発振装置

【課題】発振周波数の変動を防止することができる発振装置を提供する。

【解決手段】トランジスタのゲート電圧に応じて入力端子の信号を出力端子から出力するトランスファゲートPM5,NM5と、トランスファゲートの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第1のインバータIV1と、第1のインバータの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第2のインバータPM6,NM6と、第1のインバータの出力信号の論理反転信号を入力し、入力した信号の論理反転信号をトランスファゲートの入力端子に出力する第3のインバータPM4,NM4と、トランスファゲートの出力端子及び第2のインバータの出力端子間に接続される第1の容量C1と、トランスファゲートの出力端子及び基準電位ノード間に接続される第2の容量C2とを有する発振装置。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

41 - 60 / 374

[ Back to top ]