Fターム[5J106BB01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 用途 (1,086) | 通信機器 (578)

Fターム[5J106BB01]の下位に属するFターム

データ通信 (151)

Fターム[5J106BB01]に分類される特許

1 - 20 / 427

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

分周回路およびPLL回路

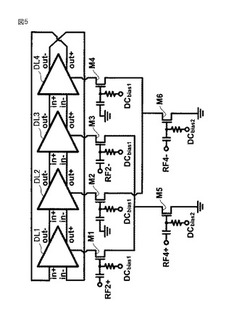

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

電子機器

【課題】局所的な温度上昇が発生した場合であっても、温度センサによる補正値と水晶振動子の周波数ドリフトとの追従ができる電子機器を提供する。

【解決手段】温度センサ素子で計測された温度を用いて水晶振動子の振動に対する補正を行う電子機器1は、基板上に配置された水晶振動子13と、温度を計測する温度センサ素子14とを備え、前記主表面のうち前記水晶振動子13で覆われた部分領域の基板内部に前記温度センサ素子14の少なくとも一部が配置される。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

PLL回路

【課題】PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制できるようにする。

【解決手段】PLL部のチャージポンプ20及びループフィルタ30をスリープ状態にし、校正部60のループフィルタ62の出力電圧V’inと校正用電源66の出力電圧Vdd/2とを電圧比較器63で比較する。比較結果を基に、V’in≒Vdd/2となるように、電流制御装置64によりデジタル制御電圧を生成し、デジタルアナログ変換器65によりアナログ制御電圧V+、V-に変換し、VCO40内の電圧電流変換回路41に供給する。

(もっと読む)

無線機

【課題】煩雑なメンテナンスを行わなくても周波数精度を高く保つことができ、かつ変調信号による周波数偏移を大きくすることができる無線機を提供する。

【解決手段】基準信号を出力する電圧制御水晶発振器と、高周波信号を出力する電圧制御発振器と、基準信号と高周波信号とが入力され、高周波信号の位相が基準信号と同じになるように位相同期を行う位相同期回路と、参照信号を発生する参照信号発生部と、基準信号の周波数を補正する周波数補正信号を電圧制御水晶発振器に出力するとともに、基準信号と参照信号とに基づき、基準信号の周波数が参照信号の周波数に対して所定の範囲内となるように周波数補正信号の値を変更する制御部と、から無線機を構成する。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

無線送信機

【課題】局部発振器の位相雑音性能の改善により、送信信号に含まれる隣接チャネル漏洩信号を大幅に低減することができる無線送信機を提供する。

【解決手段】ディジタルデータ信号を出力するデータ信号生成回路と、ディジタルデータ信号をディジタル/アナログ変換し、中間周波数のIF信号を出力するディジタル/アナログ変換回路と、IF信号と局部発振器から出力されるローカル信号とをミキシングし、無線周波数のRF送信信号を出力する直交ミキサ回路とを備えた無線送信機において、データ信号生成回路は、ディジタル/アナログ変換回路から出力されるIF信号の周波数が送信チャネルに応じて切り替わるディジタルデータ信号を出力する構成であり、局部発振器は、RF送信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成である。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

無線受信機

【課題】PLLのループフィルタの帯域を大きくすることにより、局部発振器の位相雑音性能が大幅に改善し、隣接チャネル選択性能を改善する受信機を提供する。

【解決手段】受信信号と局部発振器から出力されるローカル信号とをミキサでミキシングし、生成された中間周波数(IF)信号をバンドパスフィルタで選択して復調する無線受信機において、局部発振器は、受信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成であり、バンドパスフィルタは、受信信号の受信すべきチャネルによって通過帯域の中心周波数を切り替える構成である。

(もっと読む)

PLL回路

【課題】PLLのチャージポンプ回路からの出力電流ミスマッチにより、PLLの特性劣化に繋がるリファレンススプリアスが発生する問題がある。

【解決手段】基準信号とフィードバック信号との位相差に応じて第1、第2のパルス信号を出力する位相比較器と、第1の制御信号に応じて、前記第1、第2のパルス信号のパルス幅をそれぞれ調整した第3、第4のパルス信号を生成するパルス幅調整回路と、前記第3、第4のパルス信号に応じて出力電流を生成するチャージポンプと、前記チャージポンプの出力に接続され、電流を電圧に変換するループフィルタと、前記ループフィルタの変換した電圧を積分した検出結果を出力する検出回路と、前記検出結果に応じて、前記第1の制御信号を生成する制御回路と、を有するPLL回路。

(もっと読む)

レベル調整装置

【課題】 基準発振器、VCO、位相比較器の純度が低くても位相雑音特性を良好にする。

【解決手段】 基準発振器28aが発振する基準周波数frefをBS放送波のチャンネル間隔とされる38.36MHzに設定する。そして、中間周波数を282.28(=7×38.36+13.76)MHzとした場合は、1049.48MHzのチャンネル周波数とされるBS−1チャンネルがアサインされるBS−IFレベル調整ユニット10では、局部発振器28の出力周波数foutが767.2MHzになり、分周器28eの分周数Nを20とすればよい。基準周波数frefを38.36MHzと高くすることができるため、局部発振器28の位相雑音特性が良好になる。

(もっと読む)

水晶発振器回路の温度依存性及び処理依存性周波数変動を低減させるシステム及び方法

【課題】無線通信エレメントの発振器に於いて、共振器の温度依存性に対する処理の変動を補償する発振器の提供。

【解決手段】発振器210は、アクティブ・エレメント312と並列に共振器310を含み、共振器は、可変静電容量を有する可変コンデンサ314に結合し、発振器の出力周波数同調を可能にする。所定の温度補償算出器324は温度センサ322からの温度信号に基づき、共振器のロットに対して行われる特徴付けデータを参照して、温度ベースの周波数補償信号を出力する。又、周波数推定器326からの周波数推定信号に基づき、処理補償算出器328は共振器の処理依存性補償を算出して処理ベースの補償信号を出力し、乗算器330は前記周波数補償信号及び前記補償信号に基づき乗算器出力信号を出力し、制御モジュール332は、乗算器出力信号に基づき、制御信号を可変コンデンサに供給し、共振器における温度、処理ベースの変動を補償する。

(もっと読む)

CDR回路、受信装置、および送受信システム

【課題】非線形位相比較器を用いたCDR回路、受信装置、および送受信システムの再生クロックの位相追従精度を向上させる。

【解決手段】CDR回路106、受信装置101、および送受信システム100は、受信データ105および再生クロック119が入力される非線形位相比較器の出力に、受信データに対する、再生クロックに対して位相差を有するクロックの遅れまたは進みに応じて重み付けをし、重み付けされた出力に基づいて再生クロックの位相を調整する。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

PLL回路

【課題】 電源投入時及び基準周波数信号断から基準周波数信号入力有りの時からロックまでの時間を短くでき、ロック時の発振を安定化させ、更にロック状態から基準周波数信号断となった時にロックから制御電圧の中心付近まで早く落ち着かせることができるPLL回路を提供する。

【解決手段】 電源投入時とREF断状態からREF有りとなった場合に、積分器15内のオペアンプ39の利得を大きくし、増幅器16内のオペアンプ37の利得を大きくすることで、ロックまでの時間を短くでき、ロック時に増幅器16内のオペアンプ37の利得を小さくし、ロック状態でREF断となった場合に、積分器15内のオペアンプ39の利得を小さくしているので、自走時にコンデンサ28の電荷の放電を早めて、自走周波数に移行する時間を短くして安定化を早めることができるPLL回路である。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

1 - 20 / 427

[ Back to top ]