Fターム[5J106BB05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 用途 (1,086) | 計測機器 (35)

Fターム[5J106BB05]に分類される特許

1 - 20 / 35

平面型X線センサ

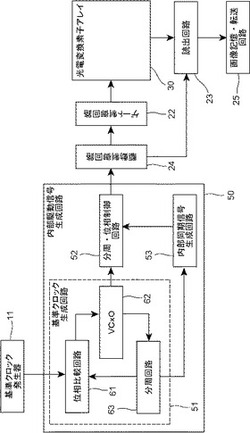

【課題】内部駆動タイミングと外部基準クロックとを整合させる。

【解決手段】X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサの内部駆動信号を生成する内部駆動信号生成回路50に、PLL構成の基準クロック生成回路51を備える。基準クロック生成回路51は、電圧制御発振器62と分周回路63と位相比較回路61とを備える。電圧制御発振器62は、たとえば水晶発振器を用いて、内部基準クロックを生成する。分周回路63は、内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する。位相比較回路61は、外部基準クロックと前記分周クロックとの位相を比較してその位相差を電圧制御発振器62に入力する。

(もっと読む)

信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

(もっと読む)

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

デジタル位相同期回路および物理量検出センサ

【課題】簡単な構成で位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

(もっと読む)

送受信装置

【課題】構造簡単な距離を測定可能とした送受信装置の実現

【解決手段】第1信号の受信と第2信号の送信とを共通化した送受信アンテナ20と、第1信号を復調して第1パルス信号を得る復調器30と、制御信号を入力して目標周波数を設定する目標周波数設定レジスタ61と目標位相を設定する目標位相設定レジスタ66とを有し、目標周波数設定レジスタに設定されている目標周波数と目標位相設定レジスタに設定されている目標位相とに一致した周波数と位相の第2パルス信号を出力するパルス発振器60を有する。第2パルス信号により搬送波を変調する変調器70と、第1パルス信号と、第2パルス信号との位相差を検出する位相比較器32を有する。また、位相差信号の時間変動からその時の第1パルス信号と第2パルス信号との周波数差をもとめ、その周波数差に基づいて目標周波数を制御する周波数制御装置と、位相差信号の示す位相差に基づいて目標位相を制御する位相制御装置とを有する。

(もっと読む)

注入同期発振器

【課題】逓倍数が任意の大きな数であっても、位相雑音が低減された注入同期発振器を得る。

【解決手段】注入同期発振器は、注入される注入信号に同期して自励発振周波数の信号を発振する発振器を備える注入同期発振器において、上記自励発振周波数と略同じ周波数の逓倍数分の1の周波数の基準信号が入力されるともに該基準信号にトリガーされてパルスを生成するパルス発生回路と、上記パルス発生回路で生成したパルスとタイミングが異なる少なくとも1つのパルスを生成するとともに該生成されたパルスと上記パルス発生回路で生成したパルスとを合わせて注入信号として出力するパルス数増倍回路と、を備える。

(もっと読む)

量子干渉装置及び量子干渉方法

【課題】アルカリ金属原子に対するEIT現象の発現効率を高めることができる量子干渉装置及び量子干渉方法を提供すること。

【解決手段】光源10は、互いに周波数が異なる複数の第1の光と互いに周波数が異なる複数の第2の光とを発生させてアルカリ金属原子20に照射する。光検出部30は、アルカリ金属原子を透過した光の強度を検出する。制御部40は、光検出部が検出した光の強度に基づいて、第1の光の各々と第2の光の各々との周波数差が2S1/2の第1の基底準位と第2の基底準位とのエネルギー差に相当する周波数にそれぞれ一致するように制御し、かつ、第1の光の各々の波長が2P1/2のいずれかの励起準位又はその近傍の準位と第1の基底準位とのエネルギー差に相当する波長と一致するように制御するとともに、第2の光の各々の波長が当該励起準位又はその近傍の準位と第2の基底準位とのエネルギー差に相当する波長と一致するように制御する。

(もっと読む)

信号発生装置および試験装置

【課題】ループ帯域より高い周波数のジッタを印加する。

【解決手段】指定された位相の出力信号を発生する信号発生装置であって、所定周期の基準信号と出力信号との位相差に応じた制御信号を出力する位相差検出部と、制御信号の高域成分を除去するループフィルタと、ループフィルタにより高域成分が除去された制御信号に応じた周波数の周期信号を発生する発振部と、指定された位相分、周期信号に対して位相がシフトされた出力信号を出力する位相シフト部と、を備える信号発生装置を提供する。

(もっと読む)

周波数掃引方法及び回路

【課題】階段状波形による繰返し周波数信号が生成されることなく、高速掃引が可能となり、また温度等の環境条件に左右されることなく、周波数制御を安定して行う。

【解決手段】VCO1からの出力をプログラマブルカウンタ14、PFD16、安定化フィルタ17及び傾き制御用フィルタ18を介して帰還させるループを形成し、プログラマブルカウンタ14からの現在の周波数ポイントの制御信号に基づく周波数引込み時間内に、次の周波数ポイントの制御信号をPFD16に出力し、位相同期状態を経ることなく、連続した周波数の掃引を実行する。上記傾き制御用フィルタ18では、掃引における周波数変化の傾きを制御する。

(もっと読む)

信号受信装置、信号受信装置の制御方法及びコンピュータプログラム

【課題】1つの位相比較器及びループフィルタを複数の同期保持チャネルで共有することで、同期保持チャネルの増加に伴う回路規模の増大を抑えることが可能な信号受信装置を提供すること。

【解決手段】所定の周波数のキャリアを生成する信号生成器を含む位相同期ループ部と、衛星から受信した信号のキャリアと信号生成器が生成したキャリアとの位相差を検出して出力する1以上の位相比較器と、位相比較器が出力する位相差情報からノイズを除去して所望のループの応答を実現する1以上のループフィルタと、を備え、同時に追跡可能な最大衛星数N(Nは2以上)に対して、位相比較器及びループフィルタの数MはN>Mである、信号受信装置が提供される。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

高性能信号発生

【課題】高性能位相検出器は、プログラムで制御できる周波数および位相を有するデジタル基準信号を生成する局部デジタルオシレータを含む。

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

(もっと読む)

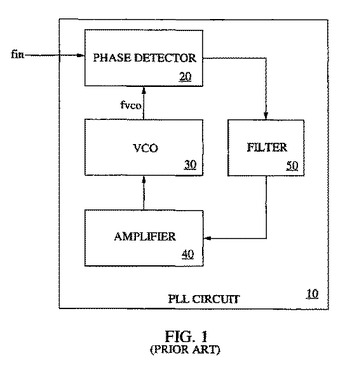

PLL回路およびそれを用いた角速度センサ

【課題】本発明は、正確に位相を調整することが可能なPLL回路およびそれを用いた角速度センサを提供することを目的とするものである。

【解決手段】本発明のPLL回路およびそれを用いた角速度センサは、AD変換器21が電圧制御発振器26の出力するタイミング信号により動作し、かつDA変換器24が分周器27の出力するタイミング信号でのAD変換器21の出力する値に応じたアナログ信号を出力する構成としたものである。

(もっと読む)

アナログ位相拘束ループ装置

【課題】単一で安定し信頼性のあるアナログのタイプIII位相拘束ループ装置を提供する。

【解決手段】位相検出器2は入力基準信号4及び出力信号6の位相差を表すエラー信号12を発生する。選択器14は第1帯域幅パラメータ値の選択時にエラー信号を第1信号経路8に供給し、第2帯域幅パラメータ値の選択時にエラー信号を第2信号経路10に供給する。第1信号経路はエラー信号を積分する第1積分器16と、その積分信号を積分してエラー電圧信号を発生する第2積分器18と、このエラー電圧信号に応答して第1信号経路出力信号を発生する電圧制御発振器20とを具えている。第2信号経路も同様な積分器22,24及び電圧制御発振器26を具えている。選択器28は第1帯域幅パラメータ値の選択時にVCO20の出力を選択し、第2帯域幅パラメータ値の選択時にVCO26の出力を選択する。選択器28の出力信号が位相検出器2に帰還する。

(もっと読む)

試験測定装置並びに位相拘束ループ及び方法

【課題】消費電力が大きくなく、位相ノイズが小さく、広い同調範囲のPLLを提供する。

【解決手段】位相検出器34は、基準信号路30及び帰還信号路32から入力の位相差を検出し、位相検出器出力を発生する。発振器32は、位相検出器出力に応答し且つこの位相検出器出力に基づいた発振出力Foutを発生する。この発振出力Foutが帰還信号路32に供給される。基準信号路30内のミキサ74は、基準信号Frefをダイレクト・デジタル・シンセサイザ72からの出力と混合する。基準信号路内のスイッチング機構80は、複数の異なるフィルタの1つを選択的にミキサ及び位相検出器の間に直列に配置する。

(もっと読む)

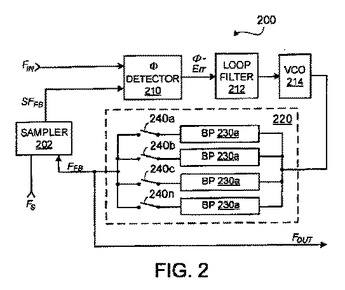

偽信号化された周波数上の位相ロック

位相ロックループ(200)は、サンプラー(202)、位相検出器(210)、ループフィルタ(212)、VCO(214)を含む。ループは、ループのフィードバックパス中に分割器を必要とすることなく周波数逓倍を達成する。VCO(214)は、サンプラーのナイキストレートより上で動作され、ループが偽信号化された信号上にロックすることを引き起こす。VCO出力周波数中のあらゆる変動(即ち、ジッターまたは位相ノイズ)は、周波数分割器に通常関連付けられる減衰無しで、1対1で位相検出器(210)にフィードバックされる。ループゲインは従って、高い閉ループ周波数逓倍を提供するループにおいてでも、高く保つことができる。一変形によると、高調波発生器(540)がVCOとサンプラーの間に置かれ、よってループがVCO周波数の高調波上にロックすることを引き起こす。開ループゲインと精度はよって更に向上される。  (もっと読む)

(もっと読む)

遅延回路およびそれを用いた信号発生回路

【課題】 プログラマブル遅延回路のオフセット遅延時間が周囲温度などの周囲条件によって変化するので、このプログラマブル遅延回路を用いた信号発生回路の出力波形信号が不安定になってしまうという課題を解決する。

【解決手段】 プログラマブル遅延回路と遅延回路を直列接続してプログラマブル遅延回路にクロックを入力し、この2つ遅延回路の合計遅延時間が一定になるように前記プログラマブル遅延回路の遅延時間を制御すると共に、このプログラマブル遅延回路の出力を複数のプログラマブル遅延回路に入力するようにした。また、この複数のプログラマブル遅延回路を用いて信号発生回路を構成した。周囲条件が変化しても複数のプログラマブル遅延回路のクロックに対する遅延時間が変動することがない。

(もっと読む)

低消費電力装置を有するタイヤ圧検出器

タイヤ圧検出器は、集積回路に外付けされるように構成されるパワーアンプと、入力データストリームの論理状態に応じて動作するVCOを有するPLL回路とを備える低消費電力装置を用いる。入力データストリームは、タイヤ圧力情報を有し、複数の論理状態を有するようにエンコードされるように構成される。入力データストリームの各データビットのパターンに応じて、所定の期間、VCO及び/又はアンプをターンオン及びターンオフすると、マイクロコントローラがVCOを制御するために用いられる。このタイヤ圧検出器は、電力効率に関して最適化された回路配置をこのようにして具現化する。  (もっと読む)

(もっと読む)

電波ビーコン及びその搬送周波数の監視方法

【課題】送信周波数の監視を容易に行うことができる電波ビーコンを提供する。

【解決手段】電波ビーコンは、内部の基準発振器13からの基準周波数を逓倍して所定の搬送周波数の搬送波を生成する搬送波発生器4を備えており、この搬送波にデータ信号を重畳した電波を外部に送信する。電波ビーコンは、前記基準周波数を分周してより低い周波数の被検査信号T1を生成する分周回路16と、この被検査信号T1を、外部から受信した参照信号T0と比較して、これらの信号の時間差を検出するタイムインターバル比較回路17と、検出した時間差に基づいて前記基準発振器13の動作状態の適否を判定し、その動作状態が不適の場合にエラー処理を行う制御部10とを備えている。

(もっと読む)

クロック信号生成回路、及び半導体装置

【課題】製造プロセスにおけるばらつきが原因による同期期間や同期期間終了後の自走期間において、周波数が変動することがなく、安定した動作を実現し、また安価な半導体装置を提供する。

【解決手段】第1の基準クロック信号を生成する基準クロック信号生成回路と、第1基準クロックの信号及び同期信号を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第1のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第2のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号を分周し、第2の基準クロック信号を生成する第1の分周回路と、第2の基準クロック信号を分周し、クロック信号を生成する第2の分周回路と、を有するクロック生成回路を半導体装置に搭載する。

(もっと読む)

1 - 20 / 35

[ Back to top ]