Fターム[5J106CC27]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | 論理回路型 (99) | イクスクル−シブオア型 (24)

Fターム[5J106CC27]に分類される特許

1 - 20 / 24

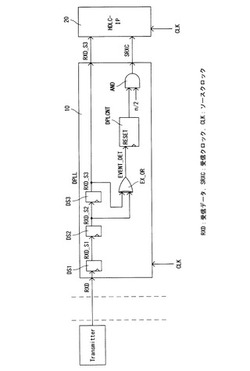

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

周波数補正回路

【課題】送信波の周波数に同期された周波数又はその逓倍波を容易かつ正確に出力できる周波数補正回路を提供する。

【解決手段】第1電圧制御発振器16の出力信号と基準発振信号との位相差に応じた位相差信号を第1位相比較器10により生成し、第1ループフィルタ12を介して第1位相差信号に応じた第1発振制御信号により第1制御発振器16の発振をフィードバック制御する第1フェーズロックループ回路106と、第2電圧制御発振器36の出力信号と比較対象信号との位相差に応じた位相差信号を第2位相比較器30により生成し、第2ループフィルタ32を介して第2位相差信号に応じた第2発振制御信号により第2制御発振器36の発振をフィードバック制御する第2フェーズロックループ回路114とを備え、第1発振制御信号に応じて第2発振制御信号を変動させることによって比較対象信号に応じて出力信号をロックする。

(もっと読む)

位相補正方法、位相補正回路、及びそれを含む信号処理装置

【課題】ローカルオシレーターから出力された信号の位相補正方法を提供する。

【解決手段】方法は、同位相出力信号の位相と直交位相出力信号の位相との比較結果に相応するデジタルコードを発生させる。方法は、同位相出力信号の位相と直交位相出力信号の位相との差を90°にするために、直交位相差動入力信号とデジタルコードとに応答して、同位相出力信号の位相を調節し、同位相差動入力信号とデジタルコードとに応答して、直交位相出力信号の位相を調節する。

(もっと読む)

デジタル遅延線の時間遅延のプロセス、電圧、および温度のばらつき補正を行う装置と方法

【課題】プロセス、電圧、温度、補償回路、および連続的に遅延量を発生させる方法を提供する。

【解決手段】補償回路は2つの遅延線を含んでおり、各遅延線が遅延出力を供給する。2つの遅延線は、それぞれが多数の遅延エレメントを含み、その結果として1つ以上の電流枯渇型インバータを含む場合がある。遅延線の数は、2つの遅延線間で異なる場合がある。遅延出力は、2つの遅延出力に基づくオフセットパルスを決定した後、オフセットパルスの電圧を平均し、遅延量を決定する合成回路に供給される。遅延量は、1つ以上の電流または電圧となる場合があり、メモリバスドライバ、動的ランダムアクセスメモリ、同期DRAM、プロセッサ、あるいは他のクロック回路のようなアプリケーション回路の入力信号または出力信号に適用されるPVT補正量を示す。

(もっと読む)

位相比較回路

【課題】D−FFの内部遅延が無視できない高速動作時において位相比較回路の低消費電力化を実現する。

【解決手段】マスタースレーブマスター型D−FF11は、第1のM−FF11−1,S−FF11−2および第2のM−FF11−3が縦続接続され、入力NRZデータ信号をクロック信号に応答して識別し、S−FFおよび第2のM−FFから出力する。遅延回路4は、入力NRZデータ信号をS−FFと同じ時間だけ遅延させる。第1のEXOR回路7は遅延回路の出力とS−FFの出力の排他的論理和演算を行ない、第2のEXOR8はS−FFの出力と第2のM−FFの出力の排他的論理和演算を行なう。加算器9は第1のEXOR回路の出力と第2のEXORの反転出力を加算する。

(もっと読む)

信号再生回路

【課題】受信マージンを拡大可能な信号再生回路を提供する。

【解決手段】例えば、クロック信号CLKa,CLKb,CLKcを生成するクロック生成部CLK_GENと、CLKaとCLKbの間、又はCLKbとCLKcの間にデータ信号Diのエッジが入り込んだ際に、位相検出信号(EARLY,LATE)を生成するクロック・データ判定部CD_JGEと、ウインドウ幅制御部WW_CTL等を設ける。CLK_GENは、この位相検出信号に基づいて、前述したDiのエッジが入り込まないように、CLKa,CLKb,CLKcの全体位相を互いの位相差を保ったままで制御すると共に、WW_CTLからの信号(Sww)に基づいて、CLKaとCLKbの位相差、およびCLKbとCLKcの位相差を制御する。

(もっと読む)

半導体集積回路

【課題】ロック動作の初期において高速引き込みを可能とすると伴に入力信号ジッタや入力雑音の影響の小さなディジタルフェーズロックドループを提供すること。

【解決手段】半導体集積回路は、位相比較器10、11、ディジタルループフィルタ12、ディジタル制御発振器13、フィードバック分周器14を含むディジタルフェーズロックドループADPLLを具備する。ディジタルループフィルタ12は、第1ゲインαを有して位相比較器10、11のディジタル位相出力信号θが供給される比例パス12aと、第2ゲインβを有して信号θが供給される積分パス12b、12c、12dと、信号θの大きさを判定する判定器12g、12hを含む。ディジタル位相出力信号θの大きさが所定の基準値θthよりも大きい場合には、判定器12g、12hは第2ゲインβと第1ゲインαとの比β/αを大に設定する。

(もっと読む)

位相同期回路、半導体装置及び無線タグ

【課題】動作範囲の広いPLLの提供を課題とする。さらに、そのようなPLLを内蔵することで、通信距離や温度において動作範囲の広い半導体装置または無線タグの提供を課題とする。

【解決手段】第1の分周回路と、第2の分周回路と、第1の分周回路の出力及び第2の分周回路の出力が与えられる位相比較回路と、位相比較回路の出力が与えられ、なおかつ入力される信号に従って時定数が切り替わるループフィルタと、ループフィルタの出力が与えられ、なおかつ第2の分周回路に出力を与える電圧制御発振回路とを有する半導体装置または無線タグ。

(もっと読む)

PLL回路、位相制御方法、および、ICチップ

【課題】クロック周波数を上げることなく、受信精度を向上させる。

【解決手段】分周器131は、クロック信号f_clkを8分周することにより、PSK変調されたデジタル信号DATAとほぼ同じ周波数の互いにπ/2だけ位相が異なる信号sin(wt)、信号cos(wt)を生成する。ACT136は、信号sin(wt)および信号cos(wt)を仮想的に制御角Φだけ移相させた信号と信号DATAとの位相を比較した結果を示す信号ΣV11および信号ΣV12に基づいて、信号DATAと仮想の信号sin(wt+Φ)の位相を同期させるように、cosΦに対応するパラメータcos_paraおよびsinΦに対応するパラメータsin_paraの値を制御する。また、ACT136は、信号ΣV11およびΣV12に基づいて、CPUが信号DATAからデータを読み出すタイミングを制御する。本発明は、非接触ICチップに適用できる。

(もっと読む)

クロックデータ復元装置

【課題】より正確にクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、入力したデジタル信号に基づいてクロック信号およびデータを復元する装置であって、イコライザ部10、サンプラ部20、クロック生成部30、イコライザ制御部40および位相モニタ部50を備える。イコライザ部10、サンプラ部20およびイコライザ制御部40によるループ処理により、イコライザ部10におけるデジタル信号のレベル調整量の制御が行われるが、一方で、クロック信号CKとデジタル信号との間の位相差が所定値より大きいときには当該制御が位相モニタ部50により停止される。これにより、より正確にクロック信号およびデータが復元され得る。

(もっと読む)

移相回路

【課題】 移相量を常に一定に制御可能とし、電源電圧変動時等の影響の低減、素子バラツキの影響を低減する移相回路の提供。

【解決手段】基準周波数信号が入力されて2分配され一方の信号は位相比較器102の一方の入力となり、他方の信号は移相器101を介してその位相が移相された後に、前記位相比較器102の他方の入力となり、位相比較器102の出力はループフィルタ(LPF)103を介して差動増幅器104の一方の入力端子に入力され、差動増幅器104の出力信号により移相器101の移相量が制御されるPLLループを有し、差動増幅器104の他方の入力端子に印加される基準電圧により前記移相器101での移相量が定まる。

(もっと読む)

位相比較信号処理回路

【課題】位相比較回路の出力矩形波信号の処理する際に、簡単な回路構成を有し、PLLで引込み可能な周波数幅を拡げ、同期時間を短縮できる位相比較信号処理回路を提供する。

【解決手段】入力矩形波信号を双極性信号に変換する電圧シフタ2、入力矩形波信号のレベル変化時に制御パルス信号を発生する制御パルス信号発生器7、制御パルス信号の到来時に積分値をリセットし、その後双極性信号を積分して積分値を出力する積分回路3、積分値のリセット時のレベル変化分を微分パルスとして出力する微分回路4、制御パルス信号の到来時に微分パルスを出力するゲート回路6、前記保持回路は最新の入力微分パルスレベルを保持し、微分パルスレベルの更新時にその微分パルスレベルが保持されるように保持電圧値が順次変化する保持信号を形成するホールド回路8を備え、この保持信号を次段のループフィルタに供給する。

(もっと読む)

集積回路、再生装置及び再生方法

【課題】 本発明は、集積回路、再生装置及び再生方法に関し、例えば非接触型のICカードシステムに適用して、クロックの周波数がばらついた状態で、デューティー比が50〔%〕から変化した場合でも、正しくデータを再生することができるようにする。

【解決手段】 本発明は、ペイロードの部分に比して速く収束するようにPLL回路の動作を切り換えて、90度位相の異なる基準信号の一方を入力信号に位相同期させるようにこれら基準信号を位相制御し、他方の基準信号が入力信号に位相同期したとの位相比較結果が得られた場合に、直前の制御を継続する。

(もっと読む)

位相誤差検出回路、位相同期ループ回路及び情報再生装置

【課題】最小ランレングス信号の再生レベルが極端に低い場合においても、安定した位相同期特性を得るための位相誤差検出回路、位相同期ループ回路および情報再生装置を提供すること。

【解決手段】位相誤差検出回路7は、アナログ入力信号に所定のクロックでサンプリングを行いA/D変換したデジタル信号を入力する。入力信号の連続する4個のサンプルに対して3次の補間演算により検出点におけるデジタル信号の振幅値を求め、その信号極性に基づいてサンプリングの位相誤差信号を出力する。その際、連続するサンプルの符号列の最小ランレングスが2以上の場合にのみ位相誤差信号を出力するよう制限する。

(もっと読む)

遅延ロックループ、および、遅延鎖の設定方法

【課題】過渡回復を出来る限り速く行う。

【解決手段】遅延ロックループは、入力部(9)と直列接続遅延セル(30,50,70,90)と出力部(10)とを有し、出力部では、遅延鎖(1)により遅延時間(Tk)だけ遅延された信号(PreStrobe)が供給される。遅延ロックループは位相検出器構造(2)を含み、位相検出器構造は入力側において遅延鎖(1)の出力部(10)と遅延鎖(1)の遅延セル(30,50,70,90)のうちの1つの出力部とに結合される第2位相検出器セル(31,51,71,91)と、遅延鎖(1)の出力部(10)と遅延鎖(1)の入力部(9)とに結合された位相検出器とを備える。位相検出器構造(2)、位相検出器(3)は制御ユニット(4)に接続される。制御ユニット(4)は遅延セル(30,50,70,90)のうちの個数Zを、遅延を行うように起動することにより遅延鎖(1)の遅延時間(Tk)を設定する。

(もっと読む)

クロックおよびデータリカバリ位相ロックループならびに高速位相検出器アーキテクチャ

入力データ速度の2分の1(すなわちハーフレートのクロック)に等しいクロック速度で動作するクロックリカバリ回路および高速位相検出器回路が提示される。クロックリカバリ回路は二重入力ラッチを用いて、ハーフレートのクロック信号の立ち上がりエッジおよび立下りエッジの双方で入力シリアルデータをサンプリングして、等価の最高データ速度のクロックリカバリを与える。クロックリカバリ回路は、入力シリアルデータビットの中心におけるハーフレートのクロック遷移を維持するように機能する。クロックリカバリ回路は、位相検出器、チャージポンプ、制御された発振モジュールおよびフィードバックモジュールを含む。位相検出器は、チャージポンプへの入力データ信号における位相およびデータの遷移に関する情報を生成する。一般的に、回路は遅延の影響を受けず、互いに対してずらされた位相および遷移情報を受信する。高速位相検出器回路は、入力シリアルデータからの位相情報および遷移情報を与える。高速位相検出器回路は、ハーフレートのクロックの立ち上がりエッジおよび立下りエッジの双方での入力シリアルデータをサンプリングして、等価の最高データ速度サンプリングを与える。高速位相検出器回路は、位相情報および遷移情報の間で遅延を生じる。位相情報は第1のビット周期で生成され、遷移情報は第1のビット周期に対する第2のビット周期で生成される。  (もっと読む)

(もっと読む)

デジタル信号処理装置

【課題】 不要輻射を発生させずに信号処理を行うことのできるデジタル信号処理装置を提供する。

【解決手段】 供給されるデジタル情報信号の信号処理を行う信号処理手段10の内部に、第1の入力端子から入力される第1の入力信号と第2の入力端子から入力される第2の入力信号の位相差を出力する位相比較器1と、上記位相比較器1の出力信号の高周波成分をカットする低域通過フィルタ2と、上記信号処理手段が上記供給されたデジタル情報信号を処理する際に利用する動作クロック信号として、上記低域通過フィルタの出力信号の振幅値に基づく発振周波数で出力信号を発生する発振器3と、指定された分周比で上記発振器の出力信号を分周して上記第2の入力端子に供給する分周器4とを備える。

(もっと読む)

位相比較回路

【課題】比較対象となるクロック信号が正常ではない場合においても位相比較結果が大きくずれてしまうことを抑圧できるような位相比較回路を提供する。

【解決手段】比較クロック102の“1”レベル区間に短期間の“0”レベル区間が入ってしまった場合にも、基準クロック101の1回の立ち上がりエッジに対し比較クロック102に2回目の立ち上がりエッジが発生したことをクロック異常検出部107が検出しクロック異常信号108を出力する。位相比較部109はクロック異常信号108を受け、比較クロック102の2回目の立ち上がりエッジでは位相比較を行わず、比較クロック102が正常である場合と同等な位相比較結果110を出力するため、比較クロックの“1”レベル区間に短期間の“0”レベル区間が入ってしまったような正常ではない場合においても位相比較結果が大きくずれてしまうことを抑圧することができる。

(もっと読む)

位相比較器

【課題】比較演算に係る論理回路の回路規模を削減し、その結果、その回路面積を縮小し、遅延時間を短縮し、消費電力を低減することができる位相比較器を提供する。

【解決手段】位相比較器は、データとデータのハーフレートの位相が90°ずつずれた4相の第1〜第4のクロックとの間の位相を比較するもので、データを4相の第1〜第4のクロックで各々サンプリングする第1〜第4のサンプリング回路と、第1および第2のサンプリング回路によって、その位相が隣接する2相の第1および第2のクロックで各々サンプリングされた2つのデータ同士を比較し、両者が異なる場合に第1のアップ信号を出力する第1の比較回路と、第4および第1のサンプリング回路によって、その位相が隣接する2相の第4および第1のクロックで各々サンプリングされた2つのデータ同士を比較し、両者が異なる場合に第1のダウン信号を出力する第2の比較回路とを備える。

(もっと読む)

1 - 20 / 24

[ Back to top ]