Fターム[5J106CC41]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | ループフィルタ (906)

Fターム[5J106CC41]の下位に属するFターム

複数のループフィルタ (25)

Fターム[5J106CC41]に分類される特許

161 - 180 / 881

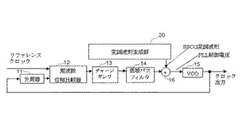

クロック生成回路と半導体装置及びクロック生成方法

【課題】スペクトルの抑圧効果の高い変調波形を得ることができ、Hershey−kissによる変調方式と比べ、回路規模を小さくするクロック生成回路の提供。

【解決手段】変調波形生成部20は、SSCG変調波形として、tan波形またはtan+三角波を生成し、PLLループの低域パスフィルタ14の出力に、該SSCG変調波形を合成した信号を発振器(VCO)15に与える。

(もっと読む)

位相検出回路およびPLL回路

【課題】2つのクロック信号の位相比較に基づき生成する2つのパルス信号の遅延時間を極力短くすることができ、かつ確実にリセットできる位相検出回路および該位相検出回路を備えたPLL回路を提供すること。

【解決手段】位相検出回路は、位相比較を行う2つのクロック信号の論理和信号と論理積信号とに基づき、進相側と遅相側の2つのパルス信号の生成に用いる一方の出力を、前記位相比較を行う準備動作状態と、前記位相比較を行った回路動作状態とに切り替えて保持するラッチ回路を備えている。

(もっと読む)

通信システム

【課題】製造ばらつき・温度変動に依存することなく、受信状態又は送信状態を良好に保つ事が出来る通信システムを提供すること。

【解決手段】電圧制御発振部(106)の発振周波数を制御するように、位相同期回路(100)からの周波数制御信号(c1)を用いて、第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つの同調周波数を制御することで、受信周波数の同調を行い、Q値制御回路(110)からのQ値制御信号(b1)を用いて第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つのQ値制御用可変抵抗の抵抗値を可変することにより、第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つのQ値を制御して、受信帯域の最適化を行う。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

(もっと読む)

位相ロックループ回路およびそれを用いた電子機器

【課題】gm−C型VCOを用いたPLL回路において、VCOをgmセルのトランスコンダクタンス(α・gm)と、キャパシタの容量値Cの比で定まる発振周波数で確実に発振させる。

【解決手段】gm−C型VCO10は、入力された制御電圧Vtuneに応じた周波数で発振する。分周器4は、gm−C型VCO10から出力される発振信号Voscを分周する。位相比較信号生成部5は、分周器4により分周された発振信号Vosc’と、基準クロック信号CLKの位相差に応じた位相差信号Vpdを発生する。ループフィルタ6は、位相差信号Vpdをフィルタリングし、制御電圧Vtuneを生成する。スタートアップ回路8は、制御電圧Vtuneに応じた検出信号Vsのレベルにもとづいたタイミングにおいて、gm−C型VCO10にシードパルスS3を注入する。

(もっと読む)

デューティ補正回路、遅延同期ループ回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】デューティ比が50%より大きい場合も小さい場合も両方を一つの素子で対応が可能であり、素子数を削減できるだけではなく、スイッチング回数を削減することが可能で、消費電流を削減することができるデューティ補正回路、DLL回路、カラムA/D変換器、固体撮像素子、およびカメラシステムを提供する。

【解決手段】デューティ補正回路10は、第1入力および第2入力を有するC素子11と、C素子11の第2入力に接続されたインバータ12と、を有し、C素子11は、入力が両方とも論理“1”になると出力が論理“1”になり、入力が両方とも論理“0”になると出力が論理“0”になり、その他の状態では出力は前の状態を保持し、C素子11の第1入力およびインバータ12にそれぞれ互いに位相差がほぼ半周期の相補クロックが入力される。

(もっと読む)

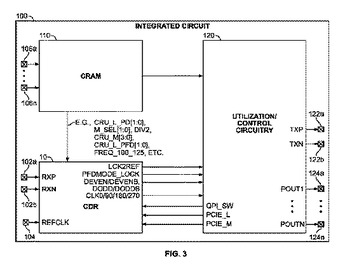

オートスピードネゴシエーションおよび他の可能な特徴を有するクロック・データ再生回路

集積回路(「IC」)は、入力データ信号からデータ情報を再生するためのクロック・データ再生(「CDR」)回路を含んでもよい。CDR回路は、参照クロックループと、データループとを含んでもよい。CDR回路によって出力される時刻変更(再生)データ信号は、その信号に含有される通信変更要求について、IC上の他の制御回路によって監視される。そのような要求に応答して、制御回路は、CDR回路の動作パラメータ(例えば、上述のループのうちのいずれか一方で使用される周波数分割ファクター)を変更することができる。これは、オートスピードネゴシエーションを採用するICサポート通信プロトコルに役立つことができる。  (もっと読む)

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

PLL発振回路

【課題】 アンロック状態を検査すると共に、自動的に再同期する自動リトライ機能を備えるPLL発振回路を提供する。

【解決手段】 MPU4は、外部基準信号とVCXO3からの出力信号の位相を比較してVCXO3への制御電圧を出力するPLL−IC1からのロック検出信号を入力し、ロック状態においてアンロック状態にするためのアンロックアラームテスト用データをPLL−IC1に設定し、PLL−IC1からのロック検出信号によりアンロック状態を判定すると、外部にアンロックアラーム出力信号を出力し、アンロック状態が第1の期間継続しているか否かを判定し、アンロック状態が第1の期間継続していれば、再同期を行わせるためのデータをPLL−IC1に設定するリトライを実行するPLL発振回路である。

(もっと読む)

位相同期発振装置

【課題】 小さいばらつきで電圧制御回路から供給される温度補償された電圧によって制御される電圧制御発振器を介して接続された増幅器の出力電力を、精度良く増減させ出力端子から出力する位相同期発振装置を得る。

【解決手段】 発振周波数を制御する周波数制御電圧入力端子と発振電力を制御する電圧入力端子とを有する電圧制御発振器と、この電圧制御発振器から出力される高周波信号を増幅して出力する温度特性を有する増幅器と、温度センサを有し、この温度センサの出力信号で基準電圧から変化する電圧を前記電圧制御発振器の電圧入力端子に入力し、前記電圧制御発振器を介して前記増幅器の電力非飽和領域の電力を増減する電圧制御回路とを備えている。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

スプレッドスペクトルクロック発生器及びそれを含む電子装置

【課題】新しい変調率及び変調周波数を有するスプレッドスペクトルクロック信号を生成することができるスプレッドスペクトルクロック発生器を提供する。

【解決手段】スプレッドスペクトルクロック発生器は、第1スプレッドスペクトルクロック信号を受信して第1スプレッドスペクトルクロック信号の平均周波数に対応する周波数信号を出力する発振回路と、周波数信号を受信して第2スプレッドスペクトルクロック信号を発生する位相固定ループと、第1及び第2スプレッドスペクトルクロック信号を受信して、第2スプレッドスペクトルクロック信号の平均周波数が第1スプレッドスペクトルクロック信号の平均周波数と近接するように位相固定ループを制御する制御回路を含む。このようなスプレッドスペクトルクロック発生器は、スプレッドスペクトルクロック信号を受信して、希望する変調率及び変調周波数を有する新しいスプレッドスペクトルクロック信号を発生する。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

位相同期ループのジッタ検出方法及び装置

【課題】別途のジッタ計測装備を使用せずとも位相同期ループのジッタ水準を検出できる位相同期ループのジッタ検出方法及び装置を得る。

【解決手段】基準クロックとフィードバッククロックとの位相差信号を検出し、その位相差信号によって一定の周波数の発振信号を生成する位相同期ループと、入力遅延制御信号によって多数のキャパシタをスイッチングし、前記位相同期ループからの前記位相差信号を前記遅延制御信号によって遅延させる可変位相遅延部と、前記位相同期ループからの前記位相差信号と前記可変位相遅延部によって遅延された位相差信号とを比較し、前記位相差信号の遅延期間を検出する比較部と、前記比較部から検出された遅延期間以後にロック範囲内に位置することを検出するロック検出部とを備える。

(もっと読む)

クロックデータリカバリ回路、表示装置用データ転送装置及び表示装置用データ転送方法

【課題】回路規模、消費電力が小さく、EMI特性に優れるクロックデータリカバリ回路の提供。

【解決手段】2倍オーバーサンプリングにより、入力データをサンプリングするサンプリング回路SCと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの周波数差を検出する周波数検出回路FDと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの位相差を検出する位相検出回路PDと、少なくとも位相検出回路PDにより検出された位相差に基づいて、サンプリング回路SCに対し、リカバリクロックを出力する電圧制御発振回路VCOと、入力データとして表示データを受信している間、周波数検出回路FDの動作を停止する周波数検出制御回路FDCと、を備えるクロックデータリカバリ回路。

(もっと読む)

PLL回路および通信装置

【課題】出力周波数を切り替えた際の追従性の悪化を抑止すること。

【解決手段】分周部2は、基準信号と出力信号との位相を同期させるための信号である帰還信号を所定の分周比に分周する。そして、位相比較部3は、出力信号を用いて基準信号および帰還信号の位相を比較することで、分周部2が分周した分周比の増減に追従して、出力信号を生成するための位相比較部出力のゲインが増減する。濾波部4は、位相比較部3によって生成されたアナログ信号を濾波する。出力信号発振部5は、濾波部4によって濾波されたアナログ信号に基づいて、出力信号を生成する。

(もっと読む)

クロックデータリカバリー回路およびその動作方法

【課題】回路規模および消費電力を削減すること。

【解決手段】クロックデータリカバリー回路3では、クロック発生器300のサンプリングクロックに応答してA/D変換器301がA/D変換し、順次生成の複数のデジタル出力信号はデータ補正部303に供給され、順次生成の複数の補正デジタル信号は位相比較器305に供給される。位相比較器305の出力はループフィルタ306を介してタイミング生成部304に供給され、複数の再サンプリングタイミングの情報Pvcoはデータ補正部303に供給される。検出回路302はアナログ入力信号の周期Tとサンプリングクロックの周期tの比T/tの誤差情報nvcoを生成して、タイミング生成部304は複数の遅延時間で複数の再サンプリングタイミングを生成して、データ補正部303は複数の補正率で複数の補正デジタル信号を生成する。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

スペクトラムアナライザおよびスペクトラム分析方法

【課題】フラクショナルスプリアスに起因するスペクトル波形の表示を阻止しつつ、迅速な測定を可能にする。

【解決手段】指定されたスパン(分析対象周波数範囲)の幅値が境界値より大きい場合、基準信号周波数を所定の基準値に設定し、RBW(分解能帯域幅)より狭いループフィルタ帯域を選択することによってフラクショナルスプリアスをRBWの内側にしてスペクトラム波形として表示されないようにする。また、指定されたスパンの幅値が境界値より小さい場合、基準信号周波数を基準値から所定値シフトさせ、そのシフト量と分周比の整数部との積に等しい分だけVCO出力信号の主信号成分とフラクショナルスプリアスとの周波数差を拡大させ、その拡大した周波数差より狭い範囲でループフィルタの帯域をRBWが含まれる領域に応じて設定してフラクショナルスプリアスのレベルを抑圧する。

(もっと読む)

161 - 180 / 881

[ Back to top ]