Fターム[5J106CC41]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | ループフィルタ (906)

Fターム[5J106CC41]の下位に属するFターム

複数のループフィルタ (25)

Fターム[5J106CC41]に分類される特許

201 - 220 / 881

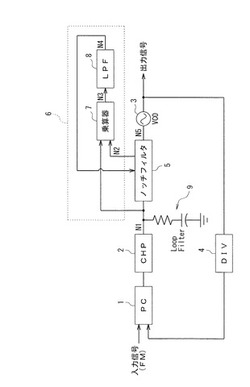

PLL回路

【課題】拡散周波数が未知の拡散信号から拡散周波数成分を除去できるPLL回路を提供する。

【解決手段】一の信号の位相と他の信号の位相との差分に応じた差分信号を出力する位相比較器1、差分信号に応じた電流信号を生成するチャージポンプ回路2、電流信号を平滑化して信号n1を生成するループフィルタ9、信号n1をフィルタリングして信号n2、n5を生成するノッチフィルタ5、信号n1の位相と信号n2の位相との差分に基づいて、ノッチフィルタ5によって遮断される遮断周波数を調整する遮断周波数調整回路6、信号n5に基づいて所定の周波数の信号を発振する電圧制御発振回路3によってPLL回路を構成する。ノッチフィルタ5は、ループフィルタ9によって遮断される周波数よりも低い周波数の範囲に上限値と下限値が含まれる所定の範囲の周波数を遮断する。

(もっと読む)

チャージポンプ回路及びそれを用いるPLL回路

【課題】電流供給および吸入用の定電流源と、それらの定電流源の間に設けられる2つの直列に接続されたスイッチ素子から成り第1の出力端子を持つ主出力側電流路と、同様に2つのスイッチ素子から成り第2の出力端子を持つ副出力側電流路とを備え、位相比較器からの駆動信号に応答して、主出力側電流路のスイッチと副出力側電流路との各スイッチ素子が開閉し、第1の出力端子から正負の電流パルスが出力される差動スイッチング方式のチャージポンプ回路において、ダイ面積を縮小するとともに、消費電力を削減する。

【解決手段】主出力側電流路のスイッチ素子Q7,Q8間の電位と副出力側電流路のスイッチ素子Q5,Q6間の電位との差に起因して定電流源Q3,Q4の寄生容量の充放電に伴い発生する緩慢なグリッチを補償するために、コンパレータ37と、ラッチ回路38と、コンデンサC1と、充放電器Q9,Q10とを用いてグリッチ補償回路36を構成する。

(もっと読む)

同期および追跡動作モードを有する位相同期ループシステム

【課題】同期モードと追跡動作モードを有する位相同期ループ(PLL)システム。

【解決手段】PLLは、所望の周波数で信号を出力する電圧制御発振器(VCO)を含む。位相検波器がVCOからの出力に結合されている。位相検波器は、VCOからの信号出力の位相を基準信号の位相と比較する。ループフィルタ601がVCOと位相検波器とに結合されている。ループフィルタ601はスイッチ603を含む。スイッチ603が垂直な位置に設定されるとき、VCO信号の位相を基準信号の位相に同期させるために、ループフィルタ601は同期動作モードとなる。スイッチ603を水平な位置に設定することにより、ループフィルタを追跡動作モードに置くことができ、追跡動作モードはVCO信号の位相を調整して、基準信号の位相を追跡する。

(もっと読む)

位相ロックループ回路

【課題】ローカルクロック信号に同期し、入力クロック信号に基づく周波数の出力クロック信号を出力することができる位相ロックループ回路を提供することを課題とする。

【解決手段】ローカルクロック信号及び第1のクロック信号の位相を比較する第1の位相比較器(107)と、第1の位相比較器により出力される信号の電圧に応じた周波数の出力クロック信号を出力する電圧制御発振器(109)と、電圧制御発振器により出力される出力クロック信号を分周し、その分周した出力クロック信号を第1のクロック信号として第1の位相比較器に出力する第1の分周器(110)と、入力クロック信号及び電圧制御発振器により出力される出力クロック信号の位相を比較する第2の位相比較器(111)と、第2の位相比較器により出力される信号に応じて第1の分周器の分周比を制御する制御部(112,113)とを有する位相ロックループ回路が提供される。

(もっと読む)

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

送受信装置およびその動作方法

【課題】半導体チップ面積を低減して再生データと再生クロックの生成の誤動作の可能性を軽減する。

【解決手段】送受信装置7は、クロックデータリカバリ回路11、デシリアライザ15、シリアライザ14、PLL回路13、周波数検出器12を具備する。クロックデータリカバリ回路11は受信信号RXとPLL回路13から生成されるクロック信号TXCLKに応答して、再生クロックCLKと再生データDATAを抽出する。デシリアライザ15はCLKとDATAからパラレル受信データDTを生成し、シリアライザ14はパラレル送信データDRとTXCLKからシリアル送信信号TXを生成する。検出器12は受信信号RXとクロック信号TXCLKの周波数の差を検出して周波数制御信号FCSを生成して、信号FCSに応答して周波数の記差を低減するように、PLL回路13はTXCLKの周期を制御する。

(もっと読む)

周波数シンセサイザ

【課題】 電源投入直後から長期にわたる使用期間全体で良好な周波数安定度が得られる周波数シンセサイザを提供する。

【解決手段】 基準信号発生回路1に、OCXO20と、TCXO30と、それぞれの出力に対してウェイト調整を行うウェイト変換器21,31と、各ウェイト変換器からの出力を加算して基準信号として出力する加算器41を備え、CPU10が、電源投入時にはTCXO30のウェイトを100%、OCXO20のウェイトを0%とし、徐々にOCXO20のウェイトを上げて、予め設定された一定時間後にTCXO30のウェイトを0%、OCXO20のウェイトを100%とするようにウェイト変換器B,Cを制御する周波数シンセサイザとしており、電源投入後に急速に周波数を安定させることができるものである。

(もっと読む)

スペクトラム拡散クロックジェネレータ、回路装置、画像読取装置、画像形成装置、及びスペクトラム拡散クロック生成方法

【課題】周波数変調幅を高精度に合わせることができるようにする。

【解決手段】入力クロックとフィードバッククロックとの位相差を検出する位相比較器2と、位相比較器2からの位相差信号に応じて電流を供給するチャージポンプ3と、チャージポンプ3の出力を電圧に変換し、平滑化するループフィルタ4と、入力電圧に応じた周波数のクロックを発生させる電圧制御発振器6と、変調幅設定値に応じた振幅を持つ変調信号を生成する変調生成部8とを有し、ループフィルタ4の出力と変調生成部8から出力される変調信号とを加算した信号を電圧制御発振器6に印加し、スペクトラム拡散クロックを生成する際、電圧制御発振器6で生成されたスペクトル拡散クロックの変調幅を検出し、検出した変調幅と変調幅目標値を比較し、その差分を小さくするように新たに算出した変調幅設定値を変調生成部8にフィードバックする変調幅検出部10を備えた。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

PLL回路

【課題】位相比較周波数を高く保ち、PLLの位相雑音を改善し、出力信号の精度を向上させたPLL回路を提供する。

【解決手段】基準信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した基準信号の位相に相当する信号を出力する第1位相アキュムレータ1、発振器の出力信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した発振器の出力信号の位相に相当する信号を出力する第2位相アキュムレータ2、第1及び第2位相アキュムレータの出力信号を比較して差を求め基準信号と発振器の出力信号との位相差を示す出力信号を出力する位相比較器3、位相比較器の出力信号に従って発振器への制御信号を生成する制御部4、制御部からの制御信号に応じた周波数の信号を出力する上記発振器5を有す。

(もっと読む)

抵抗値調整回路

【課題】LSI内部の抵抗素子の抵抗値を精度よく且つ適時に較正する。

【解決手段】

複数の抵抗素子を有する半導体集積回路に設けられる抵抗値調整回路は、前記複数の抵抗素子のうち第1の抵抗素子に基準電圧を印加して第1の抵抗素子の抵抗値に反比例する定電流を生成し、前記半導体集積回路の外部のコンデンサに前記定電流を供給する定電流源と、前記コンデンサに前記定電流が供給されるときに、前記コンデンサの電圧が所定電圧上昇する時間を計測する充電時間計測部と、予め設定された基準充電時間と前記計測された計測充電時間の差分に基づいて前記複数の抵抗素子のうち第2の抵抗素子の抵抗値を較正するキャリブレーション部を有する。LSI外部のコンデンサは容量が既知であり、LSIの製造プロセスのばらつきに依存しないので、基準充電時間と計測充電時間の差分に基づいて、精度よく抵抗値を較正できる。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、自走した時にも発振周波数を安定に保ち、更に外部からの固定電圧を可変にした制御電圧で発振できる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、PWM回路22と、メモリ21と、制御電圧可変回路26と、位相比較器12とループフィルタ14との接続をオン/オフすると共に制御電圧可変回路26からの制御電圧を選択出力する選択スイッチ13と、当該制御電圧選択の指示で当該制御電圧を優先的に選択出力し、当該指示がない場合に検波回路17で検出された外部基準信号のレベルが適正範囲内であれば選択スイッチ13をオンとし、レベルが適正範囲外であれば選択スイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する。

(もっと読む)

信号発生装置および試験装置

【課題】ループ帯域より高い周波数のジッタを印加する。

【解決手段】指定された位相の出力信号を発生する信号発生装置であって、所定周期の基準信号と出力信号との位相差に応じた制御信号を出力する位相差検出部と、制御信号の高域成分を除去するループフィルタと、ループフィルタにより高域成分が除去された制御信号に応じた周波数の周期信号を発生する発振部と、指定された位相分、周期信号に対して位相がシフトされた出力信号を出力する位相シフト部と、を備える信号発生装置を提供する。

(もっと読む)

復調器及び通信装置

【課題】受信信号と局部発振信号とに位相差があっても復調できるようにする。

【解決手段】復調器1は、変調器2で送信された受信信号D3をアンテナ11で受信し、この受信した受信信号D3をVCO13に注入して、自走発振周波数を有する局部発振信号D6を発振する。この発振した局部発振信号D6を90度移相器で90度移相する(局部発振信号D7になる)。アンテナ11で受信した受信信号D3の位相と90度移相器で90度移相した局部発振信号D7の位相とを位相比較器15で比較して、局部発振信号D6の位相を調整するための位相調整信号Vctを生成する。この生成した位相調整信号Vctに基づいて、受信信号D3と局部発振信号D6とをVCO13で同期させ、該同期させたものである局部発振信号D8をミキサ17に入力する。注入同期後の局部発振信号D8と受信信号D3とをミキサ17で演算して当該受信信号D3を復調する。

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

タイミング・モジュールのホールドオーバのための内蔵自己検査のシステム及び方法

【課題】本発明の実施例は、局所発振器を有する装置において使用される方法を含む。

【解決手段】方法は、外部レファレンス信号によって統制される局所発振器について外部レファレンス信号にロックされている間に、外部レファレンス信号の関数であり、発振器におけるドリフトを統制するために使用される関数である補正信号に少なくとも部分的に基づいて数学的モデル毎の予測補正信号を求めるよう発振器の少なくとも2つの数学的モデルを訓練する工程を含む。方法は更に、外部レファレンス信号が利用可能でなく、発振器におけるドリフトを統制するために別の補正信号を使用する場合に最小の時間誤差を少なくとも2つの数学的モデルのうちの数学的モデルも含む。方法は、訓練に使用される期間に加えた検査持続時間の必要なしに、選択された数学的モデルを使用することが可能であるように、補正信号のサンプリングされたバージョンを使用して、選択された数学的モデルを検査する工程を更に含む。

(もっと読む)

通信装置

【課題】飛翔体に搭載され衛星と通信を行う通信装置において、飛翔体からの送信信号の周波数がドップラー効果により大きく変動した場合であっても、送信信号を所定の規定周波数で衛星が受信できるようにする。

【解決手段】飛翔体に搭載され衛星20と通信を行う通信装置10であって、衛星20に対し送信信号を送信する送信部5と、衛星20に対する飛翔体の相対位置、姿勢、速度に基づいて、ドップラー効果による送信信号の周波数変動量を求める周波数変動量取得部14と、衛星20から見た送信信号の周波数が規定周波数となるように、周波数変動量に基づいて、送信信号の周波数を調整する送信信号調整部13と、を備える。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

位相同期回路

【課題】ノイズが混入した場合であっても、所望の周波数で発振信号を生成することが可能な位相同期回路を提供する。

【解決手段】位相同期回路は、低域通過フィルタからの出力電圧に応じて発振回路から出力される発振信号を、制御信号に基づいた利得で増幅する可変利得増幅回路と、可変利得増幅回路からの増幅信号の位相に応じた第1の位相と、増幅信号の基準となる基準信号の第2の位相とを比較して、第1の位相と第2の位相とを一致させるための比較信号を低域通過フィルタに出力する位相比較回路と、出力電圧に基づいて、第1の位相と第2の位相とが一致しているか否かを検出する検出回路と、検出回路の検出結果に基づいて、第1の位相と第2の位相とが一致している場合、利得が所定の値となるような制御信号を生成し、第1の位相と第2の位相とが一致していない場合、利得を所定の値より増加させるような制御信号を生成する制御信号生成回路と、を備える。

(もっと読む)

201 - 220 / 881

[ Back to top ]